# Simplifying Code Generation Through Peephole Optimizations

Jack W. Davidson

Computer Science Technical Report TR-87-07 May 1, 1987

|            |   | • |   |

|------------|---|---|---|

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            | • |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            | • |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   | * |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

| $\epsilon$ |   |   |   |

|            |   |   |   |

| •          |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

| •          |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

|            |   |   |   |

## Simplifying Code Generation Through Peephole Optimization\*

Jack W. Davidson

Department of Computer Science University of Virginia Charlottesville, VA 22903

#### **ABSTRACT**

Producing compilers that generate good object code is difficult. The early phase of the compiler, syntactical and lexical analysis, have been automated. The latter phases, code generation and optimization, are more difficult because of the wide range of machine architectures. This dissertation describes a technique for the rapid implementation of production-quality compilers through the use of a machine-independent retargetable peephole optimizer, PO. PO is retargeted by providing a description of the new machine.

PO simplifies many of the tasks associated with developing compilers. It simplifies code generation by eliminating most of the case-analysis typically necessary to produce good code. It simplifies the optimization phase by collecting several disparate optimizations and generalizing them as peephole optimizations. PO also demonstrates that traditional optimizations, such as register allocation, common subexpression elimination, and removal of unreachable code, may be done more thoroughly and completely when information about the target machine is available.

May 1, 1987

Department of Computer Science

The University of Virginia

Charlottesville, VA 22903

<sup>\*</sup>This work was supported by the National Science Foundation under Grant MCS-7802545.

| • |  |  |

|---|--|--|

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

# **Table of Contents**

| 1.  | Introduction                                         |     |

|-----|------------------------------------------------------|-----|

|     | 1.1 Previous Work                                    | ſ   |

|     | 1.1.1 Intermediate Language Approach                 |     |

|     | I.I.I.I BCPL                                         |     |

|     | 1.1.1.2 Pascal                                       |     |

|     | 1.1.1.3 MACRO SPITBOL                                |     |

|     | 1.1.2 Table-driven Approach                          |     |

|     | 1.1.2.1 Portable C Compiler                          |     |

|     | 1.1.2.2 Glanville's Work                             |     |

|     | 1.1.2.3 Ganapathi's Work                             | - 1 |

|     | 1.1.2.4 Production-Quality Compiler-Compiler Project |     |

|     | 1.1.2.5 Fraser's Work                                |     |

|     | 1.1.2.6 Donegan's Work                               |     |

|     | 1.1.2.7 Lamb's Work                                  |     |

|     | 1.2 Overview of this Research                        |     |

|     | 1.3 Guide to the Dissertation                        | \   |

|     | The Oute to the Dissertation                         | (   |

| 2.  | The Intermediate Language                            | ς   |

|     | 2.1 The Union Approach                               | Ç   |

|     | 2.2 The Intersection Approach                        | 10  |

|     | 2.3 Discussion                                       | 11  |

| 3,  | Machine Descriptions                                 |     |

|     | 3.1 Instruction-Set Processor                        | 17  |

|     | 3.2 Machine Descriptions                             | l d |

|     | 3.3 A Sample Machine Description                     | 15  |

|     | 3.4 Comparison with Other Work                       | 1.9 |

|     | 3.4.1 Glanville's Work                               | 18  |

|     | 3.4.2 Ganapathi's Work                               | 15  |

|     | 3.4.3 Cattell's Work                                 | FO  |

|     | 3.4.4 Comparison                                     | 10  |

| , . |                                                      |     |

| 4.  | The Code Expander                                    | 21  |

|     | 4.1 Form Rules                                       | 21  |

|     | 4.2 Valid Instruction Rule                           | 21  |

|     | 4.3 Label Rule                                       | 22  |

|     | 4.4 Side Effect Rule                                 | 22  |

|     | 4.5 Register Rules and Guidelines                    | 22  |

|     | 4.5.1 Register Allocation                            | 22  |

|     | 4.5.2 Machine Register Rule                          | 23  |

|     | 4.5.3 Annotation Guidelines                          | 23  |

|     | 4.5.4 Intermediate Result Guidelines                 | 2.5 |

| 5, | The Optimizer - PO                        | . 25 |

|----|-------------------------------------------|------|

|    | 5.1 Cacher                                | 25   |

|    | 5.1.1 The Algorithm                       | 25   |

|    | 5.1.2 Redundant Load Elimination          | 26   |

|    | 5.1.3 Common Subexpression Elimination    | 27   |

|    | 5.1.4 Dead-Variable Elimination           | 28   |

|    | 5.1.5 Window Definition                   | 28   |

|    | 5.1.6 Annotation                          |      |

|    | 5.1.7 Implementation                      |      |

| ٠, | 5.2 Combiner                              | 30   |

| •  | 5.2.1 Pairs                               | 30   |

|    | 5.2.2 Triples                             |      |

|    | 5.2.3 Labels                              |      |

|    | 5.2.4 Branches                            | 32   |

|    | 5.2.5 Branch Chains                       |      |

|    | 5.2.6 Simplifications                     |      |

|    | 5.2.7 Implementation                      |      |

|    | 5.3 Assigner                              | 35   |

|    | 5.3.1 Register Assignment                 |      |

|    | 5.3.2 Assembly                            | 36   |

|    | 5.3.3 Implementation                      | 37   |

|    | 5.4 Results                               | 37   |

| 6. | Results and Conclusions                   |      |

|    | 6.1 Comparison                            |      |

|    | 6.1.1 Code Quality                        | 39   |

|    | 6.1.2 Compiler Speed                      | 46   |

|    | 6.1.3 Machine Applicability               | 46   |

|    | 6.1.4 Implementation Effort               | 46   |

|    | 6.2 Areas for Further Research            | 46   |

|    | 6.3 Contributions                         | 47   |

|    | Appendix A: The Y Intermediate Language   | 49   |

|    | Appendix B: PDP-11 Machine Description    |      |

|    | Appendix C: DEC-10 Machine Description    | 57   |

|    | Appendix D: Cyber 175 Machine Description | 61   |

|    | Appendix E: 8080 Machine Description      | 63   |

|    | Appendix F: The Caching Algorithm         | 65   |

|    | Appendix G: Benchmark Programs            | 67   |

|    | List of References                        | 71   |

# **ACKNOWLEDGEMENTS**

The work described in this dissertation was supported by the National Science Foundation under Grant MCS-7802545.

I would like to thank the members of my committee, Chris Fraser, Ralph Griswold, and Dave Hanson for their support of this research. Special thanks go to Chris and Dave for their constant support and encouragement. My advisor, Chris, deserves special mention for all the time and effort he put into this work. No matter how busy he was, he always found time to discuss problems and solutions.

Finally, I would like to thank all my friends for their support, especially Audrey.

# Chapter 1

# Introduction

In the last few years there has been a great deal of research directed at automating compiler construction, particularly the code generation phase. There are several reasons for these efforts:

- 1. Because of advances in hardware design and construction, new machine architectures are being produced at a surprising rate. Unfortunately, compiler and software development has not progressed at the same rate.

- 2. Despite lower hardware costs and increased machine speeds, high-quality code is still desirable [Wulf81].

- 3. Advances in programming language design have led to large, complex languages that need the support of good compilers.

- 4. The early phases of compiler construction, lexical analysis and syntax analysis, have been successfully automated.

Automating code generation is difficult because there are many machines each with different characteristics. There are one-, two- and three-address machines, general-register machines, stack machines, array processors, and composites of these. Even among machines of the same architectural class there are major differences. Instruction sets differ, and each architecture has its own idiosyncrasies: certain registers have restricted uses, division must be done in even-odd register pairs, some instructions set condition codes while others do not, etc. This makes it difficult to decide which instructions to use to produce the best code. In the past, code generators used extensive case analysis to generate optimal code sequences. Such case analysis is ad hoc and difficult to validate.

The goal of this research has been development of a retargetable compiler for a high-level language that produces production-quality code. This has been achieved through a retargetable peephole optimizer [McKE65] that automates most of the case analysis typically performed by code generators. As a vehicle for testing and validating the ideas of this dissertation, a compiler for a high-level programming language has been developed that can be retargeted for a new machine with two to three days of effort.

# 1.1 Previous Work

There are several criteria for evaluating automatic code generation techniques and portable compilers. These are:

- 1. Speed

- 2. Quality of code

- 3. Machine applicability

- 4. Implementation cost

For the code generator to be practical, it must produce code at a reasonable rate. Few users will tolerate a slow compiler. Similarly, few users tolerate inefficient code. A technique that accommodates a wide variety of architectures is better than one that handles a restricted set. Similarly, the less effort to retarget the compiler the better.

The only way code generation techniques can be accurately evaluated is through extensive use. Of the work reviewed below, only the BCPL, Pascal, and the Portable C Compiler have been extensively tested.

It is surprising that although many code generation techniques are presented as being applicable to a wide range of architectures, usually only one or two machines are presented as evidence of this.

Previous work on producing retargetable compilers and code generation falls into two categories: intermediate language approaches and table-driven approaches.

### 1.1.1 Intermediate Language Approach

Some of the first successful work in developing portable software used intermediate languages. These works are based on an earlier effort called UNCOL [STRO58, STEE61], an acronym for UNiversal Computer Oriented Language. In the UNCOL approach, compilers emit machine-independent UNCOL, which is translated to machine-specific object code. To retarget the compiler for a new machine, the program that translates UNCOL to object code is rewritten. This project failed because it was too difficult to represent a wide variety of architectures and languages in a single intermediate language.

Closely related to the intermediate language approach is abstract machine modeling [Newe72]. An abstract machine along with a language that describes the basic operations and data types of the machine are developed. The language is often called an intermediate language. SIL, the SNOBOL4 Implementation Language [Gris72], is used to implement a portable version of SNOBOL4 [Gris71]. AIM1 [Newe72] and STAGE2 [WAIT73] were used to implement a BASIC [DART70] interpreter. Janus [HADD78] has been used to implement a set of machine-independent mathematical software.

Intermediate languages have also been used to develop retargetable compilers. The code generator of the compiler produces code for an abstract machine. This code is then translated to assembly language for the target machine, typically through macro expansion or a similar process called code expansion. BCPL and Pascal are two typical languages for which this approach proved successful.

# 1.1.1.1 BCPL

BCPL [RICH71, RICH77] is a relatively simple systems programming language that has one type, the binary bit pattern. The BCPL compiler translates BCPL to OCODE, the assembly language for the BCPL abstract machine. Because there is only one type, OCODE is relatively simple and has only 56 operation codes ('opcodes').

BCPL is moved to a new machine by rewriting the code expander that translates each OCODE statement into a sequence of assembly language instructions for the target machine. This produces an inefficient version of the compiler. More sophisticated code expanders that translate OCODE into assembly language can then be written in BCPL. These new expanders can perform optimizations to produce more efficient versions of the compiler.

It requires three to five months of effort to move BCPL to a new machine if the implementor has no previous knowledge of BCPL [Rich71]. Part of the difficulty is that several versions of the OCODE to assembly language translator had to be written before an efficient version of the compiler was produced. While OCODE is well suited to executing BCPL on an abstract machine, it is not suited to real machines. Nonetheless, BCPL is a successful portable compiler and has been transferred to over ten machines.

#### 1.1.1.2 Pascal

The Pascal-P compiler [Nor.181] is a retargetable compiler for a 'standard subset' of Pascal [Wir.175]. The compiler is written in the subset of Pascal it compiles. It emits object code for a hypothetical stack machine. The assembly language for the stack machine is called PCODE. To retarget the compiler for a new machine, the code expander must be rewritten. Pascal-P takes longer to retarget than BCPL. Six months [Berr.78] seems to be a realistic figure. This is probably due to Pascal having more types than BCPL which is reflected by the size of the abstract machine's instruction set. Pascal-P's PCODE has 125 opcodes (when types are included) as opposed to OCODE's 56.

There are several other retargetable Pascal compilers. These implementations are more complicated but capable of generating more efficient object code. One part of the compiler that is more complicated is

the intermediate language. So that it can be efficiently mapped to the target machines, special purpose opcodes have been added to the intermediate language [Nels79]. The UCSD Pascal compiler [Shill.78], PASCALJ [Hadd78], and the VU Pascal compiler [Tane80] are examples. To further increase the efficiency of the generated code, optimizers for the hypothetical stack machine's assembly language are often included as part of the distribution package [Perk79, Tane80].

#### 1.1.1.3 MACRO SPITBOL

While BCPL and Pascal achieve portability by compiling themselves and generating an intermediate language, MACRO SPITBOL [DewA77] takes a different approach. The compiler, the interpreter, and system routines are written in a machine-independent macro assembly language, called MINIMAL. The MACRO SPITBOL system is retargeted for a new machine by writing a translator that transforms MINIMAL statements to the target machine's assembly language.

Implementations of MACRO SPITBOL exist on a wide range of machines. The PDP-11, DEC-10, CDC Cyber series, and Burroughs B1700 are a few of the machines that have been accommodated. MACRO SPITBOL is unique in that the retargeted code can be faster than code that is tailored for the specific machine. Benchmarks of a MACRO SPITBOL implementation for the DEC-10 and SITBOL [GIMP73], a DEC-10 specific implementation of SNOBOL4, reveal that MACRO SPITBOL runs faster than SITBOL [GRIS77].

### 1.1.2 Table-driven Approach

Table-driven approaches to code generation modularize code generation by organizing code generation information in tabular form. The main differences in table-driven methods are how the tables are built and how the tables are used to generate code. This approach to code generation offers the same advantages as table-driven lexical and syntax analysis: ease of use, reliability, enhanced portability, and modularity.

### 1.1.2.1 Portable C Compiler

C [Kern78] is the systems programming language for the UNIX operating system [Ritc74]. The Portable C Compiler [John78] uses many of the ideas of a previous work by Snyder [Snyd74]. The goals of this work coincide with the goals of this research. These are to produce a portable compiler that is easily retargeted, produces good code, and is fast enough to be used as a production compiler.

The early phases of the compiler are mostly machine-independent and are implemented using many of the tools available with the UNIX operating system [John80]. To simplify code generation and show that it is correct, Johnson abstracts the relevant features of code generation into two models. The expression tree produced by the parser models the computation to be performed, while which registers are busy might be the model of the machine's state. Code generation is simplified to choosing the proper 'transformations' to perform on the expression tree to reduce it to a single node.

A transformation is a rewriting rule for the expression tree. Transformations are organized into templates that represent the change to the expression tree, the associated change to the machine state, and instructions that implement those changes. Templates are organized in a table so that transformations can be rapidly matched to expression trees. If the machine state and the expression tree are correct, and if the semantics of the transformation to the expression tree match the semantics of the instructions emitted, the generated code must be correct.

This code generation method is both practical and flexible. The compiler has been implemented on ver a dozen machines including the Honeywell 6000, IBM 370, and Interdata 8/32 [John 78]. It produces good code and is used as a production compiler.

The compiler is retargeted by writing templates for the new machine. Johnson reports no statistics on

how long it takes to retarget the compiler. Building new templates is an ad hoc process, and the quality of the code and the speed of the code generator depend on the design of the templates.

#### 1.1.2.2 Glanville's Work

One of the newer and more promising approaches to automatic code generation is due to Robert S. Glanville and Susan L. Graham [GLAN77, GLAN78, GRAH80]. Their technique involves a table-driven algorithm that translates a low-level intermediate representation of a program into assembly language for the target machine. The tables are constructed from a description of the target machine's instruction set.

Building the code generation tables is similar to building parse tables from a grammar. In fact, the theory of context-free parsing was used in developing the algorithm [AHO72]. As a result, the algorithm is fast and easily understood.

The code generator produces locally good code. In his dissertation, Glanville discusses code generators for two machines, the PDP-11 and the IBM 370. Although these machines are quite different, it is difficult to evaluate the ability of the algorithm to accommodate a wide variety of machines. Glanville expects to have difficulties with 'awkward' architectures such as the CDC Cyber series machines.

A more serious problem appears in the machine descriptions. Because context-free parsing techniques are used to construct the tables, it is necessary to describe each instruction with every addressing mode. For example, the PDP-11 has eight word-addressing modes. In some double-operand instructions every mode can be used in the source and destination. For a double-operand instruction such as mov there are 64 possible addressing mode combinations. This means that a full description of the PDP-11 must have 64 patterns to describe the mov instruction. Complete descriptions are large and tedious to write.

### 1.1.2.3 Ganapathi's Work

Ganapathi's work [Gana80] is similar to Glanville's. While Glanville uses LR grammars, Ganapathi uses attribute grammars [Knur68]. The attributes are used to pass code generation information up the tree. This added information can be used to generate better code and perform machine-dependent optimizations.

Ganapathi produced code generators for the PDP-11 and the VAX-11/780. These machines are so similar that it is impossible to evaluate the ability of the technique to accommodate various architectures. The machine descriptions are very long and hard to understand. Ganapathi's PDP-11 description is seven pages long, whereas Glanville's is only three pages. Similarly, Ganapathi's VAX-11/780 description is 11 pages long.

Ganapathi uses the attributes to perform many machine-dependent optimizations. These optimizations are hand-coded into the semantic actions of the machine description. Consequently, the quality of the code is somewhat better than that of the methods reviewed thus far.

# 1.1.2.4 Production-Quality Compiler-Compiler Project

The Production-Quality Compiler-Compiler (PQCC) project [Leve80] is somewhat more ambitious than the previously mentioned works. PQCC's goal is to automate all phases of compiler construction. The practical result would be a truly automatic compiler generation system. The project has focused on two areas of compiler writing: code optimization and code generation. Of main interest here is the work on code generation.

Code selection in the PQCC project is performed by the code generator generator developed by Cattell [CATT78, CATT79, CATT80]. Code generation is similar to the technique used in Johnson's Portable C Compiler. Templates are matched against a tree representing the program. The work differs from Johnson's in that templates are generated automatically from a machine description.

Templates are generated using heuristic search methods borrowed from artificial intelligence [ERNS69]. The heuristics cannot guarantee that the best instruction sequences will be found, or that any sequence

will be found at all, but as a practical matter, the heuristics seem to be quite effective. Code generation is extremely fast; Cattell reports producing 2000 instructions per second on a DEC-10.

Many code generation issues are not dealt with by Cattell's code generator. Such issues as register allocation, register assignment, temporary assignment, and storage assignment are dealt with by other phases of the compiler. This spreads machine-dependent information throughout the compiler. Work is in progress by the PQCC group to build generators that derive this machine-dependent information from machine descriptions [Leve 80].

#### 1.1.2.5 Fraser's Work

Fraser [Fras77] describes a code generator generator whose organization is similar to Cattell's. Both methods use machine descriptions to generate templates. Fraser's approach differs from Cattell's in the manner of template generation.

Cattell's approach is to formalize code selection, while Fraser uses human programming knowledge to aid code selection. Each approach has strengths and weaknesses. Cattell [CATT78] notes that possibly the best approach would be a combination of formal methods along with human-knowledge information to aid code selection when formal methods fail. Fraser implemented a experimental version of his code generator generator and code generator. The method produced locally good code but was very slow.

### 1.1.2.6 Donegan's Work

Donegan [Done79] describes a language for writing code generators called CGGL (pronounced sca-gull). It extends his earlier work in this area [Done73]. This approach has elements of both table-driven and intermediate language approaches. The compiler produces an intermediate language that is translated to machine code by a code expander. The code expander is constructed from a CGGL program that describes the semantics of each intermediate language opcode for the target machine.

A finite-state automation that models code generation is constructed from a CGGL program. For instance, data movement is expressed as finite-state machine transitions. Optimal code generation involves finding the minimal path from the start state to the goal state for each intermediate language opcode.

The code expander is realized by converting the finite-state automaton into a Pascal program for generating code. Currently CGGL only handles simple architectures. Attempts to model more complex machines, such as the CDC Cyber series, result in an explosion of the number of states in the finite state automaton. Donegan makes no statements about the speed of the code generators produced from CGGL programs or how long it takes to produce a code generator.

#### 1.1.2.7 Lamb's Work

Lamb [Lamb81] describes a set of tools that aid the construction of peephole optimizers. A peephole optimizer replaces poor code sequences in the object code with better ones. For example, one common peephole optimization is the replacement of pairs of instructions with a singleton that has the same effect. Lamb uses a pattern language to describe poor code sequences and their replacements. The language resembles assembly language with the capability to specify arbitrary patterns and conditions necessary for the replacement to occur. These patterns are converted by a translator to subroutines in the implementation language, BLISS-10 [WULF71]. The subroutines are called by a set of specialized patternmatching routines. The optimizer is retargeted by writing patterns for the new machine.

Writing patterns is an ad hoc process. Unoptimized generated code is scanned for poor code agments. Patterns that should be included may be omitted if they do not appear in the scanned code samples. A more critical problem is that the person who writes the patterns must ensure that patterns match only when appropriate. Failure to do so can produce incorrect code. Currently an optimizer for one machine, the VAX-11/780, has been implemented. Statistics for this machine show the optimizer to

be reasonably fast. As more machines are accommodated, the technique's flexibility will become easier to evaluate.

#### 1.2 Overview of this Research

This work contains elements of both the intermediate language and table-driven approaches. It differs, however, radically in its approach to achieving its goal of production-quality code. Most of the approaches described above use the traditional model of compilation consisting of five phases [Aho80]:

- lexical analysis

- syntax analysis

- semantic analysis

- code optimization

- code generation

Typically, the code optimization phase attempts to transform an intermediate representation of the source program into one that is faster, or smaller, or both. Code generation translates the optimized intermediate representation into target-machine code.

This research modifies the model of compilation by reversing the last two phases: code optimization and code generation. This has several effects. Code generation is simplified to a naive translation of the source-language program to machine code. The code optimization phase transforms the naive machine code produced by the code generator to production-quality machine code.

Code optimization is also simplified. All optimizations performed consist of peephole optimizations on a machine-dependent representation of the program. This research shows that many optimizations typically performed at a higher level are subsumed by a few machine-independent peephole optimizations. In addition, machine-level optimizations are shown to be more thorough than their high-level counterparts.

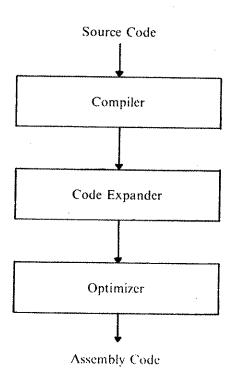

A block diagram of the organization of the compiler appears in Figure 1. The first phase of the compiler is machine-independent and produces intermediate code for an abstract machine. The second phase, called the code expander (back end), translates the intermediate language to target machine code. It is machine specific and must be rewritten for each new machine. The last phase optimizes the machine code and outputs assembly language. The optimizer, called PO, extends earlier work by Fraser [FRAS 79]. PO combines instructions by symbolically simulating pairs and using a machine description to verify that the result is valid. PO is retargeted by writing a new machine description. The compiler has been retargeted by the author for several machines in as few as three days. The compiler produces code that is as good as or better than all of the previously mentioned methods except PQCC.

# 1.3 Guide to the Dissertation

This dissertation is organized in much the same way as the compiler. Chapter 2 describes the intermediate language produced by the compiler. Chapter 3 introduces the register transfer notation used to describe instructions and explains how machines are described. Chapter 4 describes the phase of the compiler that translates the intermediate language to code for the target machine. Chapter 5, the bulk of the dissertation, describes the retargetable peephole optimizer, PO. Chapter 6 reviews the results of this work and outlines areas for future research.

Figure 1. Compiler Organization

|   |   |   |   |   | • | , |

|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |

|   |   |   |   | ٠ |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   | • |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   | * |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   | • |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   | , |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

| • |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   | • |   |   |   | • |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |

# Chapter 2

# The Intermediate Language

Machine-independence in the compiler is achieved through abstract machine modeling [Korn80, Newe72]. The abstract machine is designed to support the y programming language [Hans81], but it is sufficiently general so it could be used to implement compilers for other languages such as C, Pascal, or Ada [ICHB79] with minor modifications.

The abstract machine interprets a simple postfix code. There are no general registers, and all operations are performed on the operands on the stack. It supports three types: integer, real, and character, and arrays of these types. There are three addressing modes: local, global, and parameter. Scalar parameters are passed by value. Arrays are passed by reference. Addresses are treated as a special type, and there is a set of operations for address calculations. Other mechanisms, such as passing arrays by value, can be built upon this foundation.

### 2.1 The Union Approach

Conventional abstract machines might be called 'union' machines because their instruction sets are collections of features from the target machines needed to support the target language. For example, if any target machine has three-address operations, and if it is desired that the generated code use them when possible, these three-address operations would be included in the instruction set of the abstract machine. This is necessary because it is difficult to exploit three-address target machine instructions when the abstract machine has only two-address instructions. As with most software design processes, trade-offs are made between convenience and efficiency. The result is an abstract machine that closely parallels the real machines in terms of data types, addressing modes, and types of instructions. The intermediate language is large, but it can effectively use the instruction sets of most target machines.

There are several problems with this technique. Intermediate languages that are developed using this approach tend to be unwieldy. Many machines have special-case instructions that are more efficient than their general counterparts. To make effective use of the target machine's instruction set, these instructions are often included in the intermediate language. This makes the intermediate language large, and consequently the code expander is also large.

Another problem with the union approach, which is shared with many compilers, is that the code generation phase is complicated. In order to generate code to use the abstract machine's special case instructions, the code generator or code expander must do extensive case analysis. In order to emit a clear instruction instead of the more general store instruction, for example, the code generator or expander must check if the value being stored is zero.

A third problem with the union approach is that inefficient code is produced. For example, many machines have a condition-code register that is set to reflect the result of the last operation. Few abstract machines have explicit operations on the condition-code register, making it difficult for the compiler or expander to take advantage of the condition code being set by a previous operation. For example the code fragment,

$$i = j$$

if (i == 0)

might be translated to the following intermediate code

```

store j,i store j in i

cmpne i,0,11 jump to label 11 if i is nonzero

...

llab 11 define label 11

```

This code might be translated by an expander into the following PDP-11 assembly language.

```

mov j,i move value of j to i

cmp i,#0 compare i to 0

bne I1 jump to label I1 if not equal

...

```

11:

Comparing the value i to zero is unnecessary, since the condition code register is set when j is stored in i. Such situations are typically remedied by peephole optimizers [WULF75].

Finally, a fourth problem with the union approach is the difficulty of adding new machines with new features to the set of target machines. To do so may require redesigning the abstract machine so that code generators can take advantage of the new features. For example, the VAX-11/780 has instructions for manipulating queues. Several years ago such operations were rarely included in machine instruction sets. To exploit new operations, the abstract machine must be modified to include them. Because it is difficult to predict new machine features, union abstract machines are unstable.

# 2.2 The Intersection Approach

An alternate approach to abstract machine design is to include only the most general source-language operations required to support the language. This method might be called the 'intersection' approach. While the union approach is motivated by the source language and target machines, the intersection approach is motivated mainly by the source language.

For example, many machines have 'clear memory' instructions, but they are not included in an intersection machine's instruction repertoire. This is because there is a general way to clear a memory location—load a zero and then store it. Similarly, the abstract machine has add and subtract instructions, but not increment and decrement instructions. Consequently, intersection abstract machines have smaller instruction sets than union machines. In general, intersection intermediate languages provide only one way to generate code for any source language operation.

The generated code for the two kinds of abstract machines for the code fragment

$$i = i - 1$$

is shown below.

| Union Machine        |        |                                                              |                               | Intersection Machine                                                                                   |  |  |

|----------------------|--------|--------------------------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------|--|--|

| pushi<br>dec<br>popi | i<br>i | push value of i<br>decrement i<br>store value back<br>into i | pushla i<br>pushla i<br>pushi | push local address of i<br>push local address of i<br>load an integer using<br>address on top of stack |  |  |

|                      | or     |                                                              | pushic 1<br>subi<br>popi      | push a constant 1<br>subtract two integers<br>store integer on top of stack in                         |  |  |

| dec                  | i      |                                                              |                               | location pointed to by stack - 1                                                                       |  |  |

Constructing an abstract machine using the intersection approach has several beneficial effects. Because the intermediate language is small, the expander is small, simplifying its implementation:

The absence of special-case instructions simplifies the code generation phase of the compiler. In the

example above, the union machine requires the code generator to check the operands of the subtract operation so it can emit a decrement instruction. Intersection machines do not require such case analysis.

The only detrimental effect of the intersection method is the poor quality of the generated code. If each line of abstract-machine code in the above example is translated to one line of target-machine assembly code, the union machine produces one or three instructions, the intersection machine, six. Both code fragments need peephole optimization, but the intersection example needs extensive optimization just to reduce its size to that of the union example. This optimization, however, is shown in Chapter 5 to be manageable.

### 2.3 Discussion

The abstract machine used in this research is an intersection machine. It has 99 opcodes. In contrast, EM-1, the union intermediate language for the VU Pascal compiler, has 219 opcodes [Tane80]. A complete list of the abstract machine instructions along with a description of their operations appears in Appendix A.

The abstract machine designed for y supports a broad range of machine architectures. Cross-compilers that use the abstract machine exist for the PDP-II, DEC-I0, the CDC CYBER series computers, and Intel's 8080 microprocessor.

Certain architectures seem better suited to the Y abstract machine than others. Byte-addressable machines with stacks are particularly easy to accommodate. The abstract machine is more difficult to map onto machines with no registers or with irregular register sets such as the Intel's 8080 or the MOS Technology's 6502, but such machines can be accommodated.

To illustrate the ease of generating code using the y intermediate language, two examples of source code along with the intermediate code produced by the compiler are shown below.

# code generated for a = b \* c + 1

| pushla | а | push address of local variable a                                  |

|--------|---|-------------------------------------------------------------------|

| pushla | b | push address of local variable b                                  |

| pushi  |   | load an integer using address on top of stack                     |

| pushla | С | push address of local variable c                                  |

| pushi  |   | load an integer using address on top of stack                     |

| muli   |   | multiply two integers                                             |

| pushic | 1 | push a constant 1                                                 |

| addi   |   | add two integers                                                  |

| popi   |   | store integer on top of stack in location pointed to by stack - I |

|        |   |                                                                   |

### code generated for if (j) i = in[j]

```

pushla

push address of local variable j

pushi

get value of j

push constant 0

pushic

compare and jump to label 11 if equal

cmple

push address of local variable i

pushla

push address of local variable j

pushla

get value of i

pushi

push address of local variable in

pushla

in

convert in and index j to an address where in's element size is 2

index

.2

-2

add offset of -2 to address

adda

pushi

get array value

store value from top of stack into i

popi

llab

11

```

|  |   |       | • |   |

|--|---|-------|---|---|

|  |   |       |   |   |

|  |   |       |   | ~ |

|  |   |       |   |   |

|  |   |       |   |   |

|  |   | South |   |   |

|  |   |       |   |   |

|  |   |       |   |   |

|  |   |       |   |   |

|  |   |       |   |   |

|  | • |       |   |   |

|  |   |       |   |   |

|  |   |       |   |   |

|  |   |       |   |   |

|  |   |       |   |   |

|  |   |       |   |   |

|  |   | *     |   |   |

|  |   |       |   |   |

|  |   |       |   |   |

|  |   |       |   |   |

|  |   |       |   |   |

|  |   |       |   |   |

|  |   |       |   |   |

|  |   |       |   | , |

|  |   |       |   |   |

|  |   |       |   |   |

|  |   |       |   |   |

|  |   |       |   |   |

|  |   |       |   |   |

|  |   |       |   |   |

|  |   |       |   |   |

|  |   |       |   |   |

# Chapter 3

# **Machine Descriptions**

PO is retargeted for a new machine by providing a new machine description. A machine description describes the syntax and effects of each target machine instruction. From the machine description, a recognizer and transducer are automatically constructed. PO uses the recognizer to check that a register transfer represents a valid target machine instruction. It uses the transducer to translate the internal representation of instructions into the target machine's assembly language.

#### 3.1 Instruction-Set Processor

The effects of instructions are described using ISP-like notation [Bill. 71]. For instance, the PDP-10 instruction

add 3,loc

is expressed in ISP as

$$r[3] - r[3] + m[loc];$$

which indicates that the contents of memory location loc is added to register 3. The register transfer

$$PC \leftarrow if r[3] > m[loc] then PC+1 else PC;$$

represents the DEC-10 instruction

camg 3,loc

The instruction skips the next location if the contents of register 3 exceeds the contents of memory location loc. PC denotes the program counter, and is the only name that has special meaning to PO. The program counter is assumed to be incremented automatically, so this effect need not be made explicit.

Many machine instructions have multiple effects. Such instructions may contain several register transfers. For example, the DEC-10 instruction

aoje 5,L1

is expressed in ISP as

$$r[5] - r[5] + 1$$

; PC - if  $r[5] + 1 = 0$  then L1 else PC;

The first register transfer specifies that register 5 is incremented; the second specifies that if the result is zero a jump is made to label L1, otherwise execution continues with the next instruction. The '+ 1' is needed in the second register transfer because all register transfers are done in parallel.

Details irrelevant to the machine description may be omitted. For example, the PDP-11 instruction

· tst r1

is expressed as

The actual implementation syntax differs slightly.

$$NZ - r[1] ? 0;$$

where NZ represents the condition-code register. The contents of register I are compared to zero and the condition code is set accordingly. Code generators do not need to know how the condition code represents the result of comparisons, so the semantics of the '?' operator need not be specified. The DEC-10 ibp instruction, which increments a byte pointer, performs several complicated operations. Various fields in the byte pointer are manipulated, based on the size of the byte. Such detail is irrelevant to PO, which need know only that a memory location is being modified in the same way other byte pointer instructions manipulate them. Thus,

ibp loc

is expressed as

m[loc] - ibp(m[loc]);

which specifies that the byte pointer at memory location loc is incremented. Similarly, the 'load byte' instruction

idb 3,loc

is expressed as

r[3] - Idb(m[loc])

From the ISP for these two instructions, it is easy to see how the ildb instruction (increment and load byte) should be expressed. Composing the register transfers yields

$r[3] \leftarrow ldb(ibp(m[loc]))$

which describes the instruction ildb 3,loc

# 3.2 Machine Descriptions

A machine description is a grammar for syntax-directed translation between ISP register transfers and the machine's assembly language. Because PO is retargeted for a new machine by rewriting the machine description, machine descriptions have been kept simple to write. Typically, a machine description takes about a day to write by someone familiar with the target machine.

Awkward machine features can be disguised by the machine description. Many microprocessors have addressing modes that can only reach nearby words. These addressing modes are valuable because they are faster and take less space than their general counterparts. Assemblers often offer pseudo-instructions so the user does not have to decide which addressing variant is appropriate. Machine descriptions can do the same thing by allowing all addressing modes to any address. The machine description or the assembler can translate them to the appropriate addressing mode depending on the distance of the instruction to the source or destination. Similarly, many microprocessors have conditional branches that can only reach nearby locations. The machine description can disguise this feature by allowing conditional branches to arbitrary targets and let the assembler translate them to two-instruction sequences as necessary.

The machine description need not include every instruction in the machine's instruction set. Instructions that PO has little chance of replacing (e.g. subroutine jump instructions, block moves, and I/O instructions) may be omitted. Instructions that are never generated may also be omitted. Experience, however, has shown that it is difficult to predict the transformations PO will make on the generated code. PO can do its best job when it knows all instructions except those it has little chance of replacing.

A machine description is divided logically into two parts. The first part describes the machine's addressing modes, and the second part describes the instructions. This division provides a natural way to describe machines. The addressing modes are described without regard for the instructions that use them. The machine operations and the addressing modes are combined to describe the machine's instruction set.

Structuring machine descriptions in this way produces concise, understandable machine descriptions. Machine descriptions usually comprise two to four pages.

In this work, the recognizer and transducer are realized by transforming the machine description into a grammar for Lex [Lesx 79], a lexical-analyzer generator. From its input, Lex generates subroutines that implement the recognizer and transducer. Because Lex recognizes only regular expressions, the machine must be described using regular expressions. Most machines, however, have context sensitive components in their instructions. For instance the DEC-10, add instruction can be described as

$$RG - RG + M$$

;

where RG denotes a register and M denotes a memory location. When a nonterminal appears twice in a production, the strings matched by the patterns must be identical. In the above example, both instances of RG must match the same string.

At times it is necessary to override the context sensitivity checking performed by the recognizer. This can be done by defining several instances of the same pattern each with a different name. For example, the description of the CDC Cyber instruction for moving one X register to another is

$$x[RN1] \leftarrow x[RN2];$$

Although RN1 and RN2 (register numbers) represent the same pattern, they need not match identical strings.

# 3.3 A Sample Machine Description

Portions of the machine description for the PDP-11 are given below. Following each part of the description is a explanation of the description. To minimize detail, only a portion of the machine description is given.

This part of the description defines regular expressions used throughout the description of the addressing modes. The first definition describes a register number: a sequence of one or more digits between 0 and 7, i.e. an octal number. The second definition describes a component of an identifier: an underscore or a capital L followed by one or more letters, digits, or underscores, or a number preceded by an optional negative sign. IDENT defines an identifier: an XDENT followed by zero or more occurrences of the operators + or - followed by a XDENT. The last definition is for a label: a capital L followed by a sequence of one or more L's or digits. A description of the addressing modes follows.

```

REG

:=

r[RN]

rRN

LB

LABEL

LABEL

-

$0

ID

IDENT

$IDENT

:===

WORD

:==

m[IDENT]

¹===

IDENT

*===

m[r[RN] + IDENT]

:---

IDENT(rRN)

<u>*</u>==

m[r[RN]++]

<u>:----</u>

(rRN)+

----

m[--r[RN]]

;=

-(rRN)

:<u>---</u>

m[r[RN]]

:=

(rRN)

****

m[m[r[RN]++]]

;==

*(rRN)+

---

m[m[--r[RN]]]

:==

*-(rRN)

:---

m[m[r[RN] + IDENT]]

<u>;</u>=

*IDENT(rRN)

:==

m[m[IDENT]]

:=

*IDENT

m[m[r[RN]]]

:=

*(rRN)

REL

*****

:==

eq

:==

!==

:==

ne

:=

.....

ge

:=

:==

le

:=

<

·

lt

:==

gt

SO

;===

```

Each line of the definition has three fields: the token returned by the recognizer if the register transfer pattern is matched, the ISP syntax for the pattern, and the assembler syntax for the pattern. For instance, the first line defines a register: r followed by the register number in brackets. The corresponding assembler syntax is r followed by the register number. When a register is recognized, the token RG is returned.

If the first field is empty, the token returned is the string matched, as shown in the third line of the address definitions. In this case, a 0 is returned when a 0 is recognized. The assembler syntax field is also optional, as illustrated by the definition of SO, the shift operator. There is no corresponding assembler syntax so the field is omitted.

In the addressing modes definition, it is necessary to distinquish between a 0, a 1, and an ID. The pattern for ID can be written so that it does not match a 0 or a 1, but that complicates the pattern. To make things easier, the Lex rules for resolving ambiguous expressions are used.

- 1. The longest match is preferred.

- 2. Among rules that match the same number of characters, the rule given first is preferred.

Because the rules for 0 and 1 appear first, their tokens are returned instead of the token ID. Similarly, rule 1 ensures that the token SO is returned when the characters << are encountered instead of two occurrences of REL.

The final part of the address definitions groups the previously described tokens and single characters into classes:

```

RG1 := RG

RG2 := RG

DSTW := REG | WORD

SRCW := REG | ID | WORD | 0 | 1

```

RG1 and RG2 are two instances of registers. DSTW is a register or a word, and SRCW is a register, an identifier, a word, a 0, or a 1. Only tokens and single characters can appear on the right-hand side of these definitions. These groupings allow concise definition of instructions by combining similar addressing modes and operators into single groups.

The syntax for instruction definition is

```

instruction expression := instruction definition

```

An instruction definition is:

where brackets indicate an optional field and | separate alternatives. Ellipses (...) indicate indefinite repetition of items. Italicized words are nonterminals defined in the following paragraphs:

An instruction expression is the ISP representation of the instruction. Action's are executed if their associated test condition is true. Test conditions are evaluated in the order they appear. A series of test conditions can be thought of as an else-if chain or a case expression. If a test condition is omitted, the associated action is always executed.

The simplest type of instruction definition is one that has no test conditions and only one action. The action is the assembly language to output if the instruction expression is matched. An instruction expression matches the input string if it performs all register transfers requested, and the rest of its register transfers perform harmless functions. An example is the description of the PDP-11 compare instruction, cmp.

```

NZ - DSTW ? SRCW: := cmp DSTW,SRCW

```

Within test conditions it is possible to reference substrings of the input string that matched components of the instruction expression. For instance, the following machine description fragment describes the PDP-II instructions as and ash.

```

RG — RG SO SRCW;NZ — RG SO SRCW ? 0; := {

!strcmp(SRCW, "-1"): asr RG

ash SRCW,RG

```

In this example, the test condition allows one *instruction expression* to identify two instructions. If the shift count is -1, then the asr instruction is matched, otherwise the more general ash instruction is matched.

Test conditions may call system-supplied and user-supplied procedures. An example is stromp, which is used above to compare two strings; it returns true if they are equal, and false otherwise. The definition of the multiply instruction, mul, uses several different user-supplied routines:

```

RG - RG * SRCW;NZ - RG * SRCW ? 0; := {

lodd(RG) || !ispwr2(SRCW): ABORT

!strcmp(SRCW, "2"): asl RG

pwr2(SRCW): ash SRCW,RG

mul SRCW,RG

```

Odd returns true if its argument is an odd-numbered register -- 16-bit multiplication on the PDP-11 must be

done in an odd-numbered register. Ispwr2 returns true if its argument is a power of two. Pwr2 returns true if its argument is a power of two, and as a side effect converts its argument to the log of itself. It is used to determine whether the faster shift operation can be used instead of a multiply.

The special action ABORT indicates that although the input matched the instruction expression, it cannot possibly be a valid instruction, and that the recognition process should be terminated immediately. An ABORT action must be the first action in an instruction definition, as shown in the description of the multiply instruction. For example, 16-bit multiplication must be performed in an odd-numbered register, but if the multiplier is a power of two, it can be performed by a shift operation in any register. If neither of these two conditions is met, the input is not a valid instruction and is rejected.

Machine descriptions are converted to input suitable for Lex by a machine description processor written in SNOBOL4 [GRIS71]. Using regular expressions to describe machine instructions and Lex to construct a recognizer and transducer is one successful approach to the problem of recognizing legal instructions. A previous implementation [Davi80] used SNOBOL4 patterns and pattern matching to recognize legal instructions. It was much too slow for production use. The speed of the optimizer hinges on the recognition and translation process. Developing new notations for describing machine instruction sets and concomitant methods for recognizing machine instructions is an area of further research.

### 3.4 Comparison with Other Work

Several of the works discussed in Chapter I use machine descriptions to achieve machine independence. Since each method depends heavily on the descriptions, it is worthwhile to compare and contrast the various description methods. The PDP-II add instruction is used as a basis of comparison.

#### 3.4.1 Glanville's Work

Glanville's description of the add instruction is:

```

"add

r.1

::= (+ r.1 r.2)

r.2,r.1";

:= (+ k.1 r.1)

"add

$k.1,r.1";

r.1

r. 1

::= (+ + k.1 r.1)

"add

*k.1,r.1";

:= (:= k.1 + t k.1 r.1)

"add

r.1,*k.1";

r.2

:= (+ + + k.1 r.1 r.2)

"add

k.1(r.1),r.2";

::= (:= + k.1 r.1 + t + k.1 r.1 r.2)

λ

"add

r.2,k.1(r.1)";

λ

::= (:= + k.1 r.1 + t + k.1 r.1 t + k.2 r.2)

"add

k.2(r.2),k.1(r.1)";

"add

λ

::= (:= + k.1 r.1 + k.2 + k.1 r.1)

$k.2,k.1(r.1)";

```

r.1 and r.2 represent registers; k.1 and k.2 represent constants. 1 is a unary operator that retrieves the value of the memory location addressed by its operand. The assembly language instruction to output if the production matches the input appears to the right of the production.

#### 3.4.2 Ganapathi's Work

Ganapathi's description of the add instruction is:

```

Wordt -- + Wordta Wordtr Istemp(ir) EMIT (l'add' la Ir)

-- + Wordta Wordtb GETTEMP(l'word' tr)

EMIT (l'mov' ib Ir)

EMIT (l'add' la Ir)

```

I denotes a synthetic attribute that passes information up the parse tree. I denotes an inherited attribute, and it passes information down the parse tree. The variables a, b, and r are attribute variables. Word represents the word-addressing modes available on the PDP-11. Istemp is a disambiguating predicate that determines whether the current production can apply. Istemp is passed the attributes of the destination of the addition and verifies that it can be destroyed by the addition. GETTMP allocates a temporary, and EMIT outputs the assembly language instruction if the production matches the input.

#### 3.4.3 Cattell's Work

Cattell's description of the add instruction is:

```

(; (- $1:DST (+ $1:DST $2:SRC)) (- %N (LSS (+ $1:DST $2:SRC) 0))

(- %Z (EQL (+ $1:DST $2:SRC) 0))

```

DST and SRC represent the word-addressing modes available on the PDP-11. They are described in a separate part of the description.

#### 3.4.4 Comparison

The description used in this research is:

```

DSTW - DSTW + SRCW;NZ - DSTW + SRCW ? 0; := add SRCW,DSTW

```

DSTW and SRCW represent the word-addressing modes available on the PDP-11. NZ represents the condition code register. The assembly language instruction to output if the instruction expression matches the input follows the ':='.

This description is somewhat easier to read than the others because it uses infix notation instead of prefix. Ganapathi's description requires that the user implement the disambiguating predicates and actions for each machine. While this gives this method flexibility in performing machine-dependent optimizations, it complicates writing descriptions.

Glanville's description is substantially longer than the others because the addressing modes have not been factored out of the instruction definition.

Both Glanville's and Ganapathi's descriptions are incomplete in that the setting of the condition code is not described. In Glanville's case, this means that code cannot be generated that performs an addition solely for the side effect of setting the condition code. Ganapathi has a separate mechanism that scans for instructions that are only used to set the condition code. If it sets the condition code exactly as the preceding instruction, the instruction is suppressed. Since his description of the add instruction does not specify that the instruction sets the condition code, this information must come from some other source.

The description method used in this research provides a simple, yet robust method of describing machine instructions. Uninteresting details of the machine architecture can be suppressed, while complicated but necessary details can easily be described. Machine descriptions for the PDP-11, PDP-10, CDC Cyber series machines, and the 8080 appear in Appendices B, C, D, and E, respectively.

| - |

|---|

|   |

|   |

|   |

|   |

|   |

|   |

|   |

|   |

|   |

|   |

|   |

|   |

|   |

|   |

| • |

|   |

|   |

|   |

|   |

|   |

# Chapter 4

# The Code Expander

The code expander translates the intermediate language produced by the code generator into register transfer lists ('RTLs') for the target machine. Because the code expander must be rewritten to retarget the compiler for a new machine, it has been kept very simple. Nevertheless, it still translates the intermediate language into RTLs in a way that supports the final goal—production-quality code.

The remainder of this chapter describes rules and guidelines that have been adopted to simplify the code expander and provide input to PO that results in high-quality code. A rule must be rigorously observed. Failure to observe a rule can result in generation of erroneous code. Guidelines are suggestions and hints from an experienced user. They can be ignored, but code quality may suffer.

#### 4.1 Form Rules

The expander produces a series of records as output, some of which can be ignored by PO. Each record has four fields: a sequence number, a label, a RTL, and a dead-variable list. All but the first of these fields may be empty.

The sequence number is a unique integer that PO uses to construct pointers into the list of RTLs. Labels should have a consistent format so that they can be easily identified. PO uses the RTL and the dead-variable list to dynamically discover the effects of instructions. The dead-variable list contains variables and registers whose contents are no longer valid, or of no further interest.

The expander can emit code that is ignored by PO by marking the record with a special tag. Debugging code is an example: code that logs statement numbers, posts routine names, and outputs diagnostic information. If PO deleted, rearranged, or modified such code, the user could be confused by the unexpected absence, rearrangement, or modification of the expected output.

It is sometimes difficult to describe a machine operation using the ISP notation. These can be expressed in assembly language and tagged so that PO ignores them. Other information, such as assembler pseudo-operations used to declare variables, allocate space, and define constants are of no use to PO and can be tagged.

### 4.2 Valid Instruction Rule

The code expander translates each abstract machine opcode into one or more valid RTLs for the target machine. A valid RTL represents a legal instruction from the machine description. If the expander emits an invalid RTL, the phase of PO that translates RTLs into assembly language reports an error.

#### 4.3 Label Rule

The code expander identifies labels introduced during code expansion to ensure that incorrect optimizations are not made. Code expanders for machines with 'skip' instructions also produce code expansion labels for the implicit target of the skip. The section on labels in Chapter 5 explains the effects labels have on the various phases of optimization.

#### 4.4 Side Effect Rule

The code expander identifies all side effects caused by the expanded code. If all side effects of the generated code are not identified, missing information causes PO to make erroneous changes to the program.

If an instruction causes the contents of a register to be destroyed, the code expander must pass this information to PO. For instance, on the DEC-10 the bit instruction (block transfer) destroys the contents of the register used to hold the source and destination addresses. On some CDC machines, the integer divide instruction is actually a macro that uses certain registers as scratch locations. Subroutine calls often have side effects that must be indicated. Depending on the calling sequence, the contents of certain registers may be destroyed by subroutine calls. The expander places such registers on the dead-variable list so that PO knows their contents are invalid.

#### 4.5 Register Rules and Guidelines

#### 4.5.1 Register Allocation

The code expander maps the abstract machine onto the target machine. For stack architectures, the mapping is straightforward. For general-register architectures, the mapping is more difficult because the abstract machine is stack oriented. Conventional code expanders are complicated by allocation of the target machine's registers. They must decide which values should be in registers and what to do if the available machine registers are exhausted. They also must maintain the status of the real machine registers and temporary locations—which ones are in use and what they contain.

The policy adopted in the expanders used with PO solves all of the problems above. All values are initially loaded into registers. This, however, would quickly exhaust the supply of registers. Consequently, expanders assume that there are as many registers as needed. Each time a new register is needed, one is generated. Once PO has reduced the number of registers needed and determined which values should remain in registers, a later pass, described in Chapter 5, maps the pseudo-registers onto the set of real machine registers.

All bookkeeping involving registers and temporary locations traditionally done by expanders is eliminated. Mapping the abstract stack machine to a register machine requires simply simulating the stack in the infinite supply of registers.

The following is a fragment of y code, the intermediate code emitted by the y compiler, and the RTLs emitted by the DEC-10 expander.

```

j = i — pushla j — r[16] - r[15] + j;

pushla i — r[17] - r[15] + i;

pushl — r[18] - m[r[17]];

popi — m[r[16]] - r[18];

```

Pseudo-registers are numbered starting after the highest numbered register of the target machine. This allows the code expander to use the target machine's registers if necessary. In the above example, register 15 is the target machine register that serves as the pointer to local variables. The stack is simulated in pseudo-registers 16, 17, 18, etc.

### 4.5.2 Machine Register Rule

A machine's hardware registers may be used in generating code (e.g. register 15 in the example above). Before a hardware register is loaded, it must be placed on the previous dead-variable list. This ensures that PO does not rearrange the generated code so that the use of a hardware register is moved past a subsequent load. This is unnecessary for pseudo-registers if the intermediate result guideline below is followed:

#### 4.5.3 Annotation Guidelines

PO eliminates redundant loads by tracking values that are loaded into registers, and when possible, reusing a value in a register instead of reloading it. Depending on the target machine, there may be values for which it is better to keep the load instruction. For example, on the CDC Cyber series machines, zero need not be retained in a register, since register B0 is always zero. These values, of course, depend on the particular target machine. Determining this set of values is left to the expander. For instance, on the DEC-10 it is better to not allocate a register to a constant that is eighteen bits or smaller since these are accessed inexpensively via 'immediate' mode operations, such as addi and movei. On the PDP-11, sixteen-bit constants can be accessed by indexing off the program counter via immediate mode addressing. In this case, it is less expensive to keep a constant that is used several times in a register and save the memory references, but this consumes scarce registers. For the PDP-11 expander used in this research, RTLs that load integer constants are annotated. Registers are saved for values that are expensive to load or compute.

Loads that should *not* be deleted are annotated. Annotation is a simple marking of the RTL. Using annotation only affects the quality of generated code; omitting annotation does not affect the correctness of the code. Experience indicates that annotation is more important on some machines than on others. For example, the code on the PDP-11 suffers considerably if annotation is not used, while code on the DEC-10 is still quite good, because the DEC-10 has more registers.

### 4.5.4 Intermediate Result Guidelines

Often a value that is loaded into a register is destroyed by an operation that uses that value. This is true on many two-address machines. For instance, on the DEC-10 the add instruction destroys one of the instruction's operands. If that value is used later, it must be reloaded. Expanders can determine which values can be destroyed only by looking ahead in the instruction stream. To avoid this complication and still produce good code, all values and intermediate results are preserved. Later phases of optimization determine which values can be destroyed. A small example clarifies this guideline. Again there is a y code fragment, the intermediate code emitted by the y compiler, and the RTLs generated by the PDP-11 expander.

```

j=i+1 — pushla j — r[8]-r[5]; r[8]-r[8]+j; pushla i — r[9]-r[5]; r[9]-r[9]+i; pushi — r[10]-m[r[9]]; pushic 1 — r[11]-1; addi — r[12]-r[10]; r[12]-r[12]+r[11]; popi — m[r[8]]-r[12];

```

Register 5 is the frame pointer. The RTLs of interest are those generated for addi. On the PDP-11, an add instruction destroys one of the operands. If that value is subsequently used it has to be reloaded. To avoid this, the expander emits two transfers. The first one saves i in a new register. The second performs the addition in the new register. If there are subsequent uses of i, it is already in a register, and the redundant

loads can be deleted. On the other hand, if there are no subsequent uses of i, the transfer of the contents of pseudo-register 10 to pseudo-register 12 is unnecessary and will be deleted by PO.

This guideline is irrelevant for three-address machines, since instructions operate on values without destroying them. If this guideline is not followed for two-address machines, code quality suffers; it may contain unnecessary loads.

Writing an expander is an ad hoc process. For traditional expanders, the quality of the final code depends on the ingenuity and expertise of the person writing the code expander. This is much less true for expanders written for use with PO. PO corrects inefficiencies, turning poor code into good code. Generally, it takes a day or so to implement an expander using the techniques described above. For example, the author implemented a code expander for the CDC Cyber series machines in five hours.

# Chapter 5

# The Optimizer - PO

There are two types of conventional peephole optimization. One type tracks values held in registers and tries to reuse their values whenever possible. The other combines logically adjacent instructions, replacing several instructions with one. PO performs both these optimizations in a machine-independent way. The part of PO that tracks values is called Cacher; the part that combines instructions is called Combiner. These two programs along with a third called Assigner, which assigns registers and translates RTLs to assembly language; form PO. The names Combiner and Assigner are derived from their functions, while the name Cacher suggests its implementation.

#### 5.1 Cacher

Cacher eliminates redundant loads. In addition, it eliminates common subexpressions within a block of code bounded by labels, identifies dead variables, and defines the size of the peephole for Combiner.

Cacher extends the work of Freiburghouse [Frei74] and Gries [Grie71]. The algorithm is similar to Freiburghouse's, but it is simpler and more thorough. It is simpler because it is just peephole optimization. It is more thorough because it detects and eliminates redundant computations missed by Freiburghouse's algorithm.

### 5.1.1 The Algorithm

Cacher reads a 'block' of code at a time, processes it, and then emits the simplified code. A block is a section of code bounded by labels. It builds sets of symbolic expressions (c-exprs) it has encountered as it scans the input. Formally, these sets form equivalence classes based on the following equivalence relation.

Let R be the set of all symbolic intermediate results produced by the bounded block. Let  $a,b \in R$ . Then the equivalence relation  $a \approx b$  is true at a given point in the block if and only if the block sets values so that a and b have the same value at that point.

For example, after the register transfers

$$r[1] - m[a]$$

$r[1] - r[1] + m[b]$

$r[1] \approx m[a] + m[b].$

Two relations are defined on the elements of R. Let  $e, f, g, h \in R$ . Let  $>_t$  be an order relation where  $e >_t f$  means that e was produced first in the code sequence, i.e. e is older than f. Let  $<_c$  be an order relation where  $g <_c h$  means that g is cheaper than h. Usually cheaper means faster, i.e. g is a faster reference to the machine's store than h. For instance, register references are the fastest references to a register machine's store. To optimize a program for size instead of speed, cheaper would mean smaller.

As Cacher scans the input, it partitions the c-exprs produced by the block into equivalence classes. As new c-exprs are read, Cacher searches the equivalence class for a set whose members are equivalent to the new c-expr. If one is found, Cacher substitutes the cheapest member of the set for the c-expr, eliminating a redundant load. The intermediate result guideline of Chapter 4 ensures that c-exprs previously loaded or computed are not destroyed and are available for reuse.

The input to Cacher is a list of RTLs. Each register transfer of each RTL is split into its destination and source. These are referred to as dst and src. If a RTL contains more than one register transfer, the operations outlined below are performed on each pair of dsts and srcs. This initial presentation of the algorithm ignores dead-variable analysis, redundant computation elimination, annotation, and window definition. A formal presentation of the complete algorithm appears in Appendix F.