# On the Implementation of Local Synchrony

Raymond R. Wagner, Jr.

UVA Computer Science Technical Report TR-93-33

June 1993

# On the Implementation of Local Synchrony

Raymond R. Wagner, Jr.

# <u>Abstract</u>

Local synchrony is a distributed approach to providing logically synchronous capabilities in an asynchronous system. Local synchrony provides a logical timeline to memory access, and thus a total ordering to the steps of a distributed computation, without many of the inherent consequences of global synchronization. Local synchrony offers a framework for the implementation of various concurrency control mechanisms, including combining and isochrons (parallel operations). We show the implementability of local synchrony, and demonstrate its compatibility with existing protocols for fault-tolerance in general purpose multiprocessors. The results of our research are threefold. We show first that practical implementation of local synchrony is feasible in general, asynchronous, MIMD architectures. We show that such implementations are compatible with existing hardware fault tolerance systems and present a correct rollback algorithm for our general implementation. Finally, we present both analytic and empirical studies which illustrate the performance characteristics of such implementations. Our analytic modeling technique extends in novel ways probabilistic modelling methods often employed for interconnection networks. Our work establishes the practicality and feasibility of local synchrony as a means of providing support for concurrency control.

© Copyright 1993 by Raymond R. Wagner, Jr.

# Table of Contents

| 1.0 | Intro      | duction                                                                                           | 1  |  |

|-----|------------|---------------------------------------------------------------------------------------------------|----|--|

| 2.0 | Background |                                                                                                   |    |  |

|     | 2.1        | MIMD Architectures                                                                                | 7  |  |

|     | 2.2        | Routing, Message Transfer, and Deadlock                                                           | 9  |  |

|     | 2.3        | Combining                                                                                         | 12 |  |

|     | 2.4        | An Approach to Concurrency Control                                                                |    |  |

|     | 2.5        | Isochrons                                                                                         |    |  |

|     | 2.6        | Local Synchrony                                                                                   |    |  |

|     | 2.7        | Schemes Related to Isochrons and Local Synchrony                                                  |    |  |

|     | 2.8        | An Implementation of Local Synchrony                                                              |    |  |

|     | 2.9        | Fault Tolerance                                                                                   |    |  |

|     | 2.10       | Performance Issues                                                                                |    |  |

| •   |            |                                                                                                   |    |  |

| 3.0 |            | Preliminaries                                                                                     |    |  |

|     | 3.1        | An Alternative to Locking                                                                         |    |  |

|     |            | 3.1.1 Local Synchrony vs. Locking                                                                 |    |  |

|     | 3.2        | An Implementation of Local Synchrony                                                              |    |  |

|     |            | <ul><li>3.2.1 Implementation Plan</li><li>3.2.2 Deadlock freedom</li></ul>                        |    |  |

|     | 3.3        | A Local Synchrony Switch Design                                                                   |    |  |

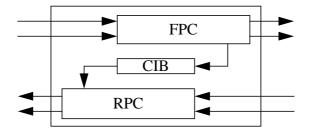

|     | 5.5        | 3.3.1 Architecture Overview                                                                       |    |  |

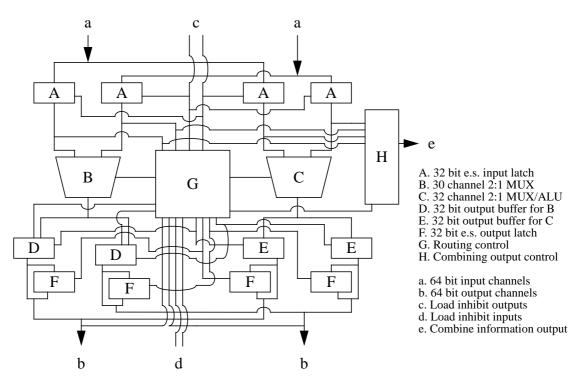

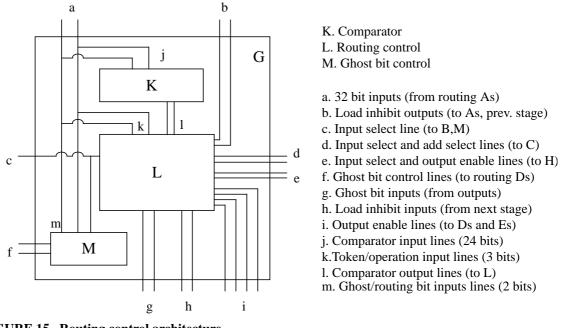

|     |            | 3.3.2 Forward Path Component Design                                                               |    |  |

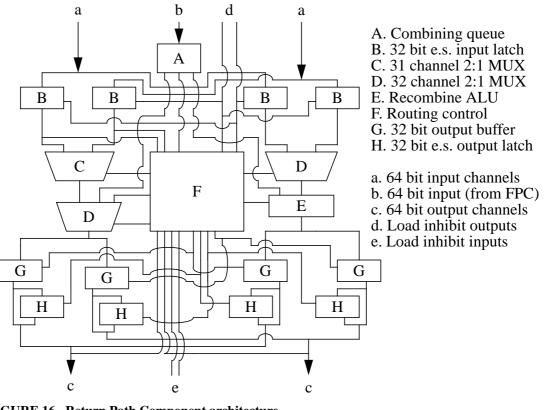

|     |            | 3.3.3 Return Path Component Design                                                                |    |  |

|     |            | 3.3.4 Combining System                                                                            |    |  |

|     |            | 3.3.5 Packaging                                                                                   |    |  |

|     |            | 3.3.6 Design Extensions                                                                           |    |  |

|     | 3.4        | Minimum Requirements for Deadlock Freedom                                                         | 79 |  |

|     | 3.5        | Summary                                                                                           | 84 |  |

| 4.0 | A Ge       |                                                                                                   |    |  |

|     | 4.1        | Correctness of a Local Synchrony Implementation                                                   | 87 |  |

|     | 4.2        | Approaches to Local Synchrony Implementation                                                      |    |  |

|     |            | 4.2.1 The Time Propagate Approach                                                                 |    |  |

|     |            | 4.2.2 The Time Increment Approach                                                                 |    |  |

|     | 4.3        | LS Graphs                                                                                         |    |  |

|     | 4.4        | Local Synchrony Implementation on LS Architectures                                                |    |  |

|     | 4.5        | Correctness of LS Architecture Implementations                                                    |    |  |

|     |            | 4.5.1 Correctness of Order of Consumption                                                         |    |  |

|     |            | 4.5.2 Deadlock Freedom                                                                            |    |  |

|     | 1.6        | 4.5.3 Termination                                                                                 |    |  |

|     | 4.6        | Mapping LS Architectures onto Candidate Architectures                                             |    |  |

|     | 4.7        | Examples of Local Synchrony Implementations                                                       |    |  |

|     |            | <ul><li>4.7.1 Implementation on a Torus</li><li>4.7.2 Implementation on a Binary 3-Cube</li></ul> |    |  |

|     |            | 4.7.2       Implementation on a Binary 5-Cube         4.7.3       Implementation on a Crossbar    |    |  |

|     | 4.8        | Operation of Virtual Switching Elements                                                           |    |  |

|     | 4.9        | Memory Requirements for Implementation                                                            |    |  |

|     | т.Э        | memory requirements for imprementation                                                            |    |  |

|     | 4.10                   | Summary                                                 |        |

|-----|------------------------|---------------------------------------------------------|--------|

| 5.0 | Fault-Tolerance Issues |                                                         |        |

|     | 5.1                    | The Preservation of System State in the Presence of Fau | lts120 |

|     | 5.2                    | A Single-Level Fault-Tolerance System                   |        |

|     | 5.3                    | A Rollback Algorithm for Local Synchrony                |        |

|     | 5.4                    | Checkpoint Validation                                   |        |

|     | 5.5                    | Summary                                                 |        |

|     |                        | 2                                                       |        |

| 6.0 | Perfo                  |                                                         |        |

|     | 6.1                    | Architectures Modeled                                   |        |

|     |                        | 6.1.1 Conventional network C1                           |        |

|     |                        | 6.1.2 Conventional network C2                           |        |

|     |                        | 6.1.3 Local synchrony network I1                        |        |

|     |                        | 6.1.4 Local synchrony network I2                        | 141    |

|     | 6.2                    | Analytical Models                                       |        |

|     |                        | 6.2.1 A Probabilistic Model for Switch I1               |        |

|     |                        | 6.2.2 Extending the Model to Local Synchrony            |        |

|     |                        | 6.2.3 Locally Synchronous Timestamp Comparison .        |        |

|     |                        | 6.2.4 Information Flow                                  |        |

|     |                        | 6.2.5 Representation of Tokens                          |        |

|     |                        | 6.2.6 A Representative Model                            |        |

|     |                        | 6.2.7 Models for Switch I2                              |        |

|     | 6.3                    | Simulation Data                                         |        |

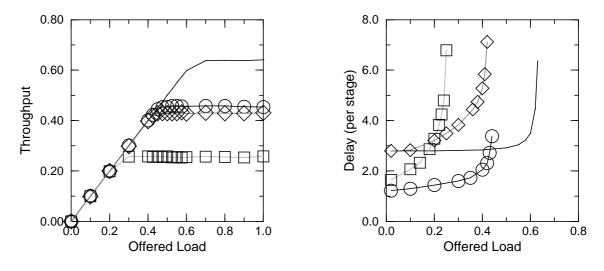

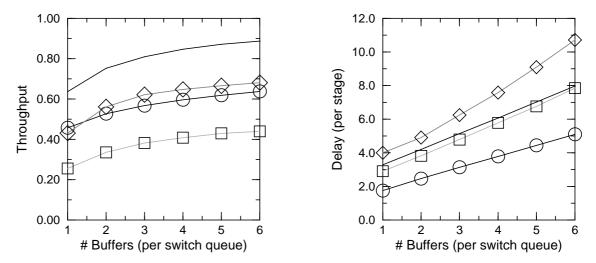

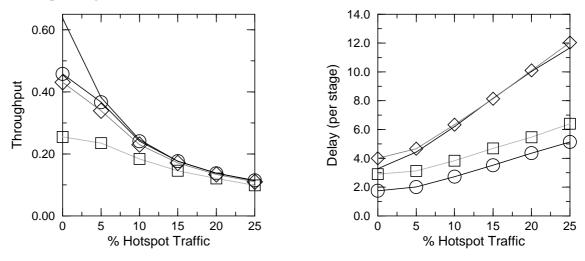

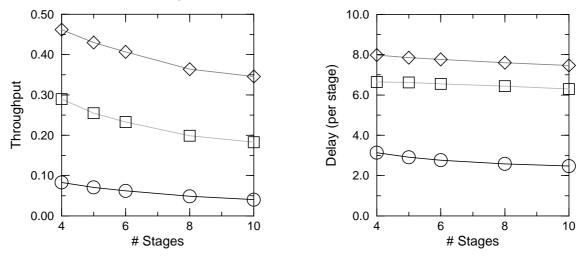

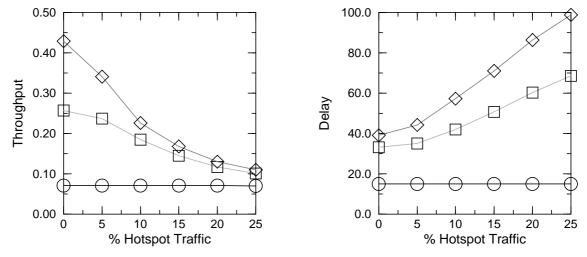

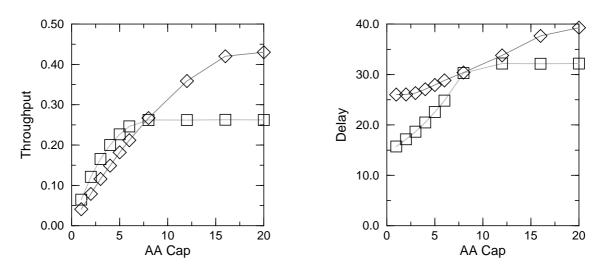

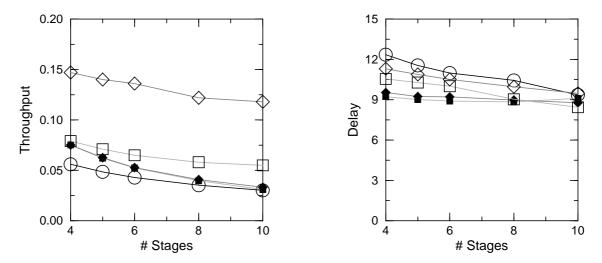

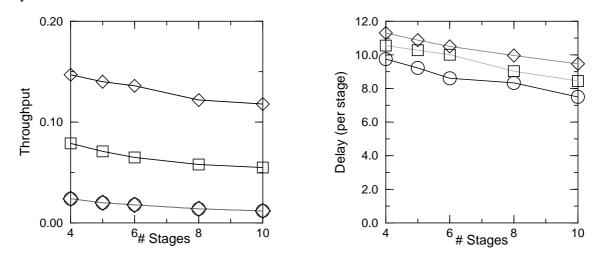

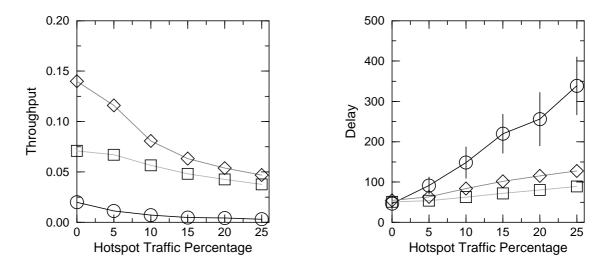

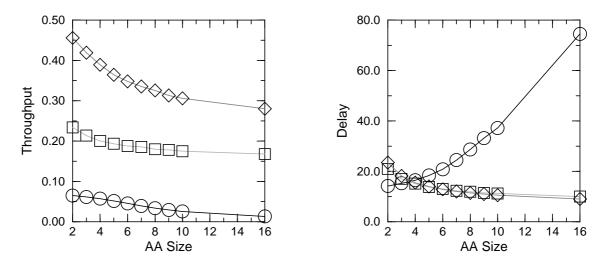

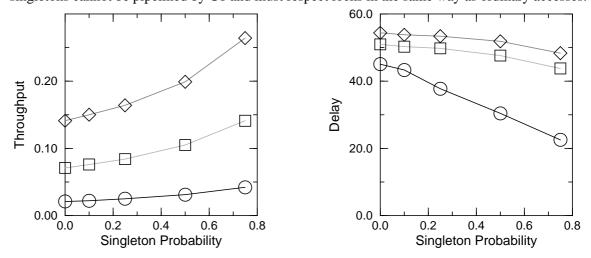

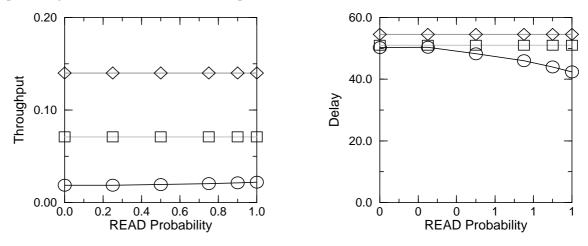

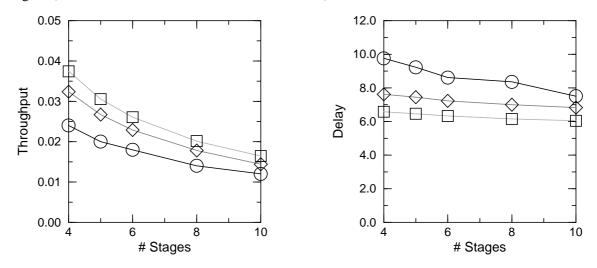

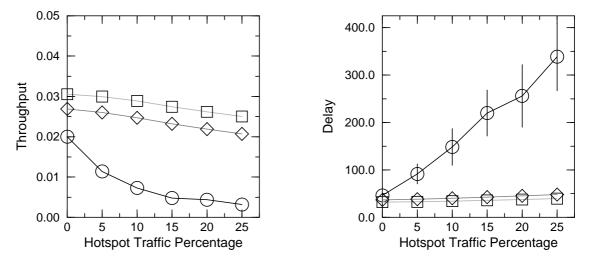

|     |                        | 6.3.1 Raw Power Data                                    |        |

|     |                        | 6.3.2 Sequential Consistency Only Data                  |        |

|     |                        | 6.3.3 Atomicity Only Data                               |        |

|     |                        | 6.3.4 Flat Atomic Action Data                           |        |

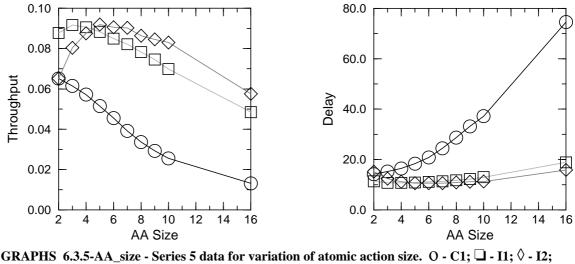

|     |                        | 6.3.5 Data Dependency Data                              |        |

|     |                        | 6.3.6 Warm Traffic Data                                 |        |

|     |                        | 6.3.7 Conclusions from the Simulation Study             |        |

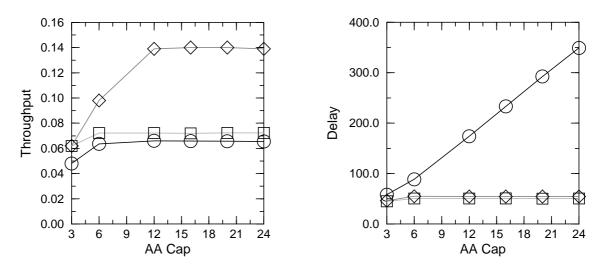

|     | 6.4                    | Alternate Implementations - Sorting at the MM           |        |

|     |                        | 6.4.1 Simulation Results for MM Sorting                 |        |

|     | 6.5                    | Summary                                                 |        |

| 7.0 | Conclusions            |                                                         |        |

|     | 7.1                    | Research Review                                         |        |

|     | 7.2                    | Future Work                                             |        |

# **1.0 Introduction**

A major focus of research in parallel processing is global memory: where to situate it, how to access it, and how to maintain its coherence. An important emphasis in any parallel architecture design is the speed with which processing elements in the system may access global memory. To a large extent, the speedups in processing power to be gained by using multiple processors to attack a single problem are directly related to memory cycle time. The longer memory cycle times of parallel processing architectures place severe limits on the processing speedups that can be achieved by utilizing the concurrency of such machines.

Much attention has been focused on improving memory access speed in both shared-memory and message-passing architectures. The proposals made by researchers in this field generally ask "In what ways can we shorten the cycle time of a single memory access in a multiprocessor system?" Their solutions include speeding up the transfer of a message through a given system by implementing better routing algorithms, and/or distributing memory in ways that reduce slowdowns caused by message traffic bottlenecks. Other work has proposed introducing multiprocessor cache memories [YYF85] [DSB88] [BNR89] [RAK89] and distributing memory [BaJ88], or balancing the message load [ReT86] to limit contention.

Another approach would be to ask: "Can we achieve better system utilization by increasing the amount of productive activity during global memory references, and reducing the amount of inter-process synchronization required?" Combining systems [GGK83] [GLR83] [Pfi85] [RBJ88] [TuR88], which reduce actual memory traffic by merging accesses to the same global variable, take this approach.

A method along these same lines would be to limit non-productive global memory references, thus freeing up system resources that could then be used for productive activity. Concurrency control requirements can generate a significant amount of the global memory traffic in a parallel computation. Concurrency control traffic only indirectly performs useful work, by facilitating (in a way that meets the synchronization requirements) the execution of later productive accesses. When multiple entities (i.e., processes) are competing for the use of multiple resources (i.e., global variables), extreme care must be taken to enforce proper accessing principles. Concurrency control principles guarantee that the result of the parallel computation will be equivalent to some possible sequential execution. Our work seeks to limit or eliminate non-productive global memory accesses by building into the system architecture the concurrency control requirements necessary for correct parallel execution.

In [RWW89], we addressed the problem of parallel atomic access to global memory. A system that provides atomic access to multiple global memory locations eliminates much of the inter-process synchronization currently necessary in parallel programming. To provide such atomic access, we must enforce a specific ordering of distributed events. In asynchronous systems it is generally impossible to order events at different locations by their physical occurrence [Lam79]. However, if events are arbitrarily ordered and executed such that all sequencing (atomic-ity and sequential consistency) constraints are met in the same way at all locations, the effect will be as if all events occurred with the correct synchronization in force.

In order to implement parallel memory access operations, or isochrons, Williams [Wil93] proposed a system of logical clocks, which provide a logical ordering of global memory accesses, in turn facilitating the synchronization necessary to guarantee atomicity and sequential consistency of parallel memory accesses. This system of logical clocks describes a logical timestamp ordering system for the global memory accesses of a parallel computation.

One method of implementation for this system of logical clocks is by:

- 1. Assigning a unique logical timestamp to each global memory access. The logical timestamps are designed to provide a total ordering of global memory accesses meeting all sequencing constraints.

- 2. Constraining all elements within the system to process global memory accesses in logical timestamp order. Thus accesses are emitted from the processes in order, kept ordered as they traverse the network, and executed in order when they reach global memory.

We call this method *local synchrony*. We are interested in this conservative logical times-

tamp ordering system for several reasons: it can be implemented using only local decision-making

by elements within the system; the timestamping system can be implemented implicitly, so an access need not be significantly larger than already necessary for conventional routing; and the system does not require elements to reach physical barriers in order to achieve synchronization.

Consider a shared memory architecture consisting of a number of processing elements (PEs) connected to a number of memory modules (MMs) by an interconnection network of switching elements. PEs communicate only by sending accesses to global memory. In a local synchrony implementation, each PE assigns a unique identifier to each access. The identifier acts as a timestamp for the access' execution at the MM. PEs release accesses in ascending order by timestamp. Switching elements merge incoming streams of sorted accesses to keep all access streams in timestamp order. MMs execute accesses in timestamp order. Nodes (PEs, MMs, switching elements) stay in loose synchronization because they must process accesses in order, which means that they must have input from each neighbor in order to make processing decisions. This is local synchrony.

An example of a local synchrony implementation is an isotach network [RWW89] [WiR91]. Such an implementation provides hardware support for the task of controlling the concurrency of parallel computations—in particular, in enforcing atomicity and sequential consistency.

Atomicity and sequential consistency are important properties of parallel computations that are expensive to enforce using existing techniques. The atomic action is a group of one or more operations issued by the same process that *appears* to be executed indivisibly, without interleaving with other operations.

Atomic actions are typically specified by operations on locks or semaphores or by critical sections or monitors implemented with locks or semaphores. Existing hardware support for atomic actions is designed to make locking more efficient. The principle drawback to the use of locks in implementing atomicity is the unnecessarily restricted access to shared variables implied by lock-ing. Variables cannot in general be partitioned so that each atomic action can, by acquiring a single

lock, control all the variables it must access and no others. Atomic actions either acquire a single lock, and lock some variables unnecessarily, or acquire multiple locks. To avoid deadlock, an atomic action that requires multiple locks must typically obtain the locks sequentially. During this lock acquisition phase, the variables controlled by already-acquired locks are unavailable to other processes. A local synchrony implementation enforces atomicity without using locks or semaphores.

Sequential consistency means that the order in which accesses are executed is consistent with the order specified by each individual process's sequential program [Lam79]. Maintaining sequential consistency is a problem in multiprocessors because stochastic delays in the network allow operations issued by the same process to arrive at global memory in an order inconsistent with the order in which operations were issued. The simplest solution, which would be to disallow the pipelining of memory accesses, is undesirable because pipelining is an important way to lessen effective memory latency. A local synchrony implementation enforces sequential consistency without restricting the pipelining of operations.

A local synchrony implementation can be used to implement data-dependent atomic actions (where one or more actions within an atomic action are dependent upon the results of one or more of the other constituent actions) using split operations [WiR89]. Williams has described a family of cache-coherency protocols [Wil93] based on isotach networks. Local synchrony also facilitates FIFO combining [Ran87], which allows access combining to be implemented without the costly associative search necessary in conventional systems. In light of the many possible uses of local synchrony implementations, it is desirable to know whether local synchrony can be implemented correctly and efficiently, in order to provide the benefits described above to parallel computations.

Our work concerns the implementation of local synchrony. We address implementation issues for local synchrony on general parallel processing architectures. We discuss some of the fault-tolerance capabilities of a local synchrony implementation. We also provide both analytical and simulation studies that model and evaluate the performance of local synchrony, compared to conventional implementations, for several operating environments.

Previous work has provided some general implementation information for local synchrony [RWW89] [Wil90]. We explore this area in depth. We present an implementation plan for local synchrony on an NYU Ultracomputer-type architecture, including operative algorithms, a lowlevel switch design realizable with current technology, and a proof of deadlock freedom. We then present a general implementation that can be realized on any parallel architecture and give a formal proof of correctness for the technique. Our general solution is a significant advance over other possible approaches because it provides greater opportunities for parallelism with smaller memory requirements.

A locally synchronous system has several properties which adapt well to current fault-tolerance research in both hardware and software. We explore these properties and how they may be advantageously exploited. We then present and prove correct a local synchrony checkpointing and rollback procedure that is compatible with our general implementation technique.

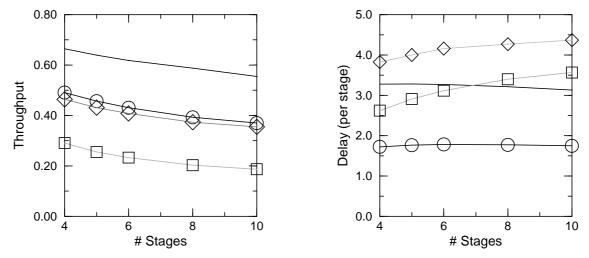

In order to demonstrate that local synchrony implementations are both valuable and feasible, we must show convincingly that the performance costs of implementing such a system are moderate compared to the benefits gained. We first present analytical models of local synchrony implementations by advancing existing modelling techniques. These analytical studies validate our simulation studies of the same implementations. The simulation studies compare local synchrony implementations to conventional implementations under workloads that include atomicity and sequential consistency constraints. We show that, while the conventional implementations outperform local synchrony in situations where these constraints are minimal, local synchrony outperforms by a significant factor conventional systems under workloads with high atomicity and sequencing constraints. The remainder of this dissertation is as follows:

Chapter 2 contains an overview of MIMD architectures, background information on local synchrony and related topics, and discussion of fault-tolerance and performance issues related to the implementation of local synchrony.

Chapter 3 includes a motivation for our work and a specific implementation of local synchrony, including a proof of deadlock freedom and a low-level switch design for the communication network. Also we present an alternate deadlock-freedom proof, covering certain architectures, that does not require the use of ghost messages.

Chapter 4 presents a general implementation technique that allows local synchrony to be implemented on most parallel processing architectures. We prove that implementations developed using our technique are correct and deadlock-free, and show that our technique provides more opportunities for parallelism and uses less memory than other approaches.

Chapter 5 discusses the fault-tolerance capabilities of local synchrony implementations and presents a simple scheme to provide a measure of fault tolerance in the presence of hardware redundant paths. Then we present a checkpointing and rollback procedure, which provides rollback capability for the general implementation, and prove the algorithm correct.

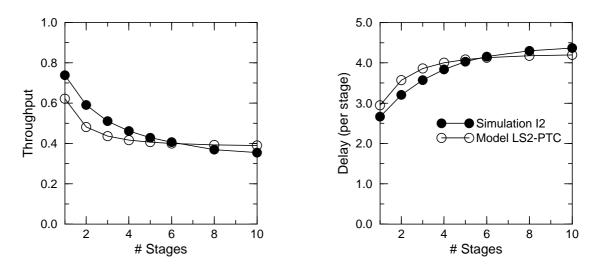

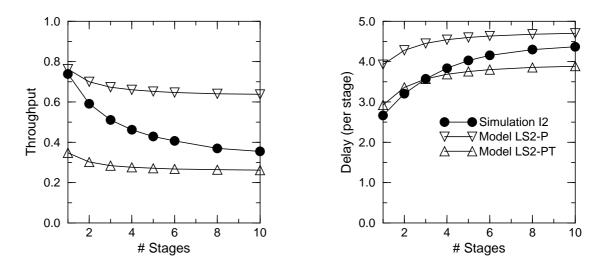

Chapter 6 presents several analytical models of local synchrony implementations on an NYU Ultracomputer-type architecture using both a low-throughput and a high-throughput switch design. We use these analytical models to validate our later simulation studies. The simulation studies compare the performance of local synchrony and conventional implementations under various workloads with varying degrees of sequencing constraints. We also compare local synchrony to another timestamp ordering implementation, *ltu ordering*.

Chapter 7 presents conclusions and an overview of the future work we intend for this area.

# 2.0 Background

This section presents relevant topics, literature review, and a background overview as an introduction to our area of research. Sections 2.1 and 2.2 present an overview of concurrent architectures, define several terms which will be of importance in later discussions, and discuss the nature of communication in a multiprocessor environment. These sections act as an introduction to the general area of our work.

Section 2.3 introduces combining systems and reviews relevant research in this area. Section 2.4 presents Williams' [Wil93] approach to concurrency control. This is the main theoretical background for our work. The basis of our work is the implementation of a concurrency control mechanism which meets Williams' constraints of atomicity and sequential consistency, and ensures conflict-free serial schedules [Wil93] for any execution. These conditions are discussed in this section.

Section 2.5 presents the concurrency control mechanism *isochrons* [Wil93]. Isochrons are a concurrency control mechanism, designed for multiprocessing systems, which are compatible with the concurrency control approach defined in section 2.4. Isochrons provide a limited form of atomic access in multiprocessing architectures.

Section 2.6 presents local synchrony as a method for the implementation of isochrons. The main thrust of this dissertation is research leading to implementations of local synchrony on interesting multiprocessing systems, which will facilitate the implementation of isochrons and other high-level concurrency control mechanisms. Section 2.7 reviews research related to concurrency control, isochrons, and local synchrony.

Sections 2.8 and 2.9 present previous work on fault tolerance and performance issues in multiprocessing systems.

## **2.1 MIMD Architectures**

Our research deals with asynchronous multiprocessing computers utilizing the *Multiple-Instruction Stream*, *Multiple-Data Stream* (MIMD) [Fly66] system architecture. A MIMD proces-

sor generally consists of a number of nodes connected by communication channels that are-usually-organized in a regular pattern (e.g., a hypercube). Each node may include zero or more processing elements and zero or more memory elements, as well as the routing hardware necessary for each of the node's input/output channels. Each processing element may execute a different program—as opposed to *Single-Instruction Stream*, *Single-data Stream* (SIMD) architectures, where each element executes the same program, albeit with different data.

This model encompasses both *message-passing* systems, in which processes communicate by sending messages to each other, with each processing node 'owning' a section of global memory, and *shared-memory* systems, in which processes communicate through global memory, which is shared. Message-passing systems may be cast as a subset of shared memory systems in which any node containing a section of global memory also contains a processing element which controls access to that memory. We choose to use the shared-memory model for our discussion and research, given the ease with which message passing can be implemented in it.

Multiprocessing systems may be either *synchronous*, in which processing occurs in lockstep phases governed by a global clock, or *asynchronous*, in which processing elements operate independently. The operation of a synchronous system is well suited to applications which are highly data-parallel in nature, consisting of groups of similar processes performing similar operations. These types of systems are very close to SIMD systems in operation. Many applications, however, are not easily cast in the data-parallel paradigm. These applications are better suited to the asynchronous model. Our work investigates the efficiency and fault-tolerance of local synchrony as a way to achieve the benefits of synchronous processing on asynchronous processors, without unduly compromising the benefits (e.g., performance) of asynchronous operation.

Padmanabhan [Pad90] distinguishes between *direct* and *indirect* interconnection schemes. In a direct interconnection scheme, processing elements are connected in a network using point-topoint links. An indirect scheme separates the architecture into processors and memory (or combined processing/memory nodes) and a switching network. Generally, indirect architectures are designed under the shared memory paradigm, while direct architectures are usually message passing systems. Exceptions to this rule include the indirect binary cube, which is an indirect message passing design.

*Equidistant* architectures are a special kind of multiprocessing system. *Distance* refers to the number of network stages or point-to-point steps which a given memory access must traverse in order to reach its destination. In an equidistant system, the distance an access requested by any processing element travels to any shared memory location is constant for all processing elements and memory locations. Equidistant architectures generally take the form of shared-memory, indirect machines (e.g., the NYU Ultracomputer [GGK83]).

Non-equidistant systems are usually directly interconnected and include most messagepassing and several shared memory designs. In a non-equidistant architecture, a node generally includes both processing and memory elements, along with switching hardware. Examples of nonequidistant architectures are numerous and include hypercubes [Sei85], cube-connected cycles [PrV81], rings, toroids, and meshes.

# 2.2 Routing, Message Transfer, and Deadlock

A multiprocessor with a *uni-path* network architecture has a unique physical path from any processing element to any memory element. Uni-path systems tend to be limited to equidistant systems, but neither is a requirement for the other. The Ultracomputer is again a good example of this class of architectures. Routing decisions in such a system are straightforward. In order to reach its destination, a message has only one possible choice of path at a given point, so routing decisions may be hard-wired into the switch. With the advent of hardware redundancy schemes for fault tolerance (section 2.8), this type of system has largely been replaced by *multi-path* systems.

In a multi-path system, a message bound for a given memory location may travel any of a number of possible paths in order to reach its destination. Routing schemes for such systems traditionally emphasize deadlock freedom first. A second priority for these systems is to route messages along the shortest possible paths in order to limit network latency. Since much of our work involves multi-path routing systems that can be implemented in the hypercube environment, we discuss several types of hypercube routing schemes here.

Each node in an *n*-dimensional binary cube is labeled with an *n*-digit binary number and is directly connected to *n* of its neighbors. The label assigned to each of these neighbors differs from that of the given node in one binary digit, or one dimension of the cube. Thus, the Hamming distance—or length of the shortest path—between any two nodes is the number of digits with different addresses.

A simple routing scheme in this environment would compare the current node address of the message with its destination, then route the message along one of the output lines crossing a dimension that the message must cross in order to reach its destination. This scheme is provably minimal. The selection of possible lines along which to route the message can be non-deterministic, or can take into account any criteria, such as network load or faulty lines.

Dally and Seitz [DaS87] describe a system called *E-Routing*, where the message always crosses the highest-order uncrossed dimension that needs to be crossed. E-routing may also be *low-order*, crossing the lowest-order dimension first. Dally and Seitz prove that E-routing is dead-lock-free for the hypercube. The authors present a method for creating deadlock-free routing schemes using *Virtual Channels* [DaS87], and Dally goes on to show that virtual channels also can provide increased efficiency in parallel communication systems [Dal90].

It is important to distinguish here between *physical, virtual*, and *routable* paths. The network topology of any given architecture defines physical paths, which are made up of actual physical links between nodes. Some routing schemes will cast a given physical link as several virtual links for resource allocation and deadlock freedom purposes. Thus, several virtual paths can exist over a given physical path. Finally, routing schemes for multi-path architectures often will not utilize all physical paths from one node to another. Thus, a routable path is a physical or virtual path used by the routing scheme. For example, in the Hypercube architecture, there are two minimumlength paths from node 11 to node 00, 11-10-00 and 11-01-00. High-order E-routing will only pass messages along the first path, however, so 11-01-00 is a physical path but not a routable path.

More interest has recently focused on dynamic systems that route messages based on current network load conditions and the presence of faulty nodes or links in the network [ChS89]. One important factor in the design of these types of systems is the method of gathering local or global information on load conditions and faults. Another important issue is the level of compatibility with concurrency control mechanisms and network performance enhancements such as combining, which require certain path restrictions.

An entirely separate routing issue concerns how messages are transferred from node to node. In *Store-and-Forward* networks, a message is stored completely at a node, and forwarded to the next node as a whole. This is the simplest scheme, and a significant volume of work has been produced on deadlock-free routing algorithms for these systems [Gun81][MeS80][Gel81]. These algorithms assign a partial order to resources by utilizing a structured buffer pool, ensuring that circular wait situations which cause deadlock cannot occur.

*Wormhole* systems [Dal87] break messages into small manageable packets. Routing information is contained in flow-control digits or flits. In wormhole routing, the head of a message (including routing flits) is advanced directly from incoming to outgoing channels at a node. As packets appear on the input channel, they are passed to the output channel. As this process occurs, messages can spread out across the network, with the requirement that the packets comprising a message always occupy contiguous channels. If the head of a message is blocked, the backed-up packets of that message then prohibit any channels they occupy from being used by other messages until the message header becomes unblocked and the message resumes transmission.

Because message flits cannot be interleaved in buffers, the priority buffer approach to deadlock freedom is not feasible for wormhole systems. However, Dally and Seitz [DaS87] show that assigning a partial order to channels rather than using buffers is sufficient for deadlock free-

dom in wormhole systems. This is the *virtual channels* approach, in which links between nodes are treated as multiple virtual links through context switching.

A third approach with similarities to both systems is *Virtual Cut-Through*[KeK79]. Here messages are broken up and allowed to spread throughout the network, but a node may not accept any part of an incoming message unless it can buffer the whole message (in the event that it is blocked). The deadlock properties of this type of system are identical to those of store-and-forward systems, although in low-traffic situations Virtual Cut-Through may offer greater throughput at less cost and network complexity.

Communication schemes are important to our work, because the implementation of local synchrony may alter network switching and routing algorithms. We show that changes in the communication systems of multiprocessors due to the implementation of local synchrony will not introduce the possibility of deadlock into the system, and that local synchrony will be compatible with the communication schemes (or variants) discussed above.

### 2.3 Combining

The objective of memory access combining is to reduce message traffic to and from heavily used global memory locations in a multiprocessor. One method of achieving this goal involves identifying accesses bound for the same memory location during transmission through an interconnection network, and molding these accesses into a single access, the result of which implies a given sequential ordering of the combined accesses. The NYU Ultracomputer was the first to combine accesses to global memory [GLR81][GLR83]; combining was later proposed for the IBM RP3 [Pfi85].

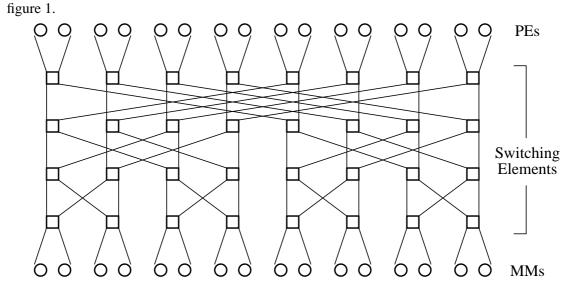

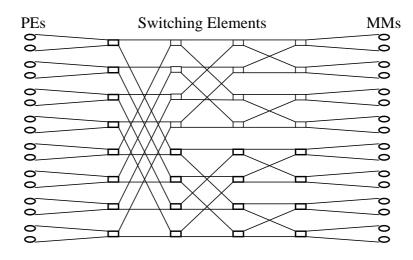

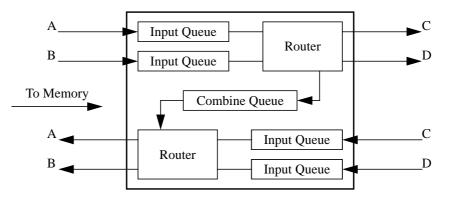

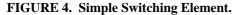

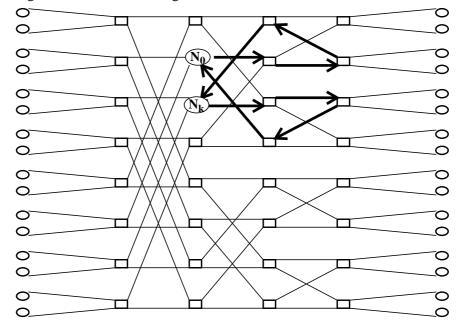

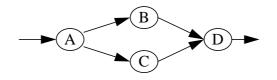

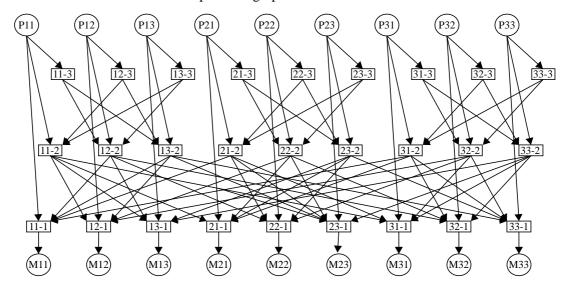

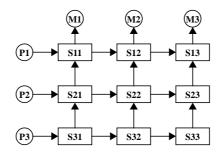

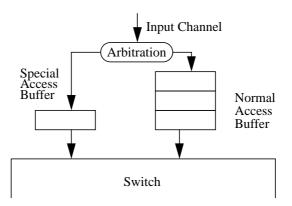

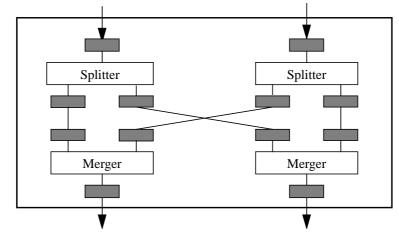

The Ultracomputer is an equidistant, shared-memory multiprocessor consisting of a number of processing elements, each with its own private memory, and a number of memory elements, which house global memory. Processing elements and memory elements are separated by an omega or banyan interconnection network, which provides a unique, same-length path from each

processing element to each memory location. An example of a small Ultracomputer is shown in

#### FIGURE 1. Ultracomputer.

As a simple example of combining, consider the following: Process 1 releases access WRITE(A,5) into the interconnection network. Process 2 releases the access READ(A). Assume at some point, at some switching element in the network, the two accesses are held concurrently. The switching hardware can then combine the two accesses into one access: WRITE(A,5). When this operation is completed, the result is as if both operations had been completed in sequence: WRITE(A,5); READ(A). The new WRITE operation is sent toward memory, while the combining information for the original messages is stored in the switch. When the combined operation returns successfully to the switch, the relevant combining information is extracted from the combining information queue through associative search. The READ access from Process 2 is sent back with the value 5, and the WRITE access from Process 1 is returned successfully.

In order to add power to the combining mechanism, Kruskal, Rudolph, and Snir [KRS88] have proposed the implementation of the READ-MODIFY-WRITE [Rud81] formalism in combining systems. Such a system would have as its basic memory access operation RMW(X,f), where X is the shared variable and f is a function to be performed on that variable. The RMW operation is equivalent to an indivisible execution of the function:

```

function RMW(X,f)

begin

temp := X;

X := f(X);

return(temp)

end

```

A READ operation may be represented in this formalism by performing the identity function, f(X)=X, while a WRITE operation is represented by performing the operation f(X)=c, where c is the constant to be written supplied by the process making the access.

The RMW formalism allows the implementation of much more powerful atomic memory operations. Using RMW operations as the basic, atomic form of memory access in a multiprocessing system gives the designer the freedom to implement almost any operation of the form:

#### memval := memval op val

where *op* is an operation which need not be associative. Possible implementations include the four arithmetic functions, all sixteen Boolean functions, and synchronization functions like full/empty bits. Kruskal, Rudolph, and Snir prove that their combining algorithm is correct by showing that the execution of a given combined operation is equivalent to a possible serial execution of the operations from which it is composed [KRS88].

A by-product of this work, which is important to our research, concerns the *orientation* of combined operations. When two operations are combined, the resulting combined operation, when performed, achieves the same result as some serial execution of the original operations. Consider a system which implements two basic operations: READ and WRITE. In this system, WRITE(B,3) and WRITE(B,4) might be combined into WRITE(B,4), which would, when executed, have the same effect as WRITE(B,3) followed immediately by WRITE(B,4). Thus, the orientation of the combined operation is the serial execution WRITE(B,3); WRITE(B,4). [Note: throughout this work, separation by semi-colons represents sequential orientation, while separation by commas denotes parallel (to the observer) orientation.]

A system implemented as above could combine two READ or two WRITE accesses in any orientation. In the case where a READ and a WRITE operation are to be combined, however, a specific orientation is necessary in the combined operation. The combined operation must be a WRITE, as the variable must be modified, and, because WRITE operations are not generally designed to return the previous value of the variable, the READ operation must be oriented after the WRITE.

Now consider a system implementing RMW operations. RMW operations always return the previous value of the memory location, and can thus be combined in any orientation. In general, any pair of RMW operations that can be combined can be combined in either orientation [KRS88].

Little research has gone into memory access combining on non-equidistant architectures. The most important addition to the combining literature has been the work at Yale on the Fluent Architecture [Ran87] [RBJ88]. While the goal of this work had little to do with combining systems (its goal was efficient PRAM emulation), Ranade was able to show that, given some synchronization, combining operations in the network could be greatly simplified, removing the need for associative search when decombining. The use of synchronization in this case helps to ensure that messages leaving a given node will return to that node *in the same order*. The Fluent machine is a non-equidistant, shared-memory machine, but in the implementation of the combining system, the designers emulate an equidistant network in order to achieve their results. A message leaving a given node will travel the same distance before returning, regardless of the distance to its destination. This means that most messages will travel significantly farther than necessary in order to be serviced.

In [WiR91], Reynolds and Williams show that atomic actions can be combined in a recombining network, without compromising the integrity of the atomic actions. We use this result in designing combining switches for local synchrony, which allow the component accesses of isochrons to be combined if necessary.

## 2.4 An Approach to Concurrency Control

Perhaps the most important problem when working in an asynchronous multiprocessing environment is concurrency control. When multiple entities (i.e., processes) are competing for the use of multiple resources (i.e., global variables) extreme care must be taken to enforce proper accessing principles. The motivation for our own work in this area is parallel memory operations [Wag87] [RWW89] or *isochrons* [Wil93]. Isochrons allow a process to perform exclusive operations on sets of global variables without the need for locking or global synchronization. Local synchrony is a concurrency control mechanism which supports isochrons.

**Definition:** The execution trace of a parallel program is equivalent to a serial schedule if all accesses to shared variables are executed in an order that is consistent with some serial execution of the same program.

In [Wil93], Williams characterizes the goal of concurrency control for parallel programs as 'to ensure that every execution is "serializable." Williams' notion of serializability considers several important factors which extend beyond the definition of a serial schedule given above. The following discussion draws on definitions and results appearing in [Wil90].

A parallel execution and a serial execution are said to be *conflict equivalent* if, in both executions, each shared variable is accessed by the same operations and conflicting operations are executed in the same order. Operations conflict if their combination changes the variable, in other words if they are not both reads. Since read operations do not change the state of a variable, they cannot conflict. Williams formally describes a parallel execution to be serializable if there exists a conflict equivalent serial execution,  $E_s$ , with the following properties:

1. Atomicity - Accesses specified as atomic actions in the parallel execution are executed in E<sub>s</sub> in sequence, without interleaving with other accesses.

An *Atomic Action* is a group of accesses, issued by the same process, that appear to be executed indivisibly, without interleaving with other accesses. An atomic action has the effect of modifying the state of a group of global variables as if the process submitting the atomic action has exclusive access to those variables while the atomic action is being executed.

> 2. Sequential Consistency - Any two accesses made by the same process are executed in the order specified by the process, if any.

The accesses of a given process are sequentially consistent if the order in which they are executed is consistent with the order specified by the process's sequential program [Lam79]. In other words, the memory access requests of a process must be executed in the order in which the process submitted them. Violations of sequential consistency can arise in multiprocessing systems because of network delays and the varying distances that access requests must traverse in order to be executed.

3. Version Consistency - Any two accesses to the same variable are executed in E<sub>s</sub> in the order specified by the program, if any.

Version consistency means that the execution is consistent with any data dependencies specified by the program. These types of dependencies arise when the program specifies the order in which different accesses to the same data should occur. For example, a program might specify that a given variable, modified by a writer, must be read by a specified reader before it can be again modified by the writer. Version consistency is generally enforced by different types of locking mechanisms.

Williams' characterization of the goal of concurrency control for parallel programs is influenced by literature on concurrency control for concurrent databases, by Lamport's definition of sequential consistency [Lam79], and by Shasha and Snir's definition of correct execution of parallel programs [ShS88]. These and related works are discussed in more detail in the following sections. Our work with local synchrony is derived from this goal as stated, and from the need to provide sequentially consistent and atomic execution of parallel programs in asynchronous multiprocessor environments.

## 2.5 Isochrons

Our main goal is to explore implementation issues regarding local synchrony. Local synchrony meets the criteria for sequential consistency and atomicity as defined in [Wil93] and discussed in section 2.4. One benefit would be that local synchrony supports *isochrons* [Wil93], a concept derived from parallel operations [Wag87] [RWW89]. An isochron consists of a set of memory accesses emitted by a given process which appear to be executed simultaneously, so that memory coherency is maintained. Preserving the coherency of memory means that it must not be possible for a process to observe an inconsistent state in global memory due to interleaving of other accesses with those of the given process.

Isochrons are a limited form of *atomic action*. The general form of atomic actions is a group of operations which are performed *atomically* [OwL82], meaning that no process other than the issuer can observe or affect an intermediate state in the execution. This general form of atomic actions allows data-dependent operations. For example, a process issuing an atomic action is able to perform an operation which reads the value of one global variable and writes that value to another, atomically. The issuer is thus able to observe the intermediate state of the execution of the atomic action. This situation allows the issuer to make conditional changes to the atomic action, based on intermediate results of that action. Isochrons, however, enforce a stronger requirement, which removes this capability. In a system implementing isochrons, no process, *including the issuer*, can observe or affect any intermediate state in the execution of an isochron. Thus, isochrons do not support global data-dependent operations.

Consider the readers and writers problem for a pair of shared variables, A and B. A and B contain values which may be read by a number of readers, and may be updated by a number of writers. A reader must read both variables, and a writer must write both. If process 1 emits two READ operations, READ(A) and READ(B), while process 2 emits WRITE(A,2) and WRITE(B,3), it is possible that the order of access to the shared variables would be READ(A); WRITE(A,2); WRITE(B,3); READ(B). In this case, process 1 does not receive a coherent set of responses, but instead receives half 'old' data and half 'new' data.

A common solution to this problem is to utilize a lock or locks to ensure exclusive access to the relevant data. In order to modify A and B, a process would have to acquire the locks on the objects before it would be able to modify the data. The locks would have to ensure the exclusion of both readers and other writers during the time the given writer was accessing the data. This serializing of accesses to shared data inhibits concurrency significantly if several processes are accessing the same data regularly.

In general, the processes of a parallel program will need atomic access to different sets of shared variables at different points during their execution. In order to avoid deadlock due to processes circularly waiting for each other to give up locks, processes must be made to acquire locks in a specific order. This situation can cause processes to contend severely in acquiring high priority locks, which further slows access to the required data by requiring more global memory accesses. Alternatives to resource ordering in this situation admit the possibility of starvation.

Isochrons provide deadlock- and starvation-freedom without the use of access-intensive locks. The use of isochrons in the above example would allow only access orders in which the order of execution *at each memory location* is consistent with a serial schedule providing atomic access. To a monitoring process, the order of execution would appear to be one of the following: READ(A), READ(B); WRITE(A,2), WRITE(B,3) or WRITE(A,2), WRITE(B,3); READ(A), READ(B). Note, however, that the actual order of execution of the memory accesses could be READ(A); WRITE(A,2); READ(B); WRITE(B,2). While there are several different possible execution orders, from the viewpoint of any given process the set of operations in a given isochron would appear to have been performed *indivisibly*, or simultaneously.

The execution of a parallel program is said to be sequentially consistent if "the result of any execution is the same as if the operations were executed in some sequential order, and the operations of each individual processor appear in this sequence in the order specified by its program" [Lam79]. An isochron program, when executed, must be sequentially consistent and also ensure the atomicity of parallel accesses to global memory. This idea is similar to Reed's notion of Concurrent Atomicity [Ree83]:

For all executed steps o not in A (the atomic action), either o precedes all steps in A, or o follows all steps in A.

Isochrons are an attempt to apply this property to memory access in distributed systems. They have the potential to be an extremely powerful concurrency control mechanism: they could reduce the need for much of the locking and synchronization of memory access in shared memory architectures, and thus significantly reduce global memory access traffic.

The implementation of isochrons requires a system which guarantees exclusive access to distributed memory locations. Our own requirements for such a system exclude explicit locking of locations and process synchronization in making this guarantee. Local synchrony [RWW89] [Wil93] meets these requirements though implicit logical timestamping of global memory accesses. Our research studies the implementation of local synchrony on various asynchronous architectures. The next section presents Williams' [Wil90] theoretical definitions for Locally Synchronous systems.

## 2.6 Local Synchrony

In [Wil90], Williams describes a set of clock conditions. These conditions describe the operation of a timestamping system for global memory accesses in a parallel architecture. A system operating under these conditions is shown to have a conflict-free serial execution which meets the requirements for sequential consistency and atomicity discussed in section 2.4. In [RWW89], a method of implementation is described which meets these clock conditions. This concurrency control mechanism is called *local synchrony*.

Williams distinguishes the following types of events:

**Definition:** An **issue event** occurs when a process queues a global memory access to be sent for execution. Issue events occur in the sequentially consistent order specified by the issuing process.

**Definition:** An **execute event** is when a global memory access actually occurs.

**Definition:** An **emission event** occurs when an access issued by a process is actually sent. An access issued by a process may, for one reason or another, be held until a later time before being sent to memory. The actual sending of such an access would constitute an emission event.

By definition, the sequence of events for an access is always: issue, emission, execute.

Because local synchrony is a logical timestamping system, two or more of these events might

occur at the same logical time. Each event is assumed to be atomic. In other words, each process issues operations one at a time, and each operation is executed at memory one at a time.

In [Wil90], two relations are defined on operations:

$OP_i \rightarrow OP_j$  (precedes) if (1) each accesses the same variable and the execute event of  $OP_i$  occurs before that of  $OP_j$ . or (2) each is issued by the same process and the issue event of  $OP_i$  occurs before that of  $OP_j$ . or (3)  $OP_k$  exists such that  $OP_i \rightarrow OP_k$  and  $OP_k \rightarrow OP_j$ .

$OP_i$  iso  $OP_j$  if both  $OP_i$  and  $OP_j$  are from the same isochron.

Consider a global clock mechanism which assigns a 'time',  $C(OP_i)$ , to every execute event. Let  $C(Op_i)$  consist of an ordered pair (*tick, tock*), and let  $C(OP_i) < C(Op_j)$  if  $C(OP_i)$  lexicographically precedes  $C(Op_j)$ . The *tick* component of  $C(OP_i)$  defines the timing relationship between  $OP_i$  and other execute events scheduled by other PEs. The *tock* component defines the relationship between  $OP_i$  and other execute events scheduled by the same PE. An execution  $E_p$  of a parallel program is then serializable if it conforms to the following clock conditions:

Condition 1:

$$OP_i \rightarrow OP_i \Longrightarrow C(OP_i) < C(OP_i)$$

Condition 2:  $OP_i$  iso  $OP_i \Longrightarrow C.tick(OP_i) = C.tick(OP_i)$

These conditions guarantee that no two execute operations are executed in  $E_p$  at the same logical time. Williams goes on to show that any isochron program,  $E_p$ , that conforms to these conditions is sequentially consistent and preserves atomicity of isochrons by proving that  $E_s$  is sequentially consistent, atomic, and conflict equivalent to  $E_p$  [Wil90]. Since all execute operations are executed at distinct logical times, those times define a *serial schedule*, or total ordering, of the global memory accesses of  $E_p$ .

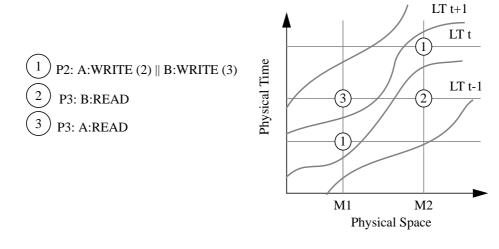

While it provides a total logical ordering to memory accesses in a distributed system, local synchrony requires physical ordering of only accesses to the same memory location, or, more realistically, to the same memory element. One can see that inconsistencies in the state of global memory *can* exist with this implementation. Consider the readers and writers example in section 2.5, where Process 2 must perform indivisible writes on two global variables, A and B, located at memory elements M1 and M2, respectively, and Process 1 must perform indivisible reads. If process 2 submits the isochron:

#### P2: A:WRITE(2) || B:WRITE(3);

there is no guarantee that these accesses will be performed at the same *physical* time. For example, at physical time *i*, M1 might be performing accesses in logical time unit *t*, and perform the write of A. Meanwhile, M2 might be only executing accesses in logical time unit *t*-2. Due to heavy access traffic at its MM, M2 might not get to logical time unit *t* until physical time i+j. So there is a physical interval of length *j* during which another process, P3, might read both A and B and receive an inconsistent version of the state which A and B together represent. However, in order to do this, P3 must emit separate, non-isochronic accesses which will be performed during logical time units t+1 and t-1, respectively. Atomicity is only guaranteed for isochronic accesses, or accesses performed at the same logical time unit. Sequential consistency, with respect to accesses to the same global variable, is guaranteed for all accesses.

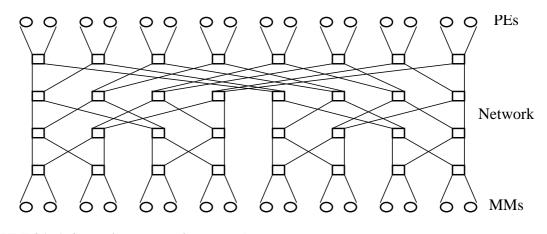

#### FIGURE 2.

Figure 2 gives an accurate representation of this scenario. One can see that, in order for a process within the system to 'see' an inconsistent state of memory, its accesses to that memory would have to be during different logical time units, and thus not isochronic. It is impossible for a process within the system to receive inconsistent data from an isochronic access to memory.

The importance of this limited form of synchronization should not be underestimated. Local synchrony provides a computation with total orderings of events and synchronization without requiring globally synchronous processing. A global memory access which occurs *physically* before another might occur *logically* after, given that the two events represent accesses to different global memory locations. This flexibility allows a system to perform in a generally asynchronous manner, while gaining much of the power of synchronous operation.

The main focus of our work pertains to local synchrony as defined in this section. Our research concerns the implementation of local synchrony in various multiprocessing environments. The definition of local synchrony outlined in this section, and specifically the clock conditions of local synchrony defined by Williams, provide a basis for any implementation of the system.

## 2.7 Schemes Related to Isochrons and Local Synchrony

In database concurrency control, timestamp ordering protocols guarantee concurrency control for any set of accesses without specific locking of the relevant data. Each access is assigned a specific 'execution time', and accesses to a given global variable are constrained to be executed in timestamp order. To be executed, a READ access must have a timestamp greater than the last WRITE, and a WRITE access must have a timestamp greater than any preceding access [BeG81]. In the basic timestamp ordering system, this means that an access will be aborted if it does not meet the above requirements.

*Conservative* timestamp ordering systems eliminate rollbacks by executing accesses only if no older access will ever be received [BeG80] [Mil79]. This type of system is generally based on global knowledge about accesses currently in the system and the current timestamps of processes. Timestamp ordering systems generally enforce a policy of sequential consistency, which dictates that processes issue timestamps in ascending order.

Local synchrony may be cast as a conservative timestamp ordering system. Local synchrony is constrained to produce sequentially consistent serial schedules for global memory accesses. The atomicity of isochrons is guaranteed with no possibility of rollback. Bernstein and Goodman [BeG81] state that, in a conservative system, "When a scheduler [node] receives an operation O that might cause a future restart [logical time conflict], the scheduler [node] delays O until it is sure that no future restarts [logical time conflicts] are possible. Either of the two general implementation techniques (sorted transmission, sorting at memory) fits this description.

There are several differences between databases and applications programming which affect the problem solver in this area [Wil93]. First, database systems generally require full recoverability of data in the case of system failure, whereas a parallel program can just be rerun. A database manager is therefore generally able to incur greater overhead in ensuring that transactions are performed correctly, whereas a concurrency control concept for a parallel operating system must incur a minimum of overhead in order to preserve memory cycle time. Concurrency control in databases generally requires only atomicity of transactions, because the nature of the database environment guarantees sequential consistency. Concurrency in parallel programs also requires sequential consistency, but it must be explicitly enforced by a system such as local synchrony.

Atomic Actions are a concept designed to provide exclusive access to multiple data items. An atomic action is a set of accesses released by a process which, when executed, appear to have occurred simultaneously, allowing no interleaving of accesses by other processes during their execution. Atomicity may be ensured by an underlying system based on two-phase locking or timestamp ordering. Atomic actions were developed in the database literature by Eswaran et al [EGL76]. Reed [Ree83] suggests a timestamp ordering implementation of atomic actions based on timestamping by physical clocks and the use of version histories in memory. A physical clock is based at each processing element, and the clocks are kept loosely synchronized by a global clock synchronization algorithm. Again, while this implementation does allow the implementation of atomic actions, the problem of aborted operations still exists.

Concurrency control as applied to parallel architectures and operating systems has only recently come under study. In [Lam78], Lamport proposed a system of *logical clocks*, which would provide partial ordering to the events of a system of processes. These clocks would consist of a function that assigns a number to each event occurring at a given process, in increasing order,

where the number would be considered the *time* that the event occurred, although this number would have no relation to actual physical time. When a process sends a message to another process, Lamport requires only that the receive time of the message be greater than the send time, since one would generally assume that a message must be sent before it is received. Lamport's clock conditions are:

Condition 1: If a and b are events in process Pi, and  $a \Rightarrow b$ , then Ci(a) < Ci(b).

Condition 2: If a is the sending of a message by process Pi, and b is the receipt of that message by process Pj, then Ci(a) < Cj(b).

Since ordering by physical occurrence of events at different processes in a distributed system is not generally possible, Lamport first generates partial orderings for events occurring in individual processes, and to inter-process communication, using the logical clock, then provides a total ordering of events by arbitrary ordering of the processes themselves. Note that this total ordering represents a sequentially consistent (by the clock conditions) serial schedule, meaning that this ordering of events is equivalent to a possible ordering of events if the computation were simulated on a traditional Von Neuman machine. Lamport uses this ordering to solve synchronization problems.

Jefferson [Jef83][Jef85] has proposed a more general theory of logical time in *Virtual Time Systems*. Such a system consists of a group of processes that execute in coordination with logical clocks, and which obey certain conditions. These conditions echo Lamport's clock conditions, except that they also restrict the processing of events received by a particular process:

Condition 1: The virtual send time  $[C_i(a)]$  of a message must be less than or equal to its virtual receive time  $[C_i(a)]$ .

Condition 2: All messages directed to a particular process must be processed in nondecreasing virtual receive time order.

The semantics of such systems obey the requirement that, "If an event A has a virtual time less than that of event B, then the execution of A and B must be scheduled so that A appears to be completed before B starts" [Jef83]. Note that there is no requirement for actual physical ordering of events in such a system. The requirement is only that, to the processes in the system, the events appear to have occurred in the given order.

The goal of Virtual Time systems is to create a temporal coordinate system in which a distributed computation can be embedded that will provide correct, logical orderings of the events of that computation. Again, the correctness of the logical orderings corresponds to their providing a proper serial schedule. Jefferson's protocol is optimistic, utilizing state-saving and roll back in order to meet its clock conditions. Cascading rollbacks are a significant problem with the Time Warp approach, although Jefferson has shown that there is a limit beyond which rollback cannot occur in a given computation: namely, the earliest current virtual time of any event in the system.

Local synchrony is a conservative timestamp ordering protocol, which guarantees serial scheduling and sequential consistency, as well as the atomicity of isochrons, without the possibility of rollback.

Awerbuch [Awe85] utilizes a system similar to local synchrony in order to simulate synchronous architectures on asynchronous networks. Awerbuch uses the notion of *safety*—where a node knows that it is finished with its operation for a given time unit—to generate a barrier for the whole network. This barrier is passed when a simulated global clock recognizes that it has been reached (all nodes are safe) and generates the next synchronous step. Safety is recognized by a node when it receives confirmation from each of its neighbors that they will send it no more work prior to the next barrier. Local synchrony elements use safety in order to safely proceed to the next logical time unit.

Ranade [Ran87] uses *end-of-stream* (EOS) messages, similar to local synchrony tokens, to emulate a CRCW PRAM on a butterfly. Unlike local synchrony, EOS messages are sent after *each* access. The EOS messages act to synchronize the operation of the system. The passage of EOS messages from an input to an output line represents timesteps of the 'global' clock as represented at each switch. Combining is implemented in such a way that only one access is executed at any memory location during any timestep. A main difference between Ranade's work and local synchrony is that Ranade requires that all messages travel the same distance to reach memory. This distance is larger than the minimum necessary traveling distance. Local synchrony allows messages to travel the minimum distance defined by the architecture to reach memory. The Fluent machine is also a specifically targeted implementation. Our implementation of local synchrony is a general approach, which can be implemented on any connected architecture (as defined in chapter 4). Ranade also failed to note that atomicity could be guaranteed using such systems.

Ranade also, in order to guarantee bounds on the emulation, is able to implement efficient (no associative search) combining by keeping accesses sorted as they traverse the network. Efficient (FIFO) combining is discussed in section 2.2.

In [ChM79], Chandy and Misra present a scheme for distributed simulation. The Chandy/ Misra system is a conservative timestamp ordering system much like local synchrony. The authors' implementation scheme is less efficient than ours, however, and their proof of deadlock freedom is slightly flawed. Kumar [Kum86] proves the Chandy/Misra system to be deadlock-free for feedforward networks consisting of fork and join nodes. In [ChM87], Chandy and Misra develop the idea of conditional knowledge, which increases the efficiency of their distributed simulation scheme.

This section provides us with a background with which to present an *Operative Condition* of local synchrony. This condition will constrain our research toward efficient and fault-tolerant implementations of local synchrony by focusing our efforts on implementations which specifically meet this condition. The operative condition of local synchrony stems from the clock conditions discussed in the previous section, and is stated in this way:

A local synchrony implementation is a conservative (logical timestamp) ordering system for global memory accesses. Thus, an entity (PE, switch, or MM) operating in a Locally Synchronous manner must perform actions on a given resource (channel, memory location) in a manner which preserves a logically serializable schedule of global memory access.

An entity operating in a conservative manner is constrained not to perform any action until it has, with certainty, performed all (logically) previous actions. Local synchrony requires only that the MMs operate conservatively in processing global memory accesses. However, an implementation of local synchrony may include conservative operation by switches and/or PEs as well.

# 2.8 An Implementation of Local Synchrony

In [Wil93], Williams presents basic implementation suggestions for local synchrony on an equidistant network and discusses extensions to this technique for non-equidistant architectures. Williams does not present specific local synchrony implementations or prove deadlock freedom. We present here the general implementation technique. For simplicity, we make several assumptions, which are based on those of Williams in [Wil93]:

- 1. The system is a network of nodes communicating over FIFO channels with finite but unbounded delay.

- 2. Each node consists of a switch, a processing element (PE) and a switch, a memory module (MM) and a switch, or a PE, an MM, and a switch.

- 3. Each process runs on its own PE. There is no multiprogramming or process migration.

Local synchrony may be characterized by the serializability, or constructible serial schedule, of all accesses performed. This serial schedule is represented by timestamp ordering of global memory accesses. Each node stays consistent with this serial schedule by loose synchronization with neighboring nodes.

This loose synchronization among nodes is implemented in the following way: each node in the system periodically emits a set of control signals, or *tokens*, one along each of its output connections to other nodes. These tokens represent the boundaries between the logical timesteps of the node's own local logical clock. For the purposes of further discussion, we will define  $ltu_i$  at a given PE to be that period of time between the sending of token *i*-1 and token *i*. During an ltu, a PE may emit zero or more accesses (accesses may only originate in nodes containing a PE).

In order to implement *local* concurrency control, the switch associated with each node must route all accesses received from its neighbors during its previous ltu before generating its next ltu. Switches may route accesses without regard to their timestamp order within the current ltu, in which case accesses must be buffered and sorted at the MM, or by merging sorted streams of

accesses by timestamp. We shall discuss these and other schemes for the transport of accesses in section 6.4. For simplicity, the reader may wish to assume in the following discussion that accesses are kept sorted by timestamp throughout their traversal of the network. Given the operative condition of local synchrony, MMs *must* process accesses (perform execute events) in a conservative manner.

Extended from [Wil93], a PE schedules emission events subject to two constraints:

1. All the accesses in any given isochron are emitted in such a way that the execute event of each will occur during the same ltu.

Constraint 1 is a restatement of the second clock condition, which guarantees atomicity for isochronic accesses. In a general implementation, isochronic accesses may have different distances to traverse in order to be executed. In this case, Constraint 1 requires the PE to guarantee that accesses arrive at memory during the same ltu. Constraint 1 is relatively simple to meet in an equidistant implementation. A PE must emit all the accesses in a given isochron during the same ltu. In a non-equidistant implementation, however, guaranteeing Constraint 1 is somewhat more difficult. Ways to guarantee Constraint 1 include holding accesses with shorter distances to travel for later emission, or routing messages along longer than necessary paths.

Let T(I) be the beginning logical time unit in which isochron will be emitted into the network. Let D(I) be the maximum distance any one access of I will have to travel to memory. Finally, let  $OP_i$  be a member access of isochron I.  $d(OP_i)$  is the distance that  $OP_i$  must travel in order to reach memory.  $OP_i$  will then be emitted into the network at time:

$$t(OP_i) = T(I) + D(I) - d(OP_i).$$

This is one possible implementation of Constraint 1; it guarantees that all the member operations of a given isochron will arrive for servicing during the same ltu. The main requirement for this type of operation is that a given processing element must be able to ascertain the distances that its accesses must travel in order to be serviced.

2. Any pair of accesses from a given process that access the same variable must be emitted in such a way that the execution events take place in the order specified by the process.

Constraint 2 provides sequential consistency for the accesses of a given PE. Sequential consistency is guaranteed in the execution of accesses by ensuring that they are executed *in issue order*. This ordering may be guaranteed through different combinations of routing, buffering, and sorting schemes for accesses. For example, rather than emit accesses in issue order, a PE might route an access in such a way that it is executed after an access emitted later but routed along a shorter path. This works because the logical time to traverse a path to memory is a function of distance, or the number of switching elements an access must go through to reach its destination.

The logical time of execution of each access is determined by the issuing PE through explicit timestamping, implicit timestamping (determined by ordering conventions implemented in the system), or a combination of the two. The timestamp for access  $OP_i$ , denoted  $TS(OP_i)$  [Wil93], is an ordered pair (*tick*, *tock*), where the *tick* component is itself an ordered pair (*ltu*, *pid*). The ltu component of  $TS(OP_i)$  is the ltu in which the execute event of  $OP_i$  will occur. In order to assign *ltus*, the PE is required to be able to compute the number of local synchrony ltus that will pass while a given access travels to its destination. This number of ltus is equal to the distance which the access must travel.

Note that, due to Constraint 1 above, an access issued by a process may be held by the PE for later emission. In order to preserve the definition of the *precedes* relation ( $\rightarrow$ ) given in section 2.6, the PE must ensure that *ltu* components are assigned in non-decreasing order as accesses are *issued*, rather than emitted. This topic will be discussed further in chapters 3 and 4.

The *pid* component is an ID unique to the issuing PE. The use of this *pid* in the timestamp assigns a disjoint interval of logical time during each ltu to the accesses issued by the given PE. This disjoint interval provides atomicity for isochrons. This technique for providing atomicity is widely used in database concurrency control [Ree83] [RSL78].

The *tock* component of the timestamp provides sequentially consistent ordering for any operations accessing the same variable, from the same process, in the same ltu, i.e.  $TS(OP_i).tock =$

*j* if  $OP_i$  is the *j*<sup>th</sup> access from the PE identified by  $TS(OP_i)$ .tick.pid to be executed during ltu  $TS(O-P_i)$ .tick.ltu.

Williams makes the following propositions regarding the operation of the system as described. These propositions relate equally well to the technique presented here:

Proposition 1: For any pair of accesses,  $OP_i$  and  $OP_j$ ,  $OP_i$  iso  $OP_i \Rightarrow TS(OP_i)$ .tick =  $TS(OP_i)$ .tick.

Proposition one is true by PE Constraint 1, which guarantees that the *ltu* component of the

timestamps of each operation in an isochron will be the same, and by the fact that an isochron is

defined to be a group of operations emitted by one process, and thus all having the same *pid*.

Proposition 2: For any pair of accesses, OP<sub>i</sub> and OP<sub>j</sub>, issued by the same process, if OP<sub>i</sub> is issued before OP<sub>j</sub>, TS(OP<sub>i</sub>) < TS(OP<sub>i</sub>).

Proposition 2 is true because the assignment of timestamps is constrained to be nondecreasing by issue order. If  $OP_i$  is issued before  $OP_j$ , then either  $OP_i$ .  $Itu < OP_j$ . Itu, or  $OP_i$ . tock $< OP_i$ . tock, and thus  $TS(OP_i) < TS(OP_j)$ .

Proposition 3: For any pair of operations,  $OP_i$  and  $OP_j$ , that access the same variable, if the execute event  $OP_i$  occurs before  $OP_j$ , then  $TS(OP_i) < TS(OP_i)$ .

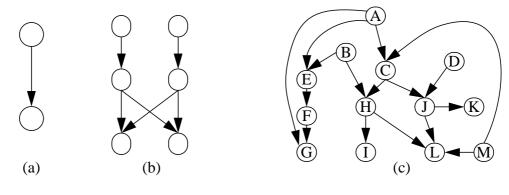

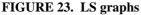

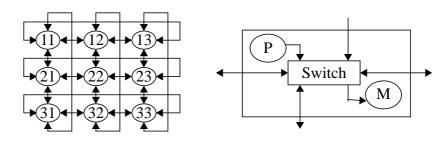

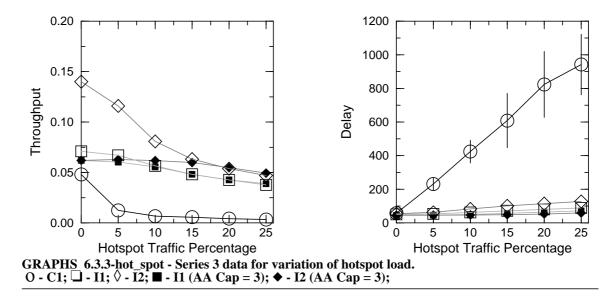

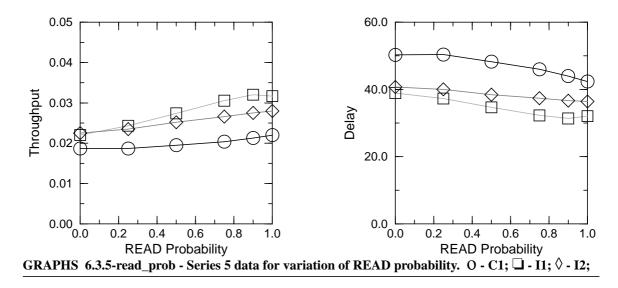

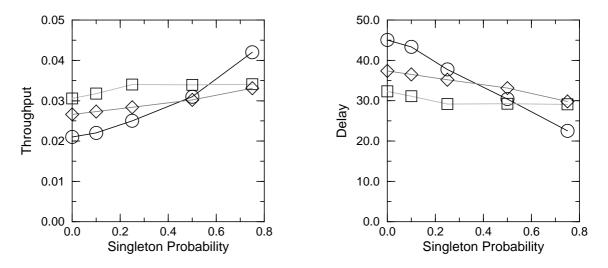

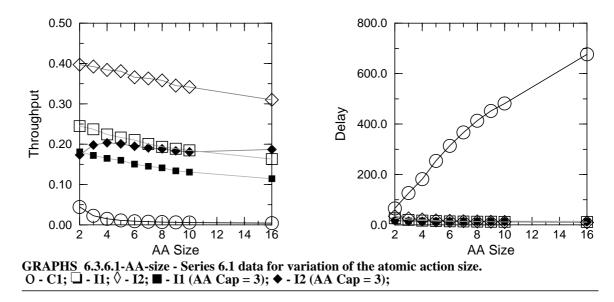

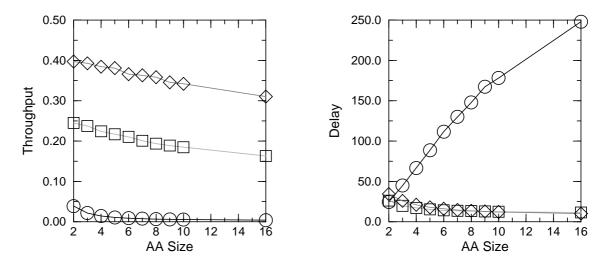

Proposition 3 stems from the requirement that operations either be transmitted through the network in timestamp order, or be sorted by timestamp order at memory before their execute events occur. This, of course, guarantees that accesses will be executed in timestamp order.