# Specifying Instructions' Semantics Using CSDL (Preliminary Report)

Norman Ramsey and Jack W. Davidson Department of Computer Science University of Virginia Charlottesville, VA 22903

November 24, 1997

#### Abstract

The Zephyr project is part of an effort to build a National Compiler Infrastructure, which will support research in compiling techniques and high-performance computing. Compilers work with source code, abstract syntax, intermediate forms, and machine instructions. By using high-level descriptions of the representations and semantics of these forms, we expect to be able to create compiler components that will be usable with different source languages, front ends, and target machines.

To help deal with multiple machines, we are developing a family of Computer Systems Description Languages (CSDL) to describe properties that are relevant to the construction of compilers and other systems software. The languages describe properties of a machine's instructions or its mutable state, or both. Of particular interest is the description of the semantics of instructions, i.e., their effects on the state of the machine. This report describes our preliminary design of  $\lambda$ -RTL, a CSDL language for specifying instructions' semantics.

We describe the effects of instructions using register transfer lists (RTLs). A register transfer list is a collection of assignments to locations, which represent registers, memory, and all other mutable state. We prescribe a form of RTLs that makes it explicit how to compute the values assigned and on what state the computation depends. The form also makes byte order explicit and provides for instructions whose effects may be undefined.

Because our form of RTLs contains so much information, it is convenient for use by tools, but it would be tedious to write RTLs by hand.  $\lambda$ -RTL, which is based on the  $\lambda$ -calculus and on register transfer lists, is a metalanguage designed to make it easier for people to write RTLs and to associate them with machine instructions. It enables us to omit substantial information from hand-written specifications; the  $\lambda$ -RTL translator infers the missing information and puts the resulting RTLs into canonical form.  $\lambda$ -RTL also provides a "grouping" construct designed to help specify large groups of similar instructions.

We are still designing  $\lambda$ -RTL. This report presents a short overview of  $\lambda$ -RTL, followed by examples. The examples include definitions of basic operators, which we believe will be useful for describing a wide variety of machines, as well as excerpts from descriptions of the SPARC and Pentium. We have chosen excerpts that illustrate features which are characteristic of these particular machines; for example, we show a model of SPARC register windows, and we show how  $\lambda$ -RTL can help manage the complexity of the Pentium instruction set.

Both the machine descriptions and  $\lambda$ -RTL itself are under development, so this report is a snapshot of a work in progress. We issue it now to solicit feedback both on our overall approach and on the details of  $\lambda$ -RTL. Please send feedback by electronic mail to zephyr-investigators@virginia.edu.

# Contents

| 1 | Overview of CSDL                                        | 1  |

|---|---------------------------------------------------------|----|

|   | Machine descriptions for machine-level tools            | 1  |

|   | Core aspects for CSDL                                   |    |

|   | Instructions                                            | 2  |

|   | Storage                                                 |    |

|   | Combining instructions and storage                      | 3  |

|   | Languages in the CSDL family                            | 4  |

| _ |                                                         |    |

| 2 | Register Transfer Lists                                 | 6  |

|   | Form of RTLs                                            | 6  |

|   | Types in RTLs                                           |    |

|   | RTL languages and translation                           |    |

|   | Interpretations of RTLs                                 | 8  |

| 3 | Using $\lambda$ -RTL to specify register transfer lists | 10 |

| • | Design considerations                                   |    |

|   | Restrictions eased in $\lambda$ -RTL                    |    |

|   | Implicit fetches                                        |    |

|   | Slices                                                  |    |

|   |                                                         |    |

|   | Implicit aggregation                                    |    |

|   | Overview of $\lambda$ -RTL                              |    |

|   | Top-level declarations                                  |    |

|   | Inner declarations                                      |    |

|   | Expressions                                             |    |

|   | Grouping                                                |    |

|   | Lexical conventions                                     |    |

|   | The initial basis                                       | 15 |

|   | Style                                                   | 16 |

|   | Differences between $\lambda$ -RTL and Standard ML      |    |

| 4 | Basic RTL operators                                     | 18 |

| - | 4.1 Building RTLs                                       |    |

|   | 4.1 Building RTES                                       |    |

|   |                                                         |    |

|   | 4.3 Integer arithmetic and comparisons                  | ∠l |

|    | 4.4 Logical operators                 | 21          |  |  |  |  |

|----|---------------------------------------|-------------|--|--|--|--|

|    | 4.5 Byte order                        | 22          |  |  |  |  |

|    | 4.6 Undefined effects                 | 22          |  |  |  |  |

|    | 4.7 Floating-point arithmetic         | 22          |  |  |  |  |

| 5  | Describing the SPARC, Version 8       |             |  |  |  |  |

|    | 5.1 Storage spaces                    | $2^{2}$     |  |  |  |  |

|    | Integer Registers                     | $2^{\cdot}$ |  |  |  |  |

|    | Integer Unit control/status registers | 2           |  |  |  |  |

|    | 5.2 SPARC instructions                | 2           |  |  |  |  |

|    | SPARC addresses and operands          | 20          |  |  |  |  |

|    | Load instructions                     | $2^{\circ}$ |  |  |  |  |

|    | Store instructions                    | 2i          |  |  |  |  |

|    | Swapping load-store instructions      | 2i          |  |  |  |  |

|    | Save and restore instructions         | 2           |  |  |  |  |

|    | Logical instructions                  | 3           |  |  |  |  |

|    | Add instructions                      | 3           |  |  |  |  |

|    | Multiply instructions                 | 3           |  |  |  |  |

|    | Branch on integer condition codes     | 3           |  |  |  |  |

|    | Call and jump instructions            | 3           |  |  |  |  |

|    | 5.3 Putting it all together           | 3           |  |  |  |  |

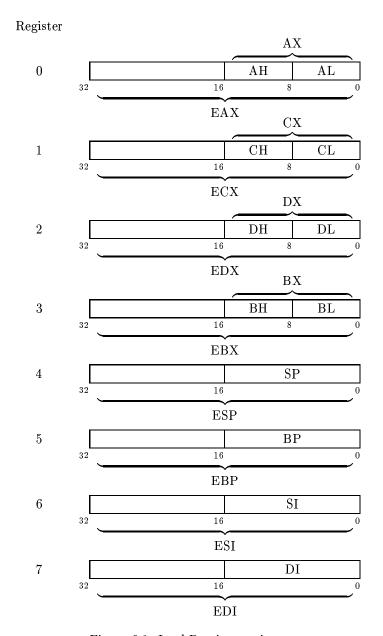

| 6  | Describing the Intel Pentium          | 30          |  |  |  |  |

|    | 6.1 Storage spaces                    | 3           |  |  |  |  |

|    | Registers                             | 3           |  |  |  |  |

|    | Effective addresses                   | 3           |  |  |  |  |

|    | Instructions                          | 4           |  |  |  |  |

| 7  | Index 4                               |             |  |  |  |  |

| -  | 7.1 List of chunks                    | 4           |  |  |  |  |

|    | 7.2 Identifier index                  | 4           |  |  |  |  |

| D. | ferences                              | 49          |  |  |  |  |

### Chapter 1

### Overview of CSDL

# Machine descriptions for machine-level tools

Special-purpose and general-purpose computers are designed at a rapid pace, and software tools and technology don't always keep up. The tools we need include not only the compilers, assemblers, linkers, and debuggers familiar to all programmers, but also less familiar tools, like profilers, tracers, test-coverage analyzers, and general code-modification tools. Most of these tools must work with machine instructions.

Machine-dependent detail makes it hard to build machine-level tools. For many years, compilers have used machine descriptions to capture such detail. Machine descriptions isolate target-specific information so that it can easily be examined and changed. Despite their successful use in compilers, machine descriptions are seldom used to build other systems software. Descriptions used in compilers are hard to reuse because they typically combine information about the target machine with information about the compiler. For example, "machine descriptions" written using tools like BEG (Emmelmann, Schröer, and Landwehr 1989) and BURG (Fraser, Henry, and Proebsting 1992) are actually descriptions of code generators, and they depend not only on the target machine but also on a particular intermediate language. In extreme cases (e.g., gcc's md files), the description formalism itself depends on the compiler.

We believe we can simplify construction of compilers and other machine-level tools by developing description techniques that separate machine properties from compiler concerns. We expect this capability to be useful in a National Compiler Infrastructure because it will lead to a back-end infrastructure that should be usable not only with many different target machines, but also with different source languages, front ends, and intermediate languages.

Some existing languages for machine description, like VHDL (Lipsett, Schaefer, and Ussery 1993) and Verilog (Thomas and Moorby 1995) do describe only properties of the machine, but they are at too low a level, describing implementations as much as architectures. These description languages require too much detail that is not needed to build systems software.

We are designing a family of Computer Systems Description Languages (CSDL) to support a variety of machine-level tools while remaining independent of any one in particular. We have several goals for CSDL:

• Descriptions should be composed from simple components. Each component should describe, as much as possible, a single aspect of the target machine. Such aspects might include calling conventions, representations of instructions, pipeline implementations, memory hierarchy, or other properties. It should not always be necessary to describe aspects completely. For example, most compilers use only a subset of the instructions available on a particular

machine, and a compiler writer should be required to describe only that subset.

- An application writer should be able to derive useful tools not only when the components describing individual aspects are incomplete, but also when not all aspects are described. An application writer should not have to describe aspects of the machine unless the information is needed to build his application. For example, an application writer working entirely at the assembly-language level or above should not have to describe binary representations of instructions. Someone writing a garbage collector might need to describe the stack-frame layouts determined by a calling convention, but he should not have to describe the instructions used in the calling sequences that establish those layouts.

- Components, especially those describing "core aspects," should be reusable. For example, writers of all specifications should benefit from having a common formalization of what it means to be a "SPARC instruction supported by the bare hardware."

CSDL forms a family of languages because all family members have the same view of two core aspects of machines: instructions and state. This report explains the CSDL view of these core aspects, and it presents a rationale for and examples of the most important member of the CSDL family, which describes the semantics of machine instructions.

### Core aspects for CSDL

To identify core aspects to be used throughout the CSDL family, we examined descriptions used to help retarget a variety of systems-level tools. These tools included an optimizer (Benitez and Davidson 1988), a debugger (Ramsey and Hanson 1992), an instruction scheduler (Proebsting and Fraser 1994), a call-sequence generator (Bailey and Davidson 1995), a linker (Fernández 1995), and an executable editor (Larus and Schnarr 1995). Cursory inspection showed no single common aspect of

a machine used in descriptions for all of these tools, but a closer look revealed that all the descriptions refer either to the machine's instruction set or to its storage locations, and some to both. For example, the specifications used by the scheduler and linker refer only to the machine's instructions and the properties thereof. The specifications used in the call-sequence generator and in the debugger's stack walker refer only to storage, explaining in detail how values move between registers and memory. The specifications used in the optimizer and the executable editor refer both to instructions and to storage, and in particular, to how instructions change the contents of storage. From these observations, we have chosen to require that languages in the CSDL family refer to instructions, storage, or both, and that they use the models of instructions and storage presented below.

#### Instructions

The CSDL model of an *instruction set* is a list of instructions together with some identifying information about their operands. Although instruction names in assembly languages are typically overloaded, CSDL requires instructions to have unique names, because tools often need uniquely named code for each instruction in an instruction set. For example, an assembler might use a unique C procedure to encode each instruction, or an executable editor might use a unique element of a C union to represent an instance of each instruction.

An individual instruction is viewed as a function or constructor that, when applied to operands, produces something interesting: a binary representation, an assembly-language string, a semantics, etc. Instruction descriptions that use the CSDL core will include the names and types of the operands of each instruction. Types will include integers of various sizes, but it will also be possible to introduce new types to define such machine-dependent concepts as effective addresses. Values of these new types may be created by applying suitable constructors; for example, Chapter 6 shows how a Pentium effective address may be formed by applying any of

9 constructors, each one representing a different addressing mode.

The structure defined by CSDL constructors and their operands can be viewed as a discriminatedunion type. It is also equivalent to an ASDL grammar (Wang et al. 1997), without recursion, in which the start symbol is "instruction," other nonterminals refer to machine-level concepts like "effective address" or "integer-instruction operand," and terminal symbols are defined by integers or addresses. This structure is a simplification of the "constructor" from the Specification Language for Encoding and Decoding (SLED) of the New Jersey Machine-Code Toolkit (Ramsey and Fernández 1997). It is determined by the machine, independent of any tool, so it should be useful in any specification language that deals with individual machine instructions. For example, the nML machine-description language (Fauth, Praet, and Freericks 1995) uses this structure, although nML is otherwise quite different from SLED.

#### Properties of instructions

Experience with the New Jersey Machine-Code Toolkit shows that many applications can be built from specifications that discuss only instructions and their properties, with no reference to storage. Such applications include assemblers and disassemblers, as well as code generators that work by pattern matching on the names of instructions.

We specify properties of instructions in a compositional style, so instructions' properties are functions of the properties of their operands. We formalize that style using attribute grammars. For example, assembly-language representations of instructions can be computed as synthesized attributes, where the attributes are strings. Binary representations can also be computed as attributes, where the attributes are SLED "patterns." Attributes readily support machines like the 68000 family, in which the representations of effective addresses depend on context.

#### Storage

The CSDL model of a *storage space* is a sequence of mutable cells. A storage space is like an array; cells are all the same size, and they are indexed by integers. For example, a typical microprocessor has a memory made up of 8-bit cells (bytes) and a register file made up of 32-bit cells. The number of cells in a storage space may be left unspecified.

The state of a machine can be described as the contents of a collection of storage spaces. We use storage spaces to model main memory, general-purpose registers, special-purpose registers, condition codes, and so on.

Experience with CCL, a Calling Convention Language (Bailey and Davidson 1995), shows that applications can be built from specifications that discuss only storage, with no reference to instructions. For example, calling conventions can be described by discussing the placement of parameters in storage cells and the the effects of calls and returns on storage. From a CCL description one can generate procedure prologs and epilogs in a compiler, and one can also generate code to test compilers' implementations of calling conventions (Bailey and Davidson 1996). One might be able to derive stack walkers or exception-handling code from similar descriptions. A garbage collector may need to know which locations in storage can contain pointers; this is a property of an application, not of a machine, but it can be described using the CSDL storage core. (We want to describe application properties as well as machine properties, but we want to keep them separate.)

Languages in the CSDL family may refer to individual *locations*. Ways of writing locations may vary, but each one must resolve to a name of a storage space and an integer offset identifying a cell within that storage space.

# Combining instructions and storage

An architecture manual tells programmers what constitutes the state of the processor, and it lists instructions and their operands, but the most important thing it does is explain the semantics of each instruction in terms of that instruction's effects on the state of the processor. Many applications can be built based on this information, but some require more detail than others. For example,

- Information about control flow is enough to build control-flow graphs.

- Information about calling conventions may be enough to recognize procedure calls and returns.

- Information about locations read and written is enough to build data-flow graphs. Such graphs, together with the ability to match individual instructions, may suffice to build code-editing tools like EEL (Larus and Schnarr 1995) or ATOM (Srivastava and Eustace 1994).

- Information about register-transfer semantics is enough to build code improvers in the style of PO (Davidson and Fraser 1980), vpo (Benitez and Davidson 1988), and gcc (Stallman 1992). These code improvers work by pattern matching, so they need not know what all of the register-transfer operators do. They do, however, need at least a partial semantics, to perform strength reduction, constant folding, and similar transformations.

- To build a code generator, one needs to know more about the operators used in the register transfers. In particular, one needs to know enough so that one can find a sequence of instructions to implement each operation in the compiler's intermediate code. It is sufficient to know that the intermediate code and the instructions compute the same operation; one need not know exactly what the operations do to the bits.

- To build an emulator like SPIM (Larus 1990) or a binary translator like FX!32 (Thompson 1996), one needs enough information about the operations in the register transfers to interpret the the effect of each register transfer on each bit of the processor's state.

We believe that these applications and more can be served by providing register-transfer semantics for instructions. The effect of a particular instruction can be specified as a register-transfer list (RTL), which modifies storage cells. As with other properties of instructions, the RTL is computed using an attribute grammar.

In principle, a single register-transfer description could support all of the different uses above. A single RTL could be given different interpretations, depending on its intended use. We believe we can support this mode of specification by prescribing a rigid form for RTLs, while supplying suitable abstraction mechanisms for use within that form. Abstraction mechanisms support our goals of enabling application writers to leave irrelevant facts unspecified. For example, we want to make it easy to write an RTL that means "register rd is assigned an unspecified function of registers rs and rt."

#### Languages in the CSDL family

We consider SLED, for specifying representations of instructions (Ramsey and Fernández 1997), and CCL, for specifying calling conventions (Bailey and Davidson 1995), to be the first languages in the CSDL family. We are developing a new language,  $\lambda$ -RTL, for specifying instruction semantics. We expect that CSDL will expand to include languages for specifying properties of memory hierarchies and of pipelines. Indeed, the simple functional-resource languages of Proebsting and Fraser (1994) and Bala and Rubin (1995) fit nicely into the CSDL framework.

This report focuses on  $\lambda$ -RTL. The report does not give a specification or definition of  $\lambda$ -RTL, because  $\lambda$ -RTL is not sufficiently developed for a specification or definition to be worthwhile. Instead, this report presents some essential properties of  $\lambda$ -RTL, and it gives examples of machine specifications using the current, imperfect version. Chapter 2 describes the form of register transfer lists used in  $\lambda$ -RTL. Chapter 3 presents  $\lambda$ -RTL and discusses its translation into RTLs. Chapter 4 describe some basic content which fits into that form, and which

we believe will be useful for describing many machines. Chapters 5 and 6 present excerpts from  $\lambda$ -RTL descriptions of the SPARC and Pentium processors, respectively.

### Chapter 2

## Register Transfer Lists

Computer scientists have used register transfers in many different forms. For  $\lambda$ -RTL, we have chosen a form designed for use by tools, not by people. We have therefore insisted that as much information as possible be explicit in the RTL itself. Under our current plan,

- RTLs are represented as trees.

- All operators are fully disambiguated, e.g., as to type and size.

- There is no aliasing of locations.

- Fetches are explicit, as are changes in the size or type of data.

- Stores are annotated with the size of the data stored.

- Explicit tree nodes specify byte order. More generally, they specify how to transfer data between storage spaces of different granularity.

- RTL should be a typed representation. We plan to generate RTL type checkers from CSDL specifications. Optimizations and other transformations that are intended to preserve semantics should also preserve the property of being well typed. Typing is a good way to catch bugs in optimizers (Morrisett 1995).

The form of RTLs proposed here may be suitable not just for specification, but also for use in the implementations of compilers, binary translators, and other tools.

Figure 2.1: ASDL specification of the form of RTLs

#### Form of RTLs

Figure 2.1 uses the Zephyr Abstract Syntax Description Language (Wang et al. 1997) to show the form of RTLs. A register transfer list is a list of guarded effects. Each effect represents the transfer of a value into a storage location, i.e., a store operation. The transfer takes place only if the guard (an expression) evaluates to true. Locations may be single cells or aggregates of consecutive cells within a storage space. Values are computed by expressions without side effects, which simplifies analysis and transformation. These expressions include integer constants, fetches from locations, and applications of RTL operators to lists of expressions. Effects in a list take place simultaneously, as in Dijkstra's multiple-assignment statement, so one RTL represents one change of state. This decision makes

it possible to specify swap instructions without having to introduce temporary locations.

Not every effect is a true assignment. A *kill* effect changes the value in a storage location in an undefined way. Kill effects are needed to model such architectural specifications as "the effect of a logical instruction on the AF flag is undefined."

The "kill all" effect in Figure 2.1 kills all of the cells in the given storage space. It is needed to give a semantics to certain phrases of  $\lambda$ -RTL. We haven't demonstrated a need for it yet, but it may be useful to model stores into arbitrary memory locations.

As an example of a typical RTL, consider a SPARC load instruction using the displacement addressing mode, written in the SPARC assembly language as

```

\langle sample \ SPARC \ instruction \rangle \equiv 1d [%sp-12], %i0

```

Although we would not want to specify just a single instance of a single instruction, the effect of this load instruction might be notated in  $\lambda$ -RTL as follows:<sup>1</sup>

```

\langle \lambda \text{-}RTL \ for \ sample \ instruction} \rangle \equiv  $\frac{\pi_1^2}{\pi_2^2} <-- \$m[\pi_1^14] +(^12)]

```

because the stack pointer is register 14 and register i0 is register 24. The corresponding RTL is much more verbose, with the sizes of all quantities identified explicitly, as a fully disambiguated tree:

The various constants labeled with hash marks, like #32, indicate the number of bits in arguments,

results, or data being transferred. Such constants will fit into a generalization of the Hindley-Milner type system (Milner 1978).

Figure 2.2 shows the operators used in this tree. The left child of the STORE is a subtree representing the location consisting of the single register i0, which is register 24. The right-hand child represents a 32-bit word (a big-endian aggregration of four bytes) fetched from memory at the address given by the subtree rooted at ADD. This node adds the contents of the stack pointer (register 14) to the constant -12. The constant is a 13-bit constant, and the SX operator sign-extends it to 32 bits, so it can be added to the stack pointer.

#### Types in RTLs

RTL is intended to be a typed format. The type system is under development, but it is expected to include the following types:

#n bits A value that is n bits wide.

#n loc A location containing an n-bit value.

#n cells One of a sequence of n-bit storage cells, which can be aggregated together to make a larger location, as by the AGGB nodes in the example tree.

bool A Boolean condition.

effect A side effect on storage.

Figure 2.2 uses these types to show the types of the operators used above. We plan to extend Milner's type inference to this system, so that those writing specifications in  $\lambda$ -RTL can omit types and widths. Unlike in ML, type inference alone will not guarantee that terms make sense; in general, it will be necessary to check additional constraints. For example, in the RTL shown above, it would be necessary to check that the signed integer -12 can be represented using 13 bits, and that 32 is a multiple of both 8 and 32.

### RTL languages and translation

Although we have prescribed the form of RTLs, we can't write any RTLs until we choose a set of lo-

<sup>&</sup>lt;sup>1</sup>The ~ in ~12 is a unary minus.

$\mathtt{STORE}: \forall \#n. \#n \, \mathtt{loc} \times \#n \, \mathtt{bits} \rightarrow \mathtt{effect}$ Store an n-bit value in a given location. The type indicates that for any n, STORE #n takes an n-bit location and an n-bit value and produces an effect.  $\texttt{FETCH}: \forall \texttt{\#}n.\texttt{\#}n \, \texttt{loc} \to \texttt{\#}n \, \texttt{bits}$ For any n, FETCH #n takes an n-bit location and returns the n-bit value stored in that location.  $AGGB: \forall \#n. \forall \#w. \#n cells \rightarrow \#w loc$ For any n and w, AGGB #n #w aggregates an integral number of n-bit cells into a w-bit location, making the first cell the most significant part of the new location, i.e., using big-endian byte order. w must be a multiple of n. (w and n are mnemonic for wide and narrow.) LOC 'm':  $\#32 \, \text{bits} \rightarrow \#8 \, \text{cells}$ Given a 32-bit address, LOC 'm' returns the 8-bit cell in memory referred to by that address. LOC 'r': #5 bits  $\rightarrow \#32$  cells Given a 5-bit register number, LOC 'r' returns the corresponding 32-bit register (a mutable cell).  $\mathtt{ADD}: \forall \mathtt{\#} n. \mathtt{\#} n \ \mathtt{bits} \times \mathtt{\#} n \ \mathtt{bits} \to \mathtt{\#} n \ \mathtt{bits}$ For any n, ADD #n takes two n-bit values and returns their n-bit sum. Carry and overflow are ignored.  $SX : \forall \#n. \forall \#w. \#n \text{ bits} \rightarrow \#w \text{ bits}$ For any n and w, SX #n #w takes an n-bit value, interprets it as a two's-complement signed integer, and sign-extends it to produce a w-bit representation of the same value. w must be greater than n.  $\mathtt{CONST}: \forall \#n.\langle \mathtt{constant} \rangle \to \#n \, \mathtt{bits}$ For any n, CONST #n k represents the n-bit constant k. k must be representable in n bits. The same k could be used with dif-

Figure 2.2: Some RTL operators and their types

ferent ns.

cations and a set of RTL operators. These choices define an RTL language. Any specification written in  $\lambda$ -RTL can introduce new storage spaces (and therefore new locations) and new RTL operators, determining an RTL language for use in that specification.

For use during compilation, we restrict RTLs to a subset of a full RTL language. Each RTL used in a back end based on the *vpo* optimizer (Benitez and Davidson 1988) must satisfy the *vpo* invariant for the target machine. An RTL satisfies that invariant if and only if it can be represented in a single instruction on the target machine. All RTLs manipulated by *vpo* satisfy this invariant, so *vpo* can stop and emit machine code at any time. We use the name X-RTLs refer to the set of RTLs satisfying the *vpo* invariant for machine X.

### Interpretations of RTLs

One reason we restrict the form of RTLs is to limit their possible meanings or interpretations. For example, access to the mutable state of a machine is available only through the fetch and store operations built into the RTL form, so we can easily tell what state is changed by an RTL and how that change depends on the previous state. Researchers and tools working with our form of RTLs have freedom to define interpretations of only two parts of the RTL form: aggregations and operators.

RTL aggregations specify byte order. More generally, aggregations make it possible to write an RTL that stores a w-bit value in (or fetches a w-bit value from) k consecutive n-bit locations, provided that w = kn. Such an aggregation has type  $\#n \text{ cells} \to \#w \text{ loc}$ , and its interpretation must be a bijection between a single w-bit value and k n-

bit values. Moreover, when w=n, the bijection must be the identity function. Storing uses the bijection, and fetching uses its inverse, making it possible to combine RTLs using forward substitution. Little-endian and big-endian aggregations will be built into  $\lambda$ -RTL, as will an "identity aggregation" that is defined only when w=n. We imagine that users could define other aggregations by giving systems of equations, as in Ramsey (1996).

RTL operators must be interpreted as pure functions on bit vectors. Consequently, the result of applying an RTL operator must not depend on processor state; the operator must give the same answer every time. Chapter 4 presents a collection of RTL operators that we expect can be used to describe many different machines. We don't expect this set to be complete; on the contrary, we expect that any machine description written in  $\lambda$ -RTL will introduce a handful of new RTL operators which will be unique to that machine.

### Chapter 3

# Using $\lambda$ -RTL to specify register transfer lists

Bare RTLs are both spartan and verbose. Expressions do not include if-then-else, so conditionals must be represented by using guards on effects. There is no expression meaning "undefined;" assignments of undefined values must be specified using a kill effect. These restrictions, and the requirement that operations be fully disambiguated, make RTLs a form that is good for manipulation by tools but not so good for writing specifications.

$\lambda$ -RTL is a metalanguage that enables specification writers to attach RTL trees to SLED-like constructors without having to write everything explicitly. Eventually,  $\lambda$ -RTL will be a higher-order, strongly typed, polymorphic, pure functional language based largely on Standard ML (Milner, Tofte, and Harper 1990). A variation on the Hindley-Milner type system will make it possible to write flexible, type-safe functions without having to write types explicitly. The current implementation of  $\lambda$ -RTL is, however, untyped.

### Design considerations

We have drawn on our experience with SLED (Ramsey and Fernández 1997) to identify mechanisms and properties that are desirable in any CSDL language, including  $\lambda$ -RTL. These include:

• Use of constructors to provide an abstract view of the machine's instruction set, and use of at-

tributes to specify properties of instructions. These mechanisms are close kin to attribute grammars and to the denotational approach to semantics, both of which have long histories of utility.

- Use of default, unnamed attributes (for example, binary representation or default constructor type), sometimes supported by special syntax. By providing a default case that does not have to be named, we can unclutter specifications. For example, when we refer to an operand of type Address, the location designated by that effective address should be the default meaning.

- Use of a specialized sublanguage for defining attributes. SLED uses patterns to specify binary representations;  $\lambda$ -RTL uses the prescribed forms of RTLs, to be augmented by a sophisticated type system.

- Language constructs that help eliminate repetition by permitting simultaneous description of many instructions at once. Such constructs reduce the number of opportunities for errors, and they help keep specifications concise and readable. λ-RTL includes two such constructs: first class functions, and a generalization of SLED's grouping construct, which itself is based on Icon generators (Griswold 1982).

• Formal notation that matches informal descriptions found in architecture manuals. The architecture manual is the standard model of the machine that is shared by all tool builders, so this close match not only helps people read specifications, it helps them write correct specifications.  $\lambda$ -RTL enables users to define their own infix operators, and Chapters 4, 5, and 6 show how we have used this capability to create an ISP-like notation for RTLs.

We expect to be able to analyze  $\lambda$ -RTL specifications for internal consistency and "plausibility." For example, it should be possible to identify cases in which a register number is mistakenly used as an immediate value instead of as an offset into the storage space modeling the register file.

#### Restrictions eased in $\lambda$ -RTL

$\lambda$ -RTL descriptions are easier to write than bare RTLs in three ways: grouping and higher-order functions can help eliminate repetition, the type system will eliminate the need to write sizes explicitly, and  $\lambda$ -RTL relaxes several of the restrictions on the form of RTLs. In particular,

- In  $\lambda$ -RTL, it is not necessary to write fetches explicitly.

- λ-RTL gives the illusion that bit slices (subfields) are locations that can be assigned to.

- λ-RTL gives the illusion that aggregates of cells are locations that can be assigned to, and it is not usually necessary to write aggregations explicitly.

#### Implicit fetches

Most programmers are used to writing x := x + 1 and having the x on the left denote a location while the x on the right denotes the value stored in that location. Typical compilers identify "lvalue contexts" and "rvalue" contexts and automatically insert fetches in rvalue contexts. We do the same in

$\lambda$ -RTL, but instead of using syntax to identify the contexts, we intend to use types.

We use types and not syntax because  $\lambda$ -RTL has no special syntax for writing RTL assignments. Instead of an assignment syntax,  $\lambda$ -RTL provides a built-in store function that accepts a location and a value and produces an effect. Any user-defined function might result in a call to the built-in store, so we have to recognize the right and left contexts by their types. Thus, if a location is used where a value is expected, we insert a fetch.

$\lambda$ -RTL does almost everything with functions, not syntax, so the writer of a specification can normally redefine the meaning of a notation by defining a new function with the same name. strategy doesn't work with implicit fetches because there is no explicit notation associated with a fetch. We want users to be able to control the meanings of these fetches, however, because many machines have resources that are almost, but not quite, sequences of mutable cells. For example, SPARC registers can be viewed as a collection of 32 mutable cells, except that register 0 is not mutable and always contains 0. We would like users to be able to define special meanings for "fetch from register 0" and "store into register 0" so the rest of the specification can pretend that the registers are an ordinary storage space. We do so by permitting users to attach fetch and store methods to each storage space. Methods not given explicitly default to the standard fetch and store operators. Sample fetch and store methods for the SPARC are shown on page 25. If we wanted, we could use fetch and store methods to describe the true implementation of SPARC registers, in which "registers" 8 through 31 denote locations accessed indirectly through the registerwindow pointer (CWP).

#### Slices

Many machine instructions manipulate fragments of a word stored in a mutable cell. For example, some machines represent condition codes as individual bits within a program status word. Many machines have instructions that, for example, assign to the least-significant 8 bits of a 32-bit register.

To make it easy to specify such instructions,  $\lambda$ -RTL creates the illusion that a sub-range or "slice" of a cell can be a location in its own right, one that is a suitable argument for a fetch or store operation. This illusion helps keep machine descriptions readable; for example, an effect that sets the SPARC overflow bit simply assigns to it, hiding the fact that it is buried in a program status word that has to be fetched, modified, and stored.

$\lambda$ -RTL uses a special syntax for slices because the slicing operation is overloaded; it can be applied to locations or to values. Examples of the syntax include

| x@[k]                       | Bit $k$ of $x$ . By default,          |

|-----------------------------|---------------------------------------|

|                             | bit 0 is the least significant        |

|                             | bit. A future version of $\lambda$ -  |

|                             | RTL may make it possible              |

|                             | to change the numbering.              |

| $x 0 [k_1 \dots k_2]$       | Bits $k_1$ through $k_2$ of $x$ , in- |

|                             | clusive.                              |

| $x @ [k 	ext{ bits at } e]$ | A $k$ -bit slice of $x$ , with the    |

|                             | least significant bit at $e$ .        |

k's denote integer constants, e's denote expressions, and x's may denote values or locations. In all cases the size of the slice is known statically, so its type can be computed automatically. We use the Greek letter  $\sigma$  to stand for any of these slice specifications.

Given a slice specification  $\sigma$ , SLICE $_{\sigma}$  is an overloaded function that maps locations to locations or values to values. The illusion that slices are locations is implemented by rewriting, according to the following rules:

```

\begin{array}{lll} \mathtt{FETCH}(\mathtt{SLICE}_\sigma\ l) & \mapsto & \mathtt{SLICE}_\sigma\left(\mathtt{FETCH}\ l\right) \\ \mathtt{SLICE}_\sigma\ l \leftarrow n & \mapsto & l \leftarrow \mathtt{bitInsert}_\sigma\left(\mathtt{FETCH}\ l, \, n\right) \end{array}

```

where l is a location and n is a value. After the rewriting, all slices operate on bit vectors, and all fetches and stores operate on true locations. Invocation of user-defined fetch and store methods takes place after the rewriting of slices. This ordering makes it possible to use fetch and store methods to define cell-like abstractions, while ensuring that the meaning of slicing is always consistent with respect to such abstractions.

#### Implicit aggregation

$\lambda$ -RTL provides the special syntax \$space[offset] for references to mutable cells. The offset can be an arbitrary expression, but the space must be a literal name, so that  $\lambda$ -RTL can identify the storage space and use appropriate fetch and store methods. To make this cell a location,  $\lambda$ -RTL applies an aggregation, which is also associated with the storage space as a method. The default method is the identity aggregation, which permits only "aggregates" of a single cell.

When little-endian, big-endian, or other aggregations are used,  $\lambda$ -RTL will infer the size of the aggregate. We have not yet determined the rules to be used for the inference, but we hope at least to support the automatic inference that four 8-bit bytes must be aggregated to form a value that goes into a 32-bit register.

The implementation of  $\lambda$ -RTL used in subsequent chapters does not support aggregation.

#### Overview of $\lambda$ -RTL

From the point of view of external tools, the output of a  $\lambda$ -RTL specification is a set of bindings of values to attributes of constructors. The part of  $\lambda$ -RTL used to specify values is a pure functional language without recursion. The implementation used in this report is untyped, but  $\lambda$ -RTL will eventually use a polymorphic typed calculus. Many features of  $\lambda$ -RTL are inspired by Standard ML.

To describe syntax, we use an EBNF grammar with standard metasymbols for {sequences}, [optional constructs], and (alternative | choices). We use large metasymbols to help distinguish them from literals. Terminal symbols given literally appear in typewriter font. Other terminal symbols and all nonterminals appear in *italic* font. Excerpts from the grammar begin with the name of a nonterminal followed by the  $\Rightarrow$  ("produces") symbol.

A  $\lambda$ -RTL specification is a sequence of *structures*.  $\lambda$ -RTL uses structures to organize the name space of values, and structures will play a role in a modules system for  $\lambda$ -RTL. A value **x** declared in a struc-

ture S is visible within S as just x, but outside S it can only be referred to as S.x. Structures are written

```

structure \Rightarrow structure struct-name is struct \{declaration\} end

```

Constructors and storage spaces occupy their own individual name spaces, which are flat. RTL operators are also expected to occupy a separate, flat name space, but within  $\lambda$ -RTL they are not distinguished from other kinds of values. Eventually,  $\lambda$ -RTL will check that the same name is not used to declare distinct RTL operators in two different structures.

Declarations are either top-level or inner declarations. Inner declarations may appear anywhere, but top-level declarations may appear only outside of function and value definitions. Top-level declarations appear only in contexts that guarantee they will be evaluated exactly once.

#### Top-level declarations

$\lambda$ -RTL's top-level declarations may introduce structures, locations, storage spaces, RTL operators, or bindings to attributes of constructors.

Storage spaces are introduced by storage; they name the storage space, give its granularity (width of an individual cell) and size (number of cells), and possibly fetch, store, or aggregation methods.

RTL operators are introduced by:

```

declaration ⇒

rtlop (operator-name | [ {operator-name} ])

For example,

rtlop bit

rtlop [= <>]

```

introduces three new RTL operators.

In the current implementation of  $\lambda$ -RTL, rtlop introduces an arbitrary, abstract value. Because it is the only abstraction mechanism available, it is sometimes put to odd uses. A future version of  $\lambda$ -RTL will require that the type of the RTL operator(s) be specified.  $\lambda$ -RTL will support polymorphic operators applicable to arguments of any

size. This parametric polymorphism will let programmers use to use the same operator to add both 16- and 32-bit integers.  $\lambda$ -RTL will not support overloading, so a different operator will be required to add floating-point values.

Attribute bindings are introduced as follows:

```

declaration ⇒

attribute of {constructor is expression}

attribute ⇒

default attribute of

| attribute (attribute-name | default) of

constructor ⇒

opcode ( [operand-name { , operand-name } ] )

```

Each expression must be terminated by a newline; if an expression doesn't fit on one line, it must contain an open parenthesis or brace so that the  $\lambda$ -RTL compiler knows to continue to the closing delimiter.

For example,

```

default attribute of

nop() is do_nothing

```

defines the effect of a no-op.

An expression bound to an attribute must denote a legal fragment of RTL; in the current implementation, this means a value, a location, or an RTL. More precisely, an expression must denote an RTL template. An RTL template becomes a fragment of RTL when suitable fragments of RTL are substituted for the constructor's operands. An RTL template is an RTL, except that

- Names of constructor operands may be used to stand for RTL expressions. (Eventually we hope to use names of operands to stand for locations as well as values, but the current implementation does not support this usage.)

- Tuple or record selections from constructor operands may be used to stand for RTL expressions.

- Vectors of RTL expressions subscripted by constructor operands may be used in place of RTL expressions.

A tuple or record containing RTL templates is also considered an RTL template. The most notable consequence of these rules is that no expression whose normal form contains a  $\lambda$ -abstraction is an RTL template;  $\lambda$ -abstractions must be applied to arguments.

Eventually there will be a precise, formal definition of RTL template.

#### Inner declarations

Inner declarations may appear anywhere a top-level declaration may appear, and they may also appear in let-expressions, where they are the only kind of declaration permitted. Their typical usage is to bind local values in function bodies. Inner declarations include value bindings, function bindings, and fixity declarations. Value and function bindings are written as

```

\begin{array}{c} \textit{declaration} \Rightarrow \\ & \texttt{val} \ \textit{value-spec} \ \texttt{is} \ \textit{expression} \\ & | \ \texttt{fun} \ \textit{value-spec} \ \textit{argument-pattern} \ \texttt{is} \ \textit{expression} \\ & \textit{value-spec} \ \Rightarrow \ \texttt{name} \ \middle| \ \middle[ \ \left\{ \ \texttt{name} \right\} \ \middle] \end{array}

```

The square brackets in value-spec represent  $\lambda$ -RTL's grouping mechanism, in which the expression actually denotes a sequence of values, and each value in the sequence is bound of the corresponding name on the left.

As examples, consider

```

val do_nothing is RTL.SKIP

fun bool n is n <> 0

val [eq ne] is [(=) (<>)]

```

$\lambda$ -RTL supports user-defined infix operators with arbitrarily many levels of precedence. Precedence levels range from 999, which represents the highest possible precedence (tightest binding) for an infix operator, down to the most negative integer on the machine (loosest binding). The syntax is

```

declaration ⇒

(infix1 | infixr | infixn) precedence value-spec

| nonfix value-spec

```

Infix operators must be declared to be left-associative, right-associative, or non-associative with other

operators of the same precedence. For example, we can make equality testing infix and non-associative using

```

infixn 5 [= <>]

```

A single instance of an infix operator can be made "nonfix" (treated as an ordinary value) by enclosing it in parentheses. The nonfix declaration makes this behavior permanent.

#### Expressions

$\lambda$ -RTL expressions include records, tuples, integers, conditionals, and functions ( $\lambda$ -abstractions). As in ML, the juxtaposition of two expressions indicates function application, and function application has higher precedence than any infix operator. Figure 3.1 shows the syntax for expressions.

#### Grouping

A group may appear in place of an expression anywhere in  $\lambda$ -RTL. Whereas an expression denotes a single value, a group denotes a sequence of values. All operations except binding distribute over the group, so if the expression in a declaration contains a group, then that expression denotes a sequence of values, no matter how deeply nested the group is. The most common operations to distribute over a group are function application and tuple formation.

The usual syntax for a group is a list of expressions in square brackets. The expressions need not be of the same type. Ordinary function application is inoperative at the top level of a group, so the group  $[f \ x]$  is a group containing two values, as is  $[f \ (x)]$ . To use function application or infix operators within a group, one must include the whole application in parentheses, e.g.,  $[(f \ x)]$  or [(f(x))]. In addition to the usual syntax,  $\lambda$ -RTL provides two kinds of special syntax to create groups of integers. All use square brackets:

```

expression ⇒

[ {expression} ]

| [expression .. expression]

| [expression to expression

[by expression | columns expression]]

```

```

expression \Rightarrow

( expression \{, expression \} )

Tuple

{ member-name is expression {, member-name is expression } }

Record

| [. expression {, expression}] .]

Vector

| let \{declaration\} in expression end

Local declarations

if expression then expression else expression fi

Conditional

Function

expression.member-name

Selection

$ space-identifier [ expression ]

Location

expression @ [slice-specification]

expression expression

Function application

identifier

Named value

literal-constant

Constant

```

Figure 3.1:  $\lambda$ -RTL expressions

In the latter two cases, the constituent expressions must be compile-time constants.

Groups are evaluated left to right, last-in, firstout, so for example the expression

denotes the same sequence of four expressions as

The evaluation rule and the design of groups in general are based on the *generator* mechanism of the Icon programming language (Griswold 1982).

The primary role of groups is to make it easy to specify multiple machine instructions in a single attribute binding. This is done by using *value-spec* (either a single name or a sequence of names in square brackets) to form the opcodes of constructors. Multiple *value-specs* may be used to combine, for example, a group of operations with a group of suffixes. Chapters 5 and 6 have examples.

$$opcode \Rightarrow value\text{-}spec\{ \text{`}value\text{-}spec \}$$

#### Lexical conventions

Like identifiers in ML,  $\lambda$ -RTL identifiers may be alphanumeric or symbolic. An alphanumeric identifier begins with a letter and continues with letters, digits, underscores, and primes. A symbolic identifier is a sequence of the symbols

Such an identifier may begin with any symbol except #.

Identifiers consisting solely of two or more dashes introduce comments; the comment includes the dashes and continues to the end of the line. For example, -- and --- introduce comments, but --> and --\*-- do not. A comment is equivalent to a newline.

An integer literal is a sequence of decimal digits;  $\lambda$ -RTL has no floating-point literals.  $\lambda$ -RTL also supports hexadecimal literals beginning with 0x, octal literals beginning with 0, and binary literals beginning with 0b.

Literals and identifiers preceded by # are intended to be used to represent widths in  $\lambda$ -RTL's forthcoming type system; in the current implementation, they are equivalent to ordinary literals and identifiers.

#### The initial basis

Most of the RTL-specific content of  $\lambda$ -RTL is in the initial basis, i.e., the collection of predefined functions and values. Figure 3.2 shows  $\lambda$ -RTL's initial basis.

Boolean constants:

true Truth false Falsehood

RTL operators and other functions used to create RTLs:

RTL. STORE Takes location and value, produces effect.

RTL.FETCH Fetches value from location.

RTL. SKIP The empty RTL; an effect that does nothing.

RTL.GUARD Takes a Boolean expression and an effect and produces an effect.

RTL.NOT Boolean negation.

RTL.EFFECTS Takes two effects (RTLs) and composes them so they take place simultaneously

(list append on list of effects).

Functions on vectors:

sub Vector subscript, a left-associative infix operator with precedence 5.

Vector.spanning A curried function of two arguments. Vector.spanning x y produces the vector

$[.x, x+1, \ldots, y.].$

Vector.foldr A higher-order function used to visit every element of a vector. Like Vector.foldr

in Standard ML '97.

Figure 3.2:  $\lambda$ -RTL's initial basis

#### Style

$\lambda\text{-RTL}$  provides expressive power with few restrictions. Writers of specifications use the functions in  $\lambda\text{-RTL}$ 's initial basis to create RTLs that correspond to the form prescribed in Chapter 2. Writers can also introduce new RTL operators. This freedom gives us ample scope for experimenting with different styles of description—as well as ample rope with which to hang ourselves. We expect our experiments to lead to a library of useful RTL operators, as well as useful  $\lambda\text{-RTL}$  functions. Chapter 4 gives a preliminary collection of RTL operators.

$\lambda$ -RTL provides no looping or recursion constructs. Loops whose sizes are known in advance can be simulated by using Vector.foldr and Vector.spanning. Because this style will be familiar only to those well versed in functional programming, we expect eventually to provide some syntactic sugar for it.

# Differences between $\lambda$ -RTL and Standard ML

Although  $\lambda$ -RTL is inspired in large part by Standard ML, there are significant differences, which may interest ML programmers. Syntactic differences include:

- The defining connective is is, not =.

- if expressions must be terminated by fi.

- Identifiers declared infix must be explicitly identified as left-, right-, or non-associative. Arbitrarily many levels of precedence are available.

- Dot notation is used to select elements from records as well as from structures.

- Comments begin with an identifier consisting of n dashes, where n is at least 2. Comments end at the end of a line.

There are also some semantic restrictions:

- There are no side effects (mutation, exceptions), so order of evaluation does not matter.

- Functions may not be recursive, so the normal form of all expressions can be computed at compile time.

- There are no datatype constructors. As a corollary, the only patterns used in function definitions are those that match tuples or records.

### Chapter 4

## Basic RTL operators

This chapter describes RTL operators and functions that we expect to be useful for describing many different machines. As we do throughout this document, we use the noweb literate-programming tool (Ramsey 1994) to present examples of  $\lambda$ -RTL. Noweb extracts the code from the same files used to produce this document, so we can run the examples through the  $\lambda$ -RTL compiler and make sure everything compiles.

A noweb file contains explanatory text interleaved with named "code chunks," which contain source code and references to other code chunks. The names of chunks appear italicized and in angle brackets, as in the following C code:

The  $\equiv$  sign indicates the definition of a chunk. Definitions of a chunk can be continued in a later chunk; noweb concatenates their contents. Such a concatenation is indicated by  $a + \equiv$  sign in the definition:

```

18c ⟨summarize the problem 18a⟩+≡

printf("Must process %d files\n", argc-1);

```

noweb adds navigational aids to the document. Each chunk name ends with the number of the page on which the chunk's definition begins. When more than one definition appears on a page, they are distinguished by appending lower-case letters to the page number. When a chunk's definition is continued, noweb includes pointers to the previous and next definitions, written "\$\pi\$18a" and "18c\$." The notation "(18a)" shows where a chunk is used.

Because  $\lambda$ -RTL does not yet have modules, we use noweb to include the chunk  $\langle RTL \ basics \ 19a \rangle$  in our descriptions of the SPARC and the Pentium.

#### 4.1 Building RTLs

$\lambda$ -RTL is intended for building RTLs, not analying them, so it doesn't expose all the structure of RTLs; single effects, guarded effects, and full RTLs (lists of guarded effects) all have the same type effect. The initial basis provides ways to create and combine effects. We define a more compact, infix notation for parts of the basis.

```

19a \langle RTL\ basics\ 19a \rangle \equiv val do_nothing is RTL.SKIP -- type will be effect val --> is RTL.GUARD -- type will be bool * effect -> effect val <-- is RTL.STORE -- type will be #n loc * #n bits -> effect infixr 1 --> infixr 2 <--

```

In the underlying representation, the semantics of these operations is extended to full RTLs in the obvious way. For example, RTL.STORE produces an RTL containing a single effect whose guard is true.

We don't need an explicit FETCH, because fetches are inserted automatically, and we don't need an explicit CONST, because  $\lambda$ -RTL compiles literal constants into RTL CONST nodes.

We use a semicolon to combine simultaneous effects. We plan eventually to have an andthen operator to indicate sequential composition of effects, which would presumably be implemented by forward substitution. Substitution isn't implemented in the current  $\lambda$ -RTL, so we make andthen equivalent to simultaneous effects, even though this semantics for andthen is incorrect.

```

19b \langle RTL\ basics\ 19a \rangle + \equiv val; is RTL.EFFECTS -- type will be effect * effect -> effect val andthen is; infix1 0; infix1 ~1 andthen

```

#### 4.2 Booleans

19c

true, false, and RTL.NOT are the Boolean operators in  $\lambda$ -RTL's initial basis. We prefer to use not to stand for Boolean negation.

```

\langle RTL\ basics\ 19a \rangle + \equiv val not is RTL.NOT

```

For writing other Boolean functions  $\lambda$ -RTL has only if-then-else-fi, which  $\lambda$ -RTL rewrites into suitable guards. We would like to have connectives andalso and orelse, but introducing them presents a choice about level of detail: should they be introduced as new RTL operators, whose semantics must be defined outside of  $\lambda$ -RTL, or should they be defined in terms of the existing  $\lambda$ -RTL primitives? We would like to try both alternatives, because they provide different levels of detail in the generated RTLs.

Eventually,  $\lambda$ -RTL will have mechanisms to support multiple levels of abstraction, probably by using some sort of parameterized modules. For now, we resort to some literate-programming tricks that are equivalent to conditional compilation. noweb can extract this code in two versions, designated **simple** and **full**. Code chunks tagged [simple] and [full] appear only in the corresponding versions, and untagged code chunks appear in both versions.

In the simple version, the boolean connectives are left abstract. In the full version, we give them their standard definitions. The simple version has the advantage that the RTLs are smaller and easier to read, but the disadvantage that the semantics have to be specified elsewhere. In the full version, these connectives are expanded to primitives, so they automatically get their proper semantics.

```

20e ► rtlop [andalso orelse] -- Boolean connectives

Conditional definition.

20b ⟨RTL basics [full] 20b⟩≡

fun andalso (p, q) is if p then q else false fi

fun orelse (p, q) is if p then true else q fi

Conditional definition.

```

No matter what their definitions, we want these connectives to be left-associative infix operators.

In the long run, equality and inequality will probably have to have some built-in semantics, but for now, we leave them abstract.

```

20d \langle RTL\ basics\ 19a \rangle + \equiv rtlop [= <>] infixn 5 [= <>]

```

We have chosen to make inequality a primitive RTL operator, although we could have defined it in terms of equality by writing val <> is (x,y). not (x = y).

We can convert between booleans and bits. Again we have the choice of making things abstract or concrete.

```

20e ⟨RTL basics [simple] 20a⟩+≡

rtlop bit -- type will be bool -> #1 bits -- turn boolean into bit

rtlop bool -- type will be #1 bits -> bool -- turn bit into boolean

20f ⟨RTL basics [full] 20b⟩+≡

fun bit p is if p then 1 else 0 fi

fun bool n is n <> 0

```

### 4.3 Integer arithmetic and comparisons

These operations represent integer arithmetic performed on the bit-vector representation. Multiplication and division come in two flavors. One interprets its operands as unsigned integers; the other interprets its operands as two's-complement signed integers. There are two sets of signed division operators because division may truncate towards  $-\infty$  (divs and mods) or towards 0 (quots and rems). There is, of course, no such distinction for unsigned division.

```

20g \langle RTL\ basics\ 19a \rangle + \equiv rtlop [add subtract neg muls mulu divu modu divs mods quots rems < <= > >=] -- standard arithmetic operators of several different types

```

The intended semantics of add and subtract is "add with carry" and "subtract with borrow." We define shorthands for the common case where carry (or borrow) in is 0 and carry out is uninteresting:

$\triangleleft 20g \quad 21b \triangleright$

```

fun +(n, m) is (add(n, m, 0)).result -- add returns {result, carry}

fun -(n, m) is (subtract(n, m, 0)).result -- subtract returns {result, borrow}

The arithmetic operators obey the usual rules of precedence.

21b ⟨RTL basics 19a⟩+≡

infixl 7 [divs mods quots rems divu modu quotu remu]

infixl 6 [+ -]

infixn 5 [< <= > >=]

```

Comparisons are left abstract instead of being defined in terms of < and =.

We can sign-extend or zero-extend integers. These operators should be polymorphic in the sizes of the arguments and results.

```

\langle RTL\ basics\ 19a \rangle + \equiv rtlop [sx zx] -- type will be #n bits -> #m bits

```

#### 4.4 Logical operators

21a

21c

$\langle RTL \ basics \ 19a \rangle + \equiv$

Most processors offer a variety of bitwise operations on bit vectors, including those shown here.

bitInsert and bitExtract insert into or extract from a w-bit ("wide") value. The thing inserted or extracted is n bits ("narrow"), and the widths of both wide and narrow values are normally inferred by the type system. (We may change the types planned for bitInsert and bitExtract.)

There are instructions that manipulate bit fields whose widths aren't known statically. These computations can't be expressed with bitInsert and bitExtract, because we can't assign a type (width) to the results. But we can define bitTransfer as a combination extraction and insertion, and in fact, this is the way such instructions must behave. Even an instruction that extracts k bits from a 32-bit word, where k is not known until run time, must still insert the result into some storage location of known size—typically a 32-bit word of all zeros.

```

21e \langle RTL\ basics\ 19a\rangle + \equiv rtlop bitTransfer -- {src: {value:#w bits, lsb:#k bits}, dst:{value:#w bits, lsb:#k bits}, width:#j bits} -> #w bits -- extract width bits from src at lsb, insert into dst at lsb

```

Most processors have shift instructions. We could make the shift operations primitive RTL operators, or we could define them in terms of bit transfer.

```

21f \langle RTL \ basics \ [simple] \ 20a \rangle + \equiv rtlop [shl shrl shra]

```

#### 4.5 Byte order

The current implementation of  $\lambda$ -RTL does not support aggregations, but we would like to be able to use them in our sample specifications, so we define both big- and little-endian aggregations to be the identity function.

#### 4.6 Undefined effects

The current implementation of  $\lambda$ -RTL does not support the kill effects. In a later implementation, we plan to use the question mark to stand for an "undefined" value. All  $\lambda$ -RTL functions and RTL operators will be strict in this value, and RTL.STORE(loc, ?) will become RTL.KILL loc. We would like to use the question mark in our example descriptions, even though  $\lambda$ -RTL doesn't yet have the machinery to give it its eventual meaning, so we introduce it as a nullary RTL operator.

```

22c \langle RTL\ basics\ 19a \rangle + \equiv rtlop ? -- type will be #k bits

```

### 4.7 Floating-point arithmetic

Floating-point operations need to come in different families, so for example we could distinguish IEEE 754 floating point from VAX floating point. Right now the name space of RTL operators is flat, so such distinctions are impossible. It nevertheless seems reasonable to put these operators in a structure. Our treatment of floating-point operators is not complete; we only sketch some possibilities.

```

22d \langle RTL\ basics\ 19a \rangle + \equiv 422c structure IEEE754 is struct \langle IEEE\ 754\ floating\ point\ 23a \rangle end

```

We use operators surrounded by slashes to designate floating-point arithmetic operations.

```

23a

\langle IEEE 754 floating point 23a \rangle \equiv

(22d) 23b ⊳

rtlop [/+/ /-/ /*/ /] -- basic floating-point arithmetic

rtlop [fabs fsqrt]

-- special floating-point operators

All these operators will eventually be parameterized by the size (type) of their operands.

When we get a type system, the conversions will be polymorphic in two widths: the argument and result

widths. We may need a whole family of float-to-integer operators in order to account properly for rounding

modes.

23b

\langle IEEE 754 floating point 23a \rangle + \equiv

(22d) ⊲23a 23c⊳

rtlop [i2f f2i]

-- conversions to/from integer.

There are the special values \pm 0 and \pm \infty.

\langle IEEE 754 floating point 23a \rangle + \equiv

23c

(22d) ⊲23b 23d⊳

rtlop [pzero mzero]

-- plus and minus zero

-- type will be #n bits

rtlop [pinf minf]

-- plus and minus infinity -- type will be #n bits

There are NaNs.

23d

\langle \mathit{IEEE} \ 754 \ \mathit{floating} \ \mathit{point} \ 23a \rangle + \equiv

(22d) ⊲ 23c 23e ⊳

rtlop NaN -- type will be function from significand to value

There are four rounding modes required by the standard.

23e

\langle \mathit{IEEE} 754 \mathit{ floating point } 23a \rangle + \equiv

(22d) ⊲ 23d

structure Round is struct

```

rtlop [nearest zero down up] -- what to round toward

end

### Chapter 5

# Describing the SPARC, Version 8

This chapter illustrates  $\lambda$ -RTL by specifying a handful of SPARC instructions. Load and store instructions illustrate the basic techniques used to move data of different sizes. Logical instructions and add instructions show simple groups of computational instructions; each group offers a slightly different treatment of condition codes. Specifications of save and restore instructions illustrate one of several possible treatments of register windows. In this case we have not yet achieved our goal of separating hardware behavior from software conventions; our model of register windows describes the abstraction that is presented by the combination of hardware, calling convention, and operating system.

#### 5.1 Storage spaces

Storage locations manipulated by SPARC instructions include memory and several kinds of registers. We have little to say about memory other than that the machine is byte-addressed and uses big-endian byte order.

```

\langle SPARC\ basics\ 24 \rangle \equiv (35c) 25c \triangleright storage 'm' is cells of 8 bits called "memory" aggregate using bigEndian val bigE is bigEndian -- useful abbreviation

```

We introduce the abbreviation bigE for cases where we want to write aggregation explicitly.

#### Integer Registers

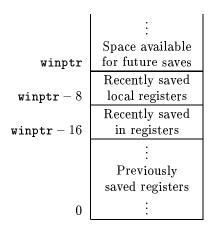

We normally expect that a machine's registers can be modeled as a simple collection of mutable cells, but the SPARC has two architectural features that don't fit this model: an immutable register and register windows. Register 0 is immutable; fetches from register 0 always return zero, and stores into register 0 have no effect. Registers 1–7 are ordinary mutable cells, but registers 8–31 are aliases for locations in a collection of register windows. The register windows are overlapping sets of 16 registers; an implementation may provide from 2 to 32 sets. Bits 0–4 of the processor state register constitute a current window pointer (CWP). When an instruction refers to a register numbered 8–31, the processor uses the CWP and the register number to identify a window of 16 registers and a register in that window. The SPARC save and restore instructions manipulate the CWP, as do traps and returns from traps.

This low-level model would be easy to describe using  $\lambda$ -RTL, but it is not the model used by most compiler writers. Compiler writers seldom need to use register 0 explicitly, because SPARC assembly languages provide "synthetic" instructions that use register 0 as needed. Instead of using the detailed semantics of register windows, compiler writers adhere to the SPARC calling convention, which (with some help from the operating system) gives the illusion of an infinite collection of register windows, and which allocates one register window to each activation of each procedure. The compiler must reserve space on the stack for use as backing store, and it must use save and restore in procedure prologs and epilogs.

$\lambda$ -RTL is not biased toward any particular model of register windows, and in fact it could be used to specify different models which might be useful in different situations. Eventually,  $\lambda$ -RTL will have a modules system that will enable us to create different models, at different levels of abstraction, of such things as SPARC register windows. For this document, we have chosen a fairly abstract model that is convenient for compiler writers. We hide most of the low-level hardware behavior, and we describe registers (except register 0) as a simple collection of mutable cells. Section 5.2 shows the details of the model that are needed to specify the effects of the save and restore instructions.

Dealing with register 0 is fairly simple; there are only two reasonable models. One is the full semantics; the other is a model which specifies only that register 0 is immutable. The simpler model suffices for some compilers, and the resulting RTLs are easier to understand. As in Chapter 4, we use [simple] and [full] to show the two alternatives.

```

25a ⟨SPARC basics [simple] 25a⟩≡

structure Reg is struct

fun fetch n is $r[n]

fun store (n, v) is n <> 0 --> $r[n] <-- v

⟨alias functions for in, out, local, and global registers 29a⟩

end

```

We make register 0 immutable by ensuring that attempts to store into it have no effect. The full semantics also shows that fetches return 0.

```

⟨SPARC basics [full] 25b⟩

structure Reg is struct

fun fetch n is if n = 0 then 0 else $r[n] fi

fun store (n, v) is n <> 0 --> $r[n] <-- v

⟨alias functions for in, out, local, and global registers 29a⟩

end

26b >

26d >

26

```

Conditional definition.

Conditional definition.

25b

In this straightforward model of registers, we use these special fetch and store methods, and we also permit registers to be aggregated into pairs, so we can describe instructions like 1dd.

```

25c ⟨SPARC basics 24⟩+≡

storage

'r' is 32 cells of 32 bits called "registers"

store using Reg.store

fetch using Reg.fetch

aggregate using bigEndian

```

<sup>&</sup>lt;sup>1</sup> "Optimized leaf procedures" may use their caller's register window.

#### Integer Unit control/status registers

This specification gives a bare minimum of information about special registers. It emphasizes condition codes.

```

26a ⟨SPARC basics 24⟩+≡

storage 'i' is 6 cells of 32 bits called "IU control/status registers"

locations

[PSR WIM TBR Y PC nPC] is $i[[0..5]]

Properly speaking, the integer condition codes are part of the processor state register (PSR).

26b ⟨SPARC basics [full] 25b⟩+≡

structure icc is struct

locations [N Z V C] is PSR@[1 bit at [23 22 21 20]]

end (35c) <25c

```

Because references to bits 20–23 of the PSR can be hard to understand, we would like to refer to the condition codes more abstractly. Eventually, the  $\lambda$ -RTL modules system will provide for such abstractions, but for now we resort to dirty tricks. We create a nullary RTL operator for each bit, then bind the names to the locations in an imaginary – space. In the [simple] version, references to, e.g., the N bit come out as \$-[N] instead of \$i[0]@[23].

```

26c ⟨SPARC basics [simple] 25a⟩+≡

structure icc is struct

storage '-' alias bogus is

cells of 32 bits called "bogus space for abstract locations"

rtlop [N Z V C]

locations [N Z V C] is $bogus[[N Z V C]]

end

```

#### 5.2 SPARC instructions

#### SPARC addresses and operands

The SPARC has a simple structure for effective addresses and operands. As far as the hardware is concerned, there are only two addressing modes, depending on whether the immediate bit is used. We've chosen to let the default attribute of the addressing modes be the address, not the location in memory denoted by that address. The address is the value of register rs1, plus either the value of register rs2 or the result of sign-extending a 13-bit immediate value.

```

\langle address \ modes \ and \ operands \ 26d \rangle \equiv

26d

(35c) 26e ⊳

default attribute of

indexA(rs1, rs2)

r[rs1] + r[rs2]

dispA (rs1, simm13)

is $r[rs1] + sx simm13

The rmode and imode constructors produce the values used in operands of type reg_or_imm.

26e

\langle address \ modes \ and \ operands \ 26d \rangle + \equiv

(35c) ⊲26d

default attribute of

rmode (rs2)

is $r[rs2]

imode (simm13) is sx simm13

```

#### Load instructions

27a

27b

The SPARC architecture provides for not one but 256 possible address spaces. By default, load instructions use space 0x0A in user mode and space 0x0B in supervisor mode. The mode is determined by the value of the S bit in the processor state register. Values from other address spaces may be obtained by using the "load from alternate space" instructions, but these instructions are privileged. We omit all this complexity from our description, treating the machine as if it were always in user mode. This omission is partly for simplicity, but partly because  $\lambda$ -RTL does not deal well with numbered collections of storage spaces.