# NATIONAL SCIENCE FOUNDATION WORKSHOP ON HIGH PERFORMANCE MEMORY SYSTEMS FINAL REPORT

Wm. A. Wulf, Steven Moyer

Computer Science Report No. CS-93-35 June 18, 1993

# National Science Foundation Workshop on High Performance Memory Systems

Editors:

Wm. A. Wulf and Steven Moyer

University of Virginia

April 12-13, 1993

## 1 Introduction

During the last decade the performance of microprocessors has increased by a factor of 50% to 100% per year. During the same period the performance of affordable (DRAM) memories has risen less than 10% per year. This growing disparity between processor and memory speeds will be one of the most pressing problems, and hence most influential factors in computer architecture, compilers, and algorithms for at least the next decade.

Given the importance of the overall problem, NSF sponsored a workshop to examine the full spectrum of relevant issues — including chip technology, architecture, caching, new concepts in hierarchy, compiler optimization, programming languages and techniques, and algorithms. Since "memory performance" is not a research area *per se* it does not have a single, separate research community. Although many of the important players know each other and meet pairwise at various conferences, there is no forum for a comprehensive analysis of the problem. The NSF Workshop on High Performance Memory Systems provided such a forum.

The objective of the workshop was to perform a comprehensive assay of the situation and suggest a synergistic research agenda for each of the areas that collectively will make a significant impact. This report contains the recommendations of the attendees.

The steering committee for the workshop consisted of Bill Wulf (U. Virginia), Jim Aylor (U. Virginia), John Hennesy (Stanford), Randy Katz (Berkeley), Ken Kennedy (Rice), Ed Lazowska (U. Washington) and Alan Smith (Berkeley). The workshop convened in Charlottesville Virginia on April 12-13, 1993.

# 2 Background

As noted above, although the amount of memory available has increased apace, the growing disparity between processor and memory speeds is likely to be a dominant concern for computer architects, compiler writers, algorithm designers, and users for at least the next decade.

Further compounding the issues is the increasing use of high performance microprocessors in scalable parallel systems. Both the absolute performance of these processors and their phenomenal price/performance ratios make them natural candidates for building large scientific machines. This use, however, further strains the memory system and adds the complexity of bandwidth as well as latency, dealing with the interconnection network, and the possibility of nonuniform access times.

Finally, the memory must be considered in the context of the total system; I/O as well as processor demands on it must be considered. Hence, issues traditionally considered in the domain of operating systems also play into memory system performance.

While it is not clear whether some new, unanticipated approach will arise, it seems more likely that the "solution" to these problems will lie in a synergistic interplay of evolutionary refinements of existing techniques -- caching, data prefetching, memory conscious architectures, compiler optimizations, etc. In particular, caching has proven to be a robust, general mechanism for decades; larger, smarter and multi-level caches will undoubtedly continue to play an important role. Nonetheless, it is time to consider complementary ideas.

# 3 Workshop Mechanics

The objective of the workshop was to bring together experts on each of the facets of the problem to formulate a set of recommendations for a research agenda to address an overall solution (those attending are listed in Appendix A).

Prior to the workshop participants were asked to submit a brief white paper summarizing their perception of (a) the status of their area of research relative to the main topic, and (b) the potential for future work in the area. Copies of the papers are located in Appendix C.

The format of the workshop was designed to maximize interaction and facilitate the production of this report. Lengthy presentations were avoided in favor of group interaction.

To stimulate discussion, four plenary panel sessions were organized around topics raised in the white papers:

- Session 1: General Problem (Chair John Hennessy)

- Session 2: Software Status (Chair Ken Kennedy)

- Session 3: Research Directions (Chair Alan Smith)

- Session 4: Memory Systems (Chair Randy Katz)

The participants were then divided into three working subgroups covering software, memory systems, and cpu/architecture issues. These subgroups were charged with formulating the recommendations of the workshop, and the remainder of this report is organized around their reports. Panelists from the above four sessions were distributed among the subgroups to ensure that hardware concerns were represented in the software recommendations, etc.

In addition to the recommendations, a number of interesting remarks by various attendees were recorded; these are assembled in Appendix B. They are not direct quotes, but capture the essence of the point and provide additional insight into the nature of the problem(s) and research agenda.

# 4 Processor Subgroup Report

Attendees: Keith Cooper, Mike Foster, Ken Kennedy, Howard Sachs, Pen-Chung Yew, Bill Wulf

Charge: The group was asked to identify important issues in overall system architecture, especially including instruction set design, that impact memory performance.

## 4.1 Observations and Recommendations Concerning NSF Funding

Due in large measure to the dynamic nature of the computer field, there has been a closer relation between the "science" and "technology" of the discipline than in many other fields. This close relation is mirrored in a similarly close relation and interaction between academia and the private sector — between research and development. This relation has been both intellectually and commercially extremely fruitful.

The nature of the discipline, and its close relation to practical and even commercial development, raises questions about the proper nature and role of NSF funding for the field. Specifically, NSF has traditionally focused on "pure", "basic", "long term" research; thus one can ask whether the sort of problems discussed at this workshop, and indeed all of those involved is "systems building" are appropriate for NSF support.

The answer is unequivocally yes!

For this discipline, at this time in its development, these issues raise fundamental questions about the organization of computation and the nature of the engines that can effect that computation. Specifically, the building and analysis of research prototype systems is an appropriate research methodology for understanding these questions.

At the same time, NSF should not fund near term development that duplicates industry. Therefore, we recommend:

- NSF's role is to build research prototypes that will not be built in industry.

- NSF should fund research that goes beyond the horizon of industry, and should explore alternatives not being pursued in industry.

- There should be emphasis on collaboration with industry to ensure the relevance of the project. This type of collaboration could be arranged after an initial exploratory concept-validation project.

For other disciplines at different stages of their maturity we recognize that this may not be the proper role for NSF. For this field it is.

# 4.2 Observations and Recommendations Concerning Architecture

The CPU/Architecture subgroup had six "top level" recommendations, with a number of specific examples of each. We first present the top level recommendations and then discuss the specifics.

NSF should support research into scalable benchmark collections so that performance evaluation of architectural schemes can be made independent of advances in the underlying technology.

- NSF should support research into methods that expose and give the user or system software (OS and compiler) more control over the memory hierarchy, including registers, cache, memory, remote disk cache and mass storage.

- NSF should support research into architectural, software and programming implications of quantitative changes in base technology that lead to qualitative changes in the way that a technology is used.

- NSF should support research into alternatives to conventional memory hierarchy

design as pursued by industry, particularly when a change in technology may obviate some of the assumptions behind the conventional design.

- NSF should support research that explores the implications of large-scale multiprocessors for the design and management of the memory hierarchy.

#### 4.2.1 Scalable Benchmarks

This recommendation was actually first made during one of the plenary panel discussions, but the CPU/Architecture group felt that it was extremely important that it should be included among their recommendations. Almost all current benchmarks are static, and their performance improves with each successive hardware generation. This is, perhaps, useful for deciding which competing system to buy, but it does not help us to understand whether that system has effectively exploited the technology advances over its predecessors.

A "scalable" benchmark is one whose complexity scales with the technology in such a way that if it requires unit execution time on one generation's hardware, one would expect that it would also require unit execution time on the successor generations. If execution took *less* than unit time, the implication is that architectural or software innovation has exceeded the pure hardware advance. If execution took more than unit time, the implication is that the underlying hardware advance was not effectively exploited.

#### 4.2.2 Exposing The Architecture

In the past one objective of architectural design was to make a machine relatively easy and safe to use; assembly language programming made this essential. However, few if any programs are still written in assembly language and compiler technology has become *much* better. It is therefore worthwhile reexamining this premise, and possibly expose

much more of the underlying operation of the machine in those cases where doing so may improve performance. Examples possibly worth considering include:

- prefetch: Prefetch instructions have been discussed in the literature, but only one

extant processor includes such an instruction and it is a nop in the initial implementation. Moreover, expression of intent to prefetch of multiple data items (as

opposed to scalars), should be investigated.

- cache management: Modern compilers sometimes know a good deal about when data will and will not be used. After a step of a blocked algorithm, for example, the compiler could inform the cache to flush certain data. In other cases, the compiler could control a set associative cache to avoid conflicts.

- *memory map manipulation:* A great deal of copying of data might be eliminated if safe user-level manipulation of the virtual memory map were possible.

These may or may not be good ideas in themselves — the real point is that the traditional assumption that these kinds of functions should be automatic and invisible to the programmer are not necessarily valid any longer.

# 4.2.3 Implications of Qualitative Changes

Sufficiently large quantitative change can induce qualitative change. There are enough quantitative changes happening simultaneously to suggest that we should investigate whether these are about to either invalidate prior assumptions or provide new opportunities to improve memory performance. For example:

- The next generation of processors will clearly be true 64-bit machines. This at least creates the possibility of 64-bit instructions, and raises the question of how so many bits would be used for a single instruction. For example, one could use a full 64-bit instruction to name very large register sets (effectively a local memory)?

- In the same vein, caches were the "right solution" in an era when compiler technology was less sophisticated than now. Is it conceivable that with current or foreseeable compiler technology, an explicitly managed local memory (or large register set) would be more effective? A cache is, after all, a *reactive* device; in many cases a compiler knows likely future execution paths and could be proactive.

The broad adoption of object-oriented programming could potentially reduce locality (at least data locality), and require rethinking caching strategies. Data derived from traces of "pre-OOP" programs may not be representative of future program behavior.

Again, these may not be good ideas in themselves — the point is that it is time to examine some of the generally accepted assumptions.

# 4.2.4 Alternatives to Conventional Memory Hierarchies

The current memory hierarchy has served us very well indeed, and it may continue to do so. Nevertheless, the degree of the growing discrepancy between processor and memory speeds suggests that in its role as funder of longer term research, the NSF should begin exploring alternatives. The creativity of the research community is probably the best source of new ideas, however a few examples might be:

- Explicitly managed local memories, as discussed above. In particular the trade-off between cache and large register sets should be explored.

- Reordering of accesses. Modern DRAM isn't really "random access" any longer;

that is, the time to access a particular cell now depends upon the prior history of

requests. Thus, to get the most from these devices the order of requests must be

managed both compile-time and run-time mechanisms to do this should be

explored.

## 4.2.5 Implications of Large Scale Multiprocessors

The trend to use production microprocessors as the compute engines of scalable multiprocessors will continue. This trend compounds each of the issues mentioned above, plus adding another set of its own. For example,

- Prefetch doesn't really work for "do across" concurrency; a form of data forwarding is needed. What is the proper architectural support?

- Coherence in a scalable shared memory system can be costly. Perhaps with compiler help not all data references need to be kept coherent. Should we consider separating coherent and non-coherent load/store instructions and permitting the compiler to emit the latter when it can prove that coherence is not required?

# 5 Memory System Subgroup Report

Attendees: Jean-Loup Baer, Forest Baskett, Doug Clark, Garth Gibson, Charley Hitchcock, Norm Jouppi, David Wood

Charge: The group was asked to identify important issues in memory systems design, including storage systems.

The Memory System Subgroup began by asking why anyone, but NSF in particular, should focus research on the memory problem, and decided that there are at least three important reasons.

- Intensive applications on current machines can spend 1/2 to 2/3 of their time waiting for memory, e.g., Gray's sort benchmark on an Alpha system takes under 10 seconds, with 6.5 seconds of that waiting for memory. Future machines will be worse. This trend hinders the exploitation of rapidly increasing processor speed.

- As machines become more capable, we find larger and more complex problems to solve, e.g., national libraries, human genome, real-time speech and video, etc. Significant advances in technology, architecture, software, and algorithms are required to keep pace with these rapidly changing demands.

- The United States is the leading innovator in computer systems. We have a significant competitive advantage and should strive to keep it. This advantage has been fostered by significant government investment in research, and close ties between academic researchers and industry. NSF needs to continue to encourage cross fertilization between industry and academia.

In order to conduct research on memory systems, there must exist an "infrastructure" that includes:

• Application Characterization: Memory system researchers need a deeper understanding of key problems, such as national libraries, real time speech, Navier Stokes, HD-TV, multimedia, and the human genome project. Classical problems such as dense linear algebra are relatively well understood throughout the community. However, many researchers are unfamiliar with the characteristics of these other problems, particularly on parallel machines. Work that identifies the essential nature of these problems to the community at large would be extremely valuable.

- Design Verification Tools and Techniques: As hardware design becomes largely a

matter of writing software, design verification has emerged as the most time-consuming and error-prone part of the process. More powerful design verification

tools and techniques are needed to eliminate this bottleneck and reduce the design

cycle.

- Compiler Infrastructure: Past research has shown that compiler optimizations can significantly improve memory system performance. However, because a good optimizing compiler represents many person-years of work, this research has been limited to those few institutions with mega-funding. Research in compiler/memory system interactions could be funded more efficiently by supporting a common compiler infrastructure, just as Berkeley UNIX and Mach have facilitated operating system research.

- Simulation Infrastructure: Studying compiler/memory system interactions requires

both an optimizing compiler and a real or simulated memory system. Simulation

infrastructure should be supported so that researchers are not forced to replicate

the simulation framework.

Given this infrastructure, the group identified a number of major areas that NSF should fund or continue funding: DRAM interfaces, Processor/cache interfaces, Cache Hierarchies, Shared memory coherency and communication, Virtual memory and translation, Disk Caching and Parallel Storage, and Prefetching support. Below is a brief discussion of the key needs in each of these major areas.

#### 5.0.1 DRAM interfaces

The standard RAS/CAS DRAM interface was designed with an emphasis on low-cost and high-density. As microprocessor cycle times continue to decrease, the limited bandwidth available from this interface becomes an increasing bottleneck. A new DRAM interface is central to enabling future systems to exploit the potential of next generation processors. While several new interfaces have been propose to address this problem, it does not appear that a consensus will soon emerge. The heart of this debate focuses on cost/performance trade-off: the PC market--which dominates DRAM sales--is very cost sensitive, while the workstation and massively-parallel processor markets demand higher bandwidth.

The group felt that academia could play a critical role in analyzing and evaluating the alternatives, perhaps developing a new interface that balances the needs of the competing markets. One reason to believe a compromise may be possible is that future PCs will support "multi-media" capabilities—such as real-time video—and hence require much higher bandwidth than current systems.

## 5.0.2 Processor/Cache Interfaces

Current generation microprocessors are designed for PCs or workstations--not high-performance MPP-class machines. These micros tend to be optimized for applications that exhibit significant locality, and consequently do not provide the bandwidth required by large-scale scientific computations. Research is needed to find an interface that appropriately balances cost and bandwidth requirements for diverse applications.

#### 5.0.3 Cache Hierarchies

As transistor densities increase, the role of on-chip and off-chip caches change. For example, some researchers have suggested that multiple levels of on-chip cache are necessary to balance competing demands for bandwidth and capacity. Continued research is required to understand these trade-off, including traditional issues such as size, associativity, and write policy, as well as more aggressive techniques such as non-blocking caches, multiporting, multiple banked caches, and hardware and software prefetching. In particular, some industry participants felt that non-blocking caches are difficult to implement and verify, making this a fertile area for collaboration between academia and industry.

In addition, research is needed to understand how trends in applications will affect cache performance. For example, object-oriented programming results in fundamentally different access patterns, which cache designers must take into consideration.

#### 5.0.4 Shared Memory Communication and Computation

Shared memory is an important paradigm for large-scale parallel machines. However, researchers have not yet reached a consensus on how this paradigm should be supported. A key requirement in reaching this consensus is to understand the communication and computation demands of real parallel programs. While much has been learned about the behavior of dense linear algebra, there are many other important codes, e.g., Navier Stokes, that have fundamentally different structure. We need to understand the bandwidth requirements, access patterns, and synchronization requirements of these and other sparse codes. What demands do these applications place on the memory system and interconnec-

tion network? What are the correct metrics for evaluation? Aggregate memory bandwidth? Bisection bandwidth?

## 5.0.5 Virtual Memory and Translation

Microprocessor architectures are moving rapidly to support 64-bit virtual addresses. However, little research has been done to understand the impact of this massive address space on applications, operating systems, and memory system implementations and performance. Does a large address space enable new applications and algorithms, such as studying the human genome? What mechanisms must hardware support to efficiently exploit these large address spaces, e.g., super-pages? What are the implications of managing very large virtual address spaces? Of managing very large physical memories?

# 5.0.6 Disk Caches and Parallel Storage systems

Research into redundant disk arrays (or RAID) is not diminishing and should receive continued support. Industry is picking up the technology, but the vast majority of participating companies are too small to be capable of doing or funding broad-based research into this area. Larger companies have started in-house development groups, but their patenting efforts seem to limit their ability to foster this fledgling marketplace. There is an industrial organization, the RAID Advisory Board, that has the goal of developing a RAID marketplace. Unfortunately, this group of mainly technical marketing representatives led by industry consultants, is focusing on standardizing RAID technology rather than encouraging new basic research. Now, as we begin to see a broad spectrum of computer science researchers address this area, the first performance models and new organizational concepts for on-line transaction processing applications have appeared. Sustained funding for systems experimentation, theoretical issues in scaling to massive parallelism, and applications-directed solutions should ensure that basic advances continue to broaden the effectiveness of this new technology.

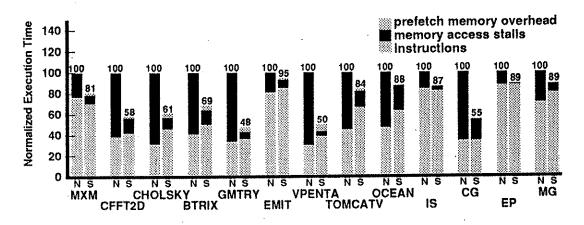

### 5.0.7 Prefetching: Hardware vs Software

Recent research results indicate that software-controlled prefetching can be extremely effective in hiding memory latency. Similar results indicate that hardware-initiated prefetching can also be effective. Determining the proper balance between hardware and software remains an extremely important research area, because of the significance of the potential performance improvements. Continued research is needed to determine the trade-offs of prefetching into different levels of the memory hierarchy, level of hardware support, granularity of data, and interaction with cache coherence protocols. It is

extremely important that this research incorporate realistic implementation factors, making it an excellent opportunity for academic/industry collaboration.

# 6 Software Subgroup Report

Attendees: Susan Eggers, John Hennessy, Randy Katz, Monica Lam, Alan Smith, Steve Scott

Charge: The group was asked to identify important issues where software can impact memory performance, including algorithm design, compilation techniques, coding practice, etc.

We feel strongly that entire of discipline of software research needs to pursue a more quantitative, comparative methodology in the research process. The current state of the field, by and large, focuses on algorithm development coupled with some limited prototype implementations, but little comparative empirical studies are pursued. New work is not placed in the context of quantitative improvements to the existing body of knowledge. Experiments are not repeatable in a scientifically meaningful way. And all too often, experiments lack real and relevant measurements.

To remedy this situation, the Software Subgroup makes the following recommendations:

- Software researchers should work with real systems, or at the very least, large pieces of software representing major subsystems.

- Software research should be driven by real world applications and realistic workloads.

- To obtain access to these, it is important for software researchers to work with industry.

- The research community should demand comparative, quantitative results in its publications and research proposals. New ides should be evaluated on their ability to demonstrate a real improvement to the existing state of the art.

- The research community should focus on collecting real system measurements, not

only those that are easy to measure. For example, all too many researchers focus

on miss rates rather than total system performance.

The community should support on-going technology exchanges with industry.

Faculty researchers should work actively with industry, either by regular consulting, close collaborative research or "co-op" programs.

Systems research typically falls into two categories: simulation-based studies and prototyping activities. Both are important, and should be encouraged, but encouraged for answering the right questions.

To facilitate prototyping activities, the community needs substrates upon which to build its prototypes rather than starting from scratch. In this regard, the operating system community is in a stronger situation than the compiler community. V-node file systems and microkernel operating systems make it easier to prototype (and trace) new file systems. A similar research infrastructure is needed for compiler researchers. Part of the reason for lack of progress in this regard for the compiler community is that we are just now realizing that a compiler is a "big program." The kind of modular decomposition found in modern operating systems has no analogies in modern, memory conscious compilers.

The Working Group recommends that some research funding should be directed to those activities that characterized by building infrastructure in support of prototyping activities. All funded research should be "credible," along the lines of the criteria described above. Today, there exists a significant funding hole for medium-scale software projects, at the level of a few faculty and several grad students. Such projects could be successfully pursued should the appropriate infrastructure be put in place. By focusing on credibility, we believe that existing research would improve in quality. While the construction of such research infrastructure may be beyond the usual scope of NSF support, NSF support could complement such activities.

In the above, we have focused on prototyping activities. There continues to be a strong need for work in fundamental inventions and evaluations across all the software areas. However, it is important to avoid research on theoretical approaches that are demonstrably in conflict with reality.

#### **6.1 Technical Directions**

We begin by listing those technical directions that are worthy of continued research support. Each area is characterized by three metrics: impact, speculativeness, and effort. Impact qualifies the potential effect on the field of research in this area. To some degree

we have downgraded impact when we thought that solid research effort in the area were already underway. Speculativeness qualifies the risk of the area. A highly speculative area means that some ideas may turn out to be highly useful while many will fail. And finally, effort describes the level of funding needed to demonstrate quality of ideas.

The five research areas are the following. The first three are particularly singled out for high priority efforts:

- Architecture-directed Compiler Research

Potential Impact: High; Speculativeness: Low; Effort: High

- Research in File and I/O Systems

Impact: High; Speculativeness: Medium-Low; Effort: Medium

- Language Research

Impact: Very High; Speculativeness: Very High; Effort: Low-High

- Research on Applications Behavior and Improvement

Impact: Medium; Speculativeness: Medium; Effort: Medium

- Parallel and Memory Sensitive Performance tools

Impact: Medium; Speculativeness: Low; Effort: Low

These are described in more detail in the following sections.

## 6.1.1 Architecture-Directed Compiler Research

There are a catalog of techniques under investigation that have the potential for improving application performance, both for memory and secondary storage. These include the following:

- Prefetch

- Loop Transformations

- Data Restructuring

- Coherence Management

- Code Scheduling

- Run-time Determination of Compilation

Whole Program Compilation. In particular, we need to understand the behavior of the whole program in order to do a credible job of data restructuring and extraction of parallelization.

In general, many of these techniques are well understood for programs that manipulate arrays. However, they are not understood at all for more application-oriented data structures.

## 6.1.2 File and I/O Systems

The I/O access gap continues to increase, and is likely to continue to widen for the fore-seeable future. The important research issues include the following topic areas:

- Disk Cache. In this area, there still exists a need to understand the algorithms for cache operation, how to exploit parallelism in the design of the disk cache, the effect of cache parameter choice on total system performance, and the issues of disk cache consistency in a parallel environment.

- Evaluation of new file and I/O techniques. New I/O architectures like RAID and file system approaches like log structuring need to be evaluated with real workloads, such as production commercial and scientific environments.

- Caches and Buffers. The role of disk caches and operating system-managed I/O buffers need to be evaluated within the context of new technologies like RAID and/or LCFS.

- File Migration Studies. The studies done in this area are over ten years old, while

the underlying technologies have undergone radical challenges. They should be

revisited in the context of new workload demands and new multi-level storage

technologies.

- Shared data management. New algorithms need to be developed and evaluated for (real) management of shared data in distributed and MP systems.

# 6.1.3 Language Research

We believe that there are significant opportunities in developing new language extensions (as opposed to new computer languages) that are applications specific. In particular, we are interested in extensions that ease the expression of parallelism and enhance locality.

We call these "application structures." For example, little is known about how to specify and compile tree data structures in modern compilers. Another example is sparse matrix support, with the related need to develop compiler algorithms to discover and exploit non-regular access to data structures. There is a strong relationship between research in compiler techniques and research in extending computer languages.

Besides the data structure specifications, a second area of language research involves the specification of the user's model of the underlying memory system. How much does the user need to specify? How much does s/he need to know about the details of the memory hierarchy? An aspect of any such a model must be like an onion skin. In other words, the user can exploit more details in order to get more help from the system. The hints that are specific to a given machine should be discouraged, while hints that are specific to a given applications should be encouraged. In any event, no hint should change the semantics of the program.

# 6.1.4 Applications Behavior and Improvement

Since we can't fix the application after it is written, an important research direction is to work on ways to express the algorithm correctly the first time. Such specifications are not just architecture driven, but should be influenced by applications as well.

A critical need is to find new ways to provide performance feedback to applications developers. They must understand the behavior of their applications in order to drive the cycle of improving program performance.

# 6.1.5 Parallel and Memory Sensitive Performance tools

Good work in performance tools is currently underway, but more needs to be done. The tools are critical if applications designers are to be able to write better programs. They play a major role in providing the feedback mechanism to users. In particular, applications developers should be able to use such tools to obtain direct quantitative measures of the effects of their hints on the performance of the application.

Performance tools make possible the kind of quantitative, credible research we called for in Section I above. There should be some emphasis on documentation/distribution of existing tools, to make them available to a wider research community than the group who originally developed the tools. This should be considered part of the necessary "infrastructure" for supporting the software research community.

# 7 Summary

A short workshop cannot hope to invent and enumerate all aspects of a research agenda for a problem as critical and complex as this one. We hope that we have made three essential points, however:

- The problem is a critical one.

- Business as usual is unlikely to solve this problem; new ideas are required.

- This is the sort of problem requiring building, measuring and/or experimenting with "real" systems, and NSF should fund this sort of research.

# 8 Acknowledgments

Ms. Kimberly Gregg made all of the arrangements for the workshop, and kept it running smoothly. Graduate students Mike Alexander, Mark Bailey, Sanjay Jinturkar, Sally McKee, Steve Moyer, Carmon Pancerella, Ramesh Peri, and Alec Yasinsac took the notes and made the recordings from which this report was compiled as well as assisting in many other ways. The attendees express their gratitude!

# **Appendix A: Participants**

Those attending the workshop were:

Jean-Loup Baer University of Washington

Forest Baskett Silicon Graphics

Doug Clark Digital Equipment

Keith Cooper Rice University

Susan Eggers University of Washington

Mike Foster National Science Foundation

Garth Gibson Carnegie Mellon University

John Hennessy Stanford University Charles Hitchcock Dartmouth College

Norm Jouppi DEC WRL Randy Katz Berkeley

Ken Kennedy Rice University

Monica Lam Stanford University

Edward Lazowska University of Washington<sup>1</sup>

Howard Sachs Integraph

Steve Scott Cray Research

Alan Smith University of California, Berkeley

David Wood University of Wisconsin Bill Wulf University of Virginia

Pen-Chung Yew University of Illinois at Urbana-Campaign

<sup>- 1.</sup> Unfortunately, Professor Lazowska had to cancel at the last moment.

# **Appendix B: Interesting Remarks**

During the workshop, a number of interesting interchanges occurred, and we have tried to capture a few of them here. These are not direct quotes, but attempt to fairly represent the point that the speaker made. Have grouped these by topic area.

#### General Remarks

Howard Sachs: OOP needs simulation and research dollars and it'll be a big win for industry since we're heading down this path. We still don't know the extent of the OOP effect on memory systems.

Ken Kennedy: We should fund more compiler research (said with grin).

Susan Eggers: In order to determine general funding directions, we need to: determine what the problems really are (by doing research to explore this). Let the problems drive our hardware and software solutions. We need to emphasize "bottom line" technology, use real workloads, use execution time as the performance metric, and develop good software platforms for real measurements and comparison.

Howard Sachs: We need more compiler and language PhD students. Will there exist a DRAM problem in the year 2000? yes and no. Will 90% of industry have a problem? no -- because they'll be using PCs. So where's the problem? workstations object-oriented programming multiprocessors (not for 8-processor SMPs, but definitely for 500-processor MPPs -- and this will be a bandwidth problem, rather than a latency one).

Ken Kennedy: Base technology drives what we're doing in the architecture community. Should this also be driven by compiler and applications people?

Ken Kennedy: Our research has to be linked to technological trends in order for it to have any impact -- if we look ahead too far and technology takes a different turn, even interesting research might become "useless".

Alan Smith: The major problem with proposals is reviewing. If you get better reviewers, better projects will be funded, and better research will be done.

Alan Smith: A bunch of graduate students using a toy file system does not represent real workloads.

Alan Smith: We need a co-op program in industry for faculty, similar to one for students.

Howard Sachs: We need standards in order to influence semiconductor manufacturers. We have to solve problems architecturally at a level above that of the DRAM cell.

# Concerning Research Infrastructure

Dave Wood: How do we evaluate the benefits of hardware support for memory performance? We NEED a simulation platform. We need a standard intermediate form to communicate much of the compiler analysis to machine-dependent backends in order to make use of all the hardware's resources. Right now it's hard to separate the analysis from the algorithms that make use of that information.

## Concerning Benchmarking

Steve Scott: We want benchmarks to scale with the underlying raw technology in order to gauge how effectively we're USING that technology. We need to extend benchmark suites to other areas; for instance, we want a graphics benchmark suite, or an object oriented benchmark suite.

## **Concerning Architecture**

Pen Yew: Packaging constraints (clusters) correspond well with application code. The memory hierarchy should be visible to OS, compiler, and user/language.

Bill Wulf: Compiler/architecture interactions are the thing to look at.

Ken Kennedy: Memory organization should only be exposed to the user if the OS/compiler is lousy. We need to hide the memory hierarchy from users.

John Hennessy: Once you tell user about memory hierarchy and locality, what/how do you tell them? We need a memory model to explain to programmers.

Bill Wulf: The question is where structurally dissimilar hierarchies can be described in the same way.

Susan Eggers: There should be a difference between an actual memory model of a machine and an abstract memory model. An abstract memory model should be used for the programmer -- an actual model is too complicated to explain to a programmer.

John Hennessy: If we tell the user something about the memory hierarchy, it should be relatively SIMPLE (the same goes for parallelism). "Local" versus "Remote" should be a good enough programmer's model.

Bill Wulf: Don't forget bandwidth-limited applications. The more improvements that are made in DRAM organization, page mode, etc., the more important it is to use these components wisely in order to take advantage of their capabilities to deliver bandwidth.

John Hennessy: Many techniques to increase bandwidth also increase latency. We can buy bandwidth with dollars, but things don't scale linearly.

Steve Scott: Money can buy bandwidth, but not latency.

## Concerning Multiprocessor Architecture

Pen Yew: Designing better memory systems for parallel machines requires better understanding of parallel program behavior, better benchmarks (we need a common suite), more and better performance measures and simulations on future and existing machines.

Steve Scott: P < 2M (meaning that the importance of parallelization is less than twice the importance of memory optimization, in terms of overall importance).

Alan Smith: Bus traffic is so high that multiprocessors are only MARGINALLY useful.

## Concerning Caches

John Hennessy: There has been more cache research and many more cache papers (than I/O papers) because it's much easier research to do.

Susan Eggers: Stressing temporal locality isn't enough. There are too many restrictions on how we can use the cache. The user doesn't get the expected performance.

Steve Scott: We're seeing the same problems with VM -- the user should write code with locality.

Garth Gibson: Building larger caches doesn't scale performance linearly. Doing this assumes that the workload is constant. The bottom line is that linear increases in cache size are not sufficient for database and scientific computing applications.

Alan Smith: Published data indicates that the miss rate goes down with the square root of the cache size. Is designing DRAM for use with cache different from designing DRAM for stand-alone memory systems?

Bill Wulf: (concerning cache coherence) Parts of applications don't need coherence; can we productively separate access into those that need coherence and those that don't? If so, then we needn't pay for it all of the time. This is another area where compiler/architecture interaction is important.

# Concerning Memory Component Design

Forest Baskett: The biggest thing we need to accomplish is to provide guidance to DRAM venders. There is a whole set of potential [DRAM organization] improvements possible (cache, organization, voltage, pinouts, etc.) -- DRAM organization is a relatively new field.

John Hennessy: The problem is getting everyone to agree on what we should do, and then sell that to the PC market -- if each improvement remains a "niche technology", we're doomed.

Forrest Baskett: In order to influence technology on this huge growth curve, we have to provide easy, cheap solutions, or else it won't be worth it for venders to make changes. Venders need a volume market.

John Hennessy: IC and DRAM technologies are giving an exponential growth curve with respect to size -- and we *don't want* this to stop.

Steve Scott: We need to sell ideas to customers in order to get DRAM manufacturers to listen. The PC industry drives the DRAM business, and manufacturers are scared to introduce anything that isn't standard RAM.

# Concerning What Software can Do

Keith Cooper: Hardware design is based on probability, but users care about performance on THEIR code (the characteristics of which may not match the assumptions made when the hardware was designed).

Keith Cooper: What can compilers do? change reference patterns, understand specific locality, change layouts and alignments at runtime. We need to do things differently, and stop doing "more of the same" with respect to larger or greater numbers of caches.

John Hennessy: People claim every few years that they have understood the compiler field completely and there is nothing left there; but then they keep going back to it. I feel that there is lot to be understood and done yet.

Howard Sachs: Industry is desperate for compiler writers.

# Concerning IO

Alan Smith: Research in FILE and I/O gets much less attention than cache memory systems, but is no less important.

# **Appendix C: White Papers**

# Tolerating memory latency

# High Performance Memory Systems Workshop

Jean-Loup Baer

Department of Computer Science and Engineering, FR-35

University of Washington

Seattle, Wa 98195

March 1993

## 1 Motivation

Peak processor performance has now surpassed the 100 MIPS level. With the current VLSI developments, several functional units, instruction and data caches, and further hardware support functions can be included on a processor chip. Processors are backed up by very large (several megabytes) second-level caches and main memory. In the case of shared-memory multiprocessors or distributed memory systems, the connection to memory can be implemented in a variety of ways (bus, ring, mesh or multi-stage interconnection network, scalable coherent interface) depending on the size of the systems. With processor speed increasing very rapidly, and memory latency and bandwidth progressing at a slower pace, we must investigate techniques to reduce the effects of memory latency, these effects being exacerbated by physical constraints (e.g., chip crossings, latency in the interconnection networks) and logical constraints (e.g., cache coherence, hot spots, synchronization).

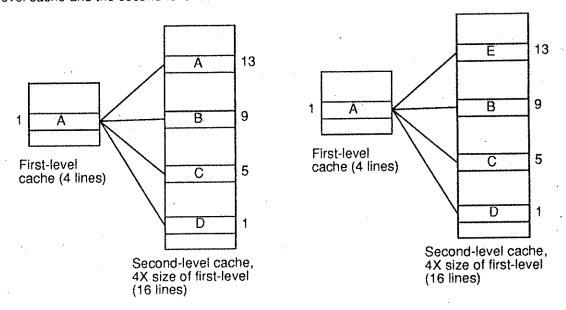

The introduction of caches, in the late sixties, was motivated by the goal to balance processor speed and memory access time. Caches have been extremely successful since they not only provide the desired performance enhancements but also they are completely transparent to the software, i.e., until now, the introduction of a cache has been an organizational matter, not an architectural decision. However, with larger caches, the cache access time again becomes disproportionate with the processor speed. Today, even with two-level caching, the cost of memory access is significant enough so that a system approach must be taken for the management of the cache hierarchy (e.g., flush, fence, prefetch, and poststore instructions).

In order to put these effects in perspective, consider the following table of memory latencies with a normalized processor cycle time of 1 (C1 is a first-level or on-chip cache; C2 is a second-level cache; MM is main memory).

| ,                    | C1 | C2   | MM (close) | MM (far) |

|----------------------|----|------|------------|----------|

| 100 MIPS workstation | 1  | 6    | 25-60      |          |

| (best guesses)       |    |      |            |          |

| Dash ·               | 1  | 5-15 | 8-29       | 26-132   |

| KSR-1                | 2  | 20   | 150        | 570      |

Let us use as metric the average number of cycles per instruction, or CPI. The component of the CPI due to cache misses depends on two factors: miss ratio and memory latency. Even with the very small miss ratios that have been recorded on numerous benchmarks, it is not unusual to see the average CPI due to cache misses be as much as 2 or 3 because of the high latencies. Thus, the fact that latencies are very large compared to the processor's speed implies that cache misses have still an important impact on the loss of efficiency of the system. The memory latency problem that had been "solved" (in uniprocessors) first by the introduction of caches, then by cache hierarchies, still confronts the designers of high performance machines. This problem is compounded in shared-memory multiprocessors because latencies are larger if an interconnection network is used, or there is more resource contention (e.g., access to a shared-bus, hot spots in access to a memory module), or there is extra communication needed because of the cache coherence requirements and interprocess(or) synchronization. Since the trend is for the decrease in physical memory latency to lag behind the increase in processor speed, the CPI increment due to cache misses must be reduced by methods that decrease the miss ratio and/or hide the memory latency.

Looking at the previous table, we see that a memory reference that results in a miss at the first-level cache and a hit at the second-level has a penalty of roughly one order of magnitude. Any mechanism that is meant to reduce the latency between the two lowest levels of the memory hierarchy should then be non-intrusive. This calls for either a hardware scheme that is not on the critical path and that does not "steal" cycles from the execution of the instruction stream, or for a software scheme that can run concurrently with the ordinary stream (e.g., in a super-scalar processor or one with a load/store unit and multiple instruction issue). Of course, compiler optimizations can be added at no run-time cost to both software and hardware schemes.

When the penalty for referencing memory reaches two orders of magnitude, then spending two or three cycles on an extra instruction and/or associated address computation is not as critical. Therefore at this level, one can envision using sophisticated software methods and, if proven useful, hardware assists at the second-level cache.

Among the hardware-based methods that have been used or proposed, we can list:

- Cache hierarchies (now present in many medium to high-performance systems) and cache assists (write buffers, victim caches)

- Lock-up free caches (with various degrees of sophistication).

- Hardware-based prefetching (from simple sequential stream buffers to cache-like reference prediction tables).

- · Relaxed memory consistency models (and the hardware assists they require).

On the software side, with an emphasis on the multiprocessor case:

- Software cache coherence schemes.

- · Data placement (increasing locality and reducing false sharing).

- Prefetching and poststoring.

# 2 Prefetching

Looking only at prefetching, the previous discussion leads to the following matrix:

|          | C1-C2                                       | C2-MM                                   |

|----------|---------------------------------------------|-----------------------------------------|

| Hardware | Yes                                         | Maybe                                   |

|          | Special sophisticated functional unit       | Special unsophisticated functional unit |

| Software | Yes if<br>super-scalar or<br>multiple issue | Yes<br>Sophisticated compiler           |

Although we intend in the long run to look at the four elements of the matrix, we have concentrated on the hardware-based prefetching at the C1-C2 level and on some aspects of software prefetching at the C2-MM level.

Our current and future research plans are as follows:

# Level 1 to Level 2: Hardware-based prefetching

At this level of the memory hierarchy, we do not make any distinction between the single processor and the multiprocessor case. Coherence effects should not have a great impact on prefetching to the first-level cache if some form of inclusion is implemented. Hardware prefetching should be useful in reducing capacity and conflict misses in the (relatively) small and most likely direct-mapped first-level cache.

Our approach has focused mainly on loop-domain references in applications. It combines the dynamic determination of stride information and conventional instruction look-ahead. The variations on a common scheme consists of a support unit for the C1 data cache, consisting of a Reference Prediction Table (RPT), a Branch Prediction Table, and associated logic. The RPT is organized as a regular cache and records the referencing patterns. The key to hiding memory latency is to keep enough distance between the prefetches and the execution stream so that the prefetched data arrives just, or slightly before, it is needed.

The type of questions that can be asked are:

- 1. How complex should the associated unit be? For example, would a complex scheme, akin to the Two-Level Adaptive Branch Prediction, have a significant impact on non-numeric applications (we have evidence that a simpler scheme works well for numeric applications)?

- 2. Should prefetching be done in the D-cache, or in a buffer, or associated with victim caching to reduce conflicts misses caused by prefetching too early?

- 3. What significance have the usual cache parameters (capacity, line size, associativity) and the amount of bandwidth between the first and second level caches (regular or split bus)?

# Level 2 to Main Memory: Aspects of software prefetching

Software-directed approaches rely on data access patterns detected by static program analysis. Within the context of the interface between a second-level cache and main memory, and most importantly in the case of a shared-memory multiprocessor but the same analysis will be valuable for a distributed memory architecture, a prefetching algorithm must answer the following questions: when to prefetch (certainly quite far in advance for tight loops), what data is a candidate for prefetch (the penalty of prefetching unused data is high since there is not only pollution in the cache but also increased utilization of the interconnect), and what is the size of the prefetched data. The same type of algorithm could be designed to poststore: which data should be broadcast, to whom, and when?

At this point, we are planning studies on an architecture based on a tree hierarchy of busses (we have an instruction level simulator for that system). The main focus of attention will be the correlation between prefetching and data placement (where in the hierarchy should we keep the prefetched data) in the various clusters and levels of the hierarchy. The data placement problem should also provide some interesting insights of programming machines relying on message passing between clusters of processors. Our initial approach will be pragmatic and rely on the application programmer to insert the prefetch operations and do the data placement. In the long run, we might want to investigate how this fits within languages such as HPF.

# 3 Summary

Means to reduce or tolerate memory latency is a challenge that cannot be avoided if we want to take full advantage of current technology. We feel that part of the millions of transistors that are now present in a single chip could be advantageously devoted to a special-purpose functional unit for prefetching. We also feel that software prefetching, and associated data placement, is crucial for improving the performance of programs running in either a shared-memory multiprocessor or a distributed memory machine.

# Compilers, Microprocessors, and Memory Systems

Preston Briggs

Keith D. Cooper

Rice University

Houston, Texas 77251-1892

#### 1 Introduction

One key performance problem in today's microprocessor-based computers is the shifting balance between the speed of a floating-point multiply instruction and the speed of a load instruction. A decade ago, load was fast and multiply was slow. That situation has reversed over the last five years. Within a couple of years, we may see systems with processors clocked at three nanoseconds talking to fifty or seventy nanosecond memory chips. To make effective use of these fast processors, the combined hardware-software system must hide this speed mismatch. That will require changes in our compilers, our operating systems, our microprocessors, and our systems architecture.

This white paper tries to assess the state of compiler techniques for hiding memory latency. It looks briefly at trends in memory system design. Finally, it suggests a strategy for deploying our resources, in both software and hardware, to improve our ability to manage latency in real computations.

## 2 What can compilers do today?

Recent years have seen a large body of work developed around the problem of providing adequate performance on cache-based systems. This section tries to assess what's possible in compiler-based cache management today.

Any attempt to improve cache behavior through compile-time techniques must begin by trying to understand when cache misses occur. Several groups have looked at this problem. Porterfield et al. proposed a simple scheme for discovering the overflow iteration – the iteration of a loop where a cache miss must occur [7, 1]. Mowry et al. use another scheme to estimate where cache misses must occur [6]. Both techniques rely on dependence analysis to spot temporal reuse. Spatial locality is usually found by looking at loop strides. Gannon and Jalby proposed a technique based on reference windows that is an alternative to dependence-based techniques [3]. Their reference windows allow them to notice spatial locality, too.

Discovering where to improve the code is just the first step. To make the code run faster, we must transform it so that its behavior better maps onto the memory hierarchy. Work in this area falls into three major categories: blocking, copying, and prefetching.

#### 2.1 Cache blocking

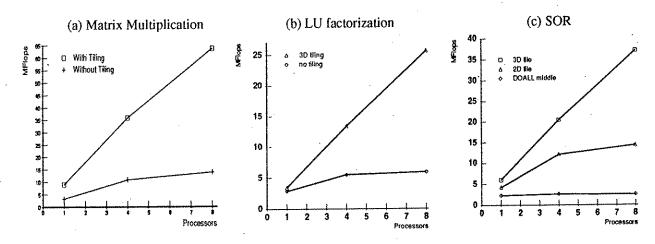

Cache blocking (also called *tiling* or *strip mining*) is a technique for reshaping the iteration space of a loop to improve its locality [9, 10, 8, 2]. Some loops overrun their reuse – they would reuse values from cache except that those values have been knocked out of the cache by intervening references. Blocking improves the performance of these loops by bringing references to a single location closer together in time. While the specific transformations involved in blocking varies from paper to paper, they include loop interchange, strip mining, loop skewing, and loop reversal.

Blocking improves performance in one specific case: when reuse exists, but the combination of cache and program behavior results in replacement of data before its reuse. Such premature replacement comes from several sources:

1. Alignment of data can cause interference (both within a single data structure and between multiple structures).

This research is supported by ARPA through ONR grant N00014-91-J-1989.

Warning: This paper contains strong opinions on hardware. We have drawn these opinions from reading and listening. We have not done the extensive simulation studies that would be required to assess completely the practicality of our ideas.

- 2. The number of items used between successive references can exceed the cache's effective size, ensuring replacement before reuse.

- 3. The replacement algorithm implemented in the cache can be a poor match to the program's actual behavior.

Blocking directly addresses the second problem. By moving successive references closer together, it increases the likelihood of successful reuse – reuse within the cache. As a side effect, it may decrease the likelihood of the other two problems, but this is an indirect effect. Blocking changes neither alignments nor replacement policies; it reshapes the iteration space.

## 2.2 Copying

Copying [4] (or streaming [5]) attempts to improve behavior by treating the cache as a fast local memory. In effect, the generated code treats the cache as a single large array. Values are explicitly copied into the array before use and modified values are copied back to main memory after their last reuse. This lets the code sidestep problems of alignment, stride, and replacement policy; the compiler tries to dictate all data movement in and out of the cache. As a further, often ignored benefit, copying can remove TLB misses from inner loops – making performance far more stable.

Copying imposes some overhead. Lam et al. show that the benefits of copying often exceed the overhead [4]. To minimize the overhead, the map from subscripts in the original code to subscript in the pseudo-array used to represent cache should be simple. A further problem arises if the instructions used to load and unload the cache allocate cache lines themselves. This introduces a subtle problem with self-interference – the loads required to copy the data into cache can cause replacements of data already moved into the cache.

#### 2.3 Prefetch (and flush)

Both blocking and copying work within a given architecture. The use of an advisory prefetch instruction offers an interesting alternative, albeit one that requires carefully designed hardware support.

Conceptually, advisory prefetch is simple. We add an additional instruction to the architecture - prefetch (expr). It initiates a fetch of the cache line containing (expr) into cache. Barring resource constraints, this allows the compiler to overlap execution with the time required for the fetch operation - a clear win. The principal drawback of an advisory prefetch scheme is that it requires modifications to the hardware.

Researchers have shown that even simple schemes for inserting prefetch instructions can be surprisingly effective [6, 1]. The decreased time spent waiting for a fetch to complete often more than compensates for the additional instruction issue slots required. A corresponding flush instruction might be used to control replacement when there is a mismatch between the hardware-enforced policy and the actual reference patterns.<sup>1</sup>

#### 2.4 Assessment

Each of these techniques addresses the problem of mapping program locality onto hardware cache structures. Each has strengths; each has weaknesses. Compilers should use these techniques whenever possible; the payoffs are large enough to compensate for the extra complexity in the compiler.

Nonetheless, questions remain about the effectiveness of these techniques on production codes. The examples shown in papers and talks are almost all small loop kernels. The extent to which these techniques can improve production applications remains to be seen.<sup>2</sup> Today, we are basically limited to improving the memory performance of simple loop nests.

<sup>&</sup>lt;sup>1</sup>Remember, LRU replacement is not necessarily what we want. It is simply a compromise based on statistical properties of programs. For a specific program, other replacement policies may work better.

<sup>&</sup>lt;sup>2</sup>A particular concern is that real loops reference more aggregate data items that the associativity of real caches. Loop distribution may help in such cases – when it is safe and legal.

#### 3 Trends in hardware

Compilers must target specific architectures. A decade ago, compilers largely ignored specific details of the memory hierarchy. Today, these details are critical. Thus, we should look briefly at trends in the design and construction of memory systems. We will focus on cache issues, but register sets and TLBs are equally important.

Trends in cache design are hard to decipher. New machines have large caches (PA-RISC), small caches (ALPHA & i860), direct-mapped caches (SPARC & PA-RISC), and set-associative caches (RS/6000 & i860). They implement diverse replacement algorithms: pseudo-random (i860XP), pseudo-LRU (i486), and LRU

(RS/6000). Some even provide prefetch instructions (ALPHA).

Several larger trends do emerge, however. Cache lines are getting longer. Primary caches, in general, become larger across different generations of the same architecture. Many systems are being designed with secondary caches (SPARC-10 & ALPHA-based systems). The one dimension that is not growing is set associativity – there is a fundamental conflict between updating the context required for LRU replacement and increasing associativity. If, in fact, a general trend exists in associative cache design, it is away from real LRU replacement.

Each of these trends is an attempt to increase the likelihood that a given value resides in cache. If small caches are good, larger caches should be better. There is substantial justification for this reasoning. Unfortunately, most of the arguments in favor of these trends ignore one fundamental fact – in many cases, the compiler can analyze reference patterns, recognize broad styles of locality, and provide the hardware

with hints.

# 4 A modest proposal

In the semiconductor industry, it is widely accepted that the number of devices on a single integrated circuit roughly doubles every eighteen months. Naturally, this trend has provoked speculation about how to use the massive number of transistors available on a single chip by the end of the decade. Current trends would move in the direction of larger on-chip caches and integration of multiple chips on a single die.

With all this extra chip real estate available, we propose taking a different approach to designing a memory hierarchy. The trends cited in Section 3 can be viewed as "more of the same." Simply put, larger caches should produce higher hit ratios. Unfortunately, this strategy produces diminishing returns – it requires ever more cache for an ever smaller improvement in the hit ratio. The other trends – longer lines, relaxing replacement policies – simplify the construction of larger caches.

Instead of building larger caches, we propose that new architectures provide hardware support for other kinds of locality. The support for prefetch in the ALPHA is a step in this direction. We should take it further. Rather than providing one principal path from main memory to the register set, we should provide several paths with different properties. For example, we should consider

- hardware support for gather and scatter operations between a small local memory and main memory.

The success of copying (see Section 2.2) argues for this support.

- a small cache (short lines & large associativity) to support references that exhibit temporal locality without spatial locality, like pointers. Such a cache differs from a register in that it provides address resolution. Analysis of addresses at compile-time is imprecise.

- a small, fully-associative cache with compiler-controlled replacement. Self-interference due to alignment is a problem with small caches; it cannot be sidestepped easily. Let the compiler worry about replacement with flush instructions.

- support for prefetch and flush in each level of the hierarchy. Such support might include a separate issue slot dedicated to prefetch and flush operations.

- non-allocating load and store instructions for two reasons: (1) to handle values that exhibit no reuse, and (2) to let programs avoid easily detectable forms of self-interference. For example, the pfld operations on the i860XP have proven useful to the Portland Group's compiler [5].

- programmable fifo's like those proposed in Wulf's WM architecture [11]. These can be viewed as

sophisticated, programmable gather-scatter operations for non-reused values; an alternative view is

that they are tools to let the compiler avoid generating prolog and epilog loops

- · hardware support for coherence between these structures, where possible.

Of course, none of these make sense without a smart compiler. The classic primary cache cannot simply disappear, unless we mandate improvements in basic compiler technology. That seems an unlikely scenario. In short, compilers can discover different styles of locality. Current cache structures support several of these well, but fail to help with others. Further, by forcing all references through a single structure, we

these well, but fail to help with others. Further, by forcing all references through a single structure, we decrease the cache's effectiveness on those references where it could help most. We should build hardware that offers different paths from main memory to registers – paths that match the different styles of locality known to a modern compiler. This lets the compiler provide the hardware with contextual information about locality – information encoded in the choice of instructions.

#### References

- [1] David Callahan, Ken Kennedy, and Allan Porterfield. Software prefetching. In Proceedings of the Fourth International Conference on Architectural Support for Programming Languages and Systems, April 1991.

- [2] Steve Carr. Mcmory-Hierarchy Management. PhD thesis, Rice University, Department of Computer Science, September 1992.

- [3] Dennis Gannon, William Jalby, and Kyle Gallivan. Strategies for cache and local memory management by global program transformation. *Journal of Parallel and Distributed Computing*, 5:587-616, 1988.

- [4] Monica S. Lam, Edward E. Rothberg, and Michael E. Wolf. The cache performance and optimizations of blocked algorithms. In Proceedings of the Fourth International Conference on Architectural Support for Programming Languages and Operating Systems, April 1991.

- [5] Larry Meadows, Steven Nakamoto, and Vincent Schuster. A vectorizing, software pipelining compiler for LIW and superscalar architecture. In *Proceedings of RISC '92*, San Jose, CA, February 1992.

- [6] Todd C. Mowry, Monica S. Lam, and Anoop Gupta. Design and evaluation of a compiler algorithm for prefetching. SIGPLAN Notices, 27(9):62-75, September 1992. In Proceedings of the Fifth International Conference on Architectural Support for Programming Languages and Operating Systems.

- [7] Allan Porterfield. Software Methods for Improvement of Cache Performance on Supercomputer Applications. PhD thesis, Rice University, Department of Computer Science, May 1989.

- [8] Michael E. Wolf and Monica S. Lam. A data locality optimizing algorithm. In Proceedings of the SIGPLAN '91 Conference on Programming Language Design and Implementation, June 1991.

- [9] Michael Wolfe. Iteration space tiling for memory hierarchies. In Proceedings of the Third SIAM Conference on Parallel Processing for Scientific Computing, December 1987.

- [10] Michael Wolfe. More iteration space tiling. In Proceedings of the Supercomputing '89 Conference, 1989.

- [11] William A. Wulf. The WM computer architecture. Computer Architecture News, 16(1):70-84, March 1988.

# A Note on Microprocessors and DRAMs

Douglas W. Clark

Digital Equipment Corporation

doug@ad.enet.dec.com

March 3, 1993

The CPU-DRAM performance gap is clearly a problem on the horizon—Amdahl's Law warns us what will happen if we ignore one portion of the computation while trying to speed up the rest.

-Hennessy and Patterson, CA:AQA, 1990

There is great intuitive appeal in the notion that computers made of rapidly-improving processors combined with slowly-improving memory should themselves have a performance improvement rate between the two, possibly sagging toward the memory rate over time. Although John and Dave say that this problem is "on the horizon," it has clearly been with us for a decade at least. Thus it may be informative to look at the brief historical record.

While parallel-processor systems should see this effect, and bandwidthlimited applications should see this effect, in this note I will look only at access-time-limited applications on uniprocessors. I will also look chiefly at hardware issues.

What we'd like is a time-series of microprocessor implementations of the same architecture running the same workload, in order to avoid the confounding of effects. Each microprocessor should be measured in a computer containing contemporaneous DRAMs. If the Workshop Hypothesis is true, we would expect to see the rate of performance improvement of the computers lie somewhere between the rates of improvement of the processors and the DRAMs; perhaps the rate might even decline over time, as memory speed came to dominate processor speed.

The VAX microprocessor family offers an excellent opportunity to observe this phenomenon empirically. Between 1985 and 1992 a series of eight comparable VAX minicomputer/server systems employed four major VAX microprocessor designs in four generations of semiconductor process, plus several "shrinks" of a design into the next-generation process. The constant workload will be the SPEC benchmarks, vintage '89. Over the seven years, the cycle time of the microprocessors improved almost 20-fold, or at an annual rate of close to 50 percent. The memory subsystem speed barely improved at all during this time (due in part to the steady growth in memory size). Thus the memory access time for the first VAX microprocessor was 2 or 3 cycles, and for the most recent ones, it was more like 60 cycles. But contrary to the Workshop Hypothesis, the performance of the computers, as measured by SPECmarks, improved at an annual rate of 75 percent.

Here's another piece of data from two non-microprocessor VAXes I studied during the Reagan era. The VAX-11/780 had a cycle time of 200 nanoseconds, and took 6 cycles to access main memory on a cache miss. The more recent VAX 8800 had a cycle time of 45 nanoseconds and took 18 cycles to access memory. Yet in comparative measurements of these machines in timesharing applications, the average number of cycles-per-instruction spent waiting for memory actually declined.

What goes on here? Both pieces of evidence—the microprocessor benchmark time series and the big-machine timesharing comparison—seem to refute the hypothesis.

The principal and obvious answer is that the use of caches has more than compensated for the increasing performance gap. Caches, after all, make most accesses to main (DRAM) memory simply disappear. In the VAX microprocessor case, the number of cache levels between processor and main memory increased over the seven-year history from zero to two. At the same time, cache size and bandwidth increased, and more sophisticated buffering schemes were used. In the timesharing comparison, the 8800 had a cache 8 times bigger than the 780's, with bigger blocks and better write-buffering.

I suppose one might object to these data on the grounds that VAX is a high-CPI architecture to begin with, and so the Workshop Effect would be seen much more weakly than in a proper modern RISC family. One might further object that the SPEC benchmarks do not seriously challenge the memory system in any case. Neither objection holds water. The memory-

waiting component is certainly a smaller portion of average instructionexecution time in a VAX than in a RISC, but remember that the data didn't show weak evidence for the Workshop Effect, they showed contrary evidence! (Is there a RISC time series that does demonstrate the effect?) And while a few of the SPEC benchmarks do quite well in modest-sized caches, some do not; recall also that the VAX microprocessor history includes machines with trivial caches and one with no cache.

To be sure, if one simply took the microprocessor of 1985 and mapped it directly into the technology of 1992, changing only its cycle time, the result would be a computer that spent nearly all of its time waiting for memory. But technology improvement gives us more than cycle time: it gives us logic density, and more density leads to bigger caches, more levels of cache, fancier buffering schemes, and other organizational improvements.

There are serious issues here, of course. The accretion of cache levels and write buffers adds significantly to the complexity of an implementation, even as it increases performance. Cost may increase too, as expensive board-level secondary and tertiary caches become necessary.

But as the VAX history shows, the Workshop problem, while quite real, has not been so severe as to have required extraordinary efforts in engineering or research. Indeed, in my view the hardest technical challenge over this period at Digital has been the steady reduction of the processor cycle time. Ordinary engineering efforts, chiefly in cache design, have been enough to enable system performance improvement to surpass processor performance improvement. Why will caching not continue to work?

At around the time that DRAMs were first used in main memories, there was a concern about a different performance gap: the one between the access times of memory and disks. Several "gap-filling" technologies were proposed (remember magnetic bubbles? charge-coupled devices?), but the gap was ultimately filled by greatly increasing the size of DRAM memory, thanks to its rapidly improving density and cost. The same thing seems to have happened in the short history of the processor-DRAM performance gap. Perhaps the future will be different, and radical new approaches will be needed. But proponents of this view must explain why, at least in the uniprocessor case, this has not been true in the past.

# Compiler Support for Reducing, Hiding and Eliminating Memory Latency

Susan J. Eggers

Department of Computer Science and Engineering

University of Washington

# 1 Prefetching

Current compiler algorithms for cache-based prefetching can fairly accurately predict cache misses that depend on the configuration of the cache, i.e., capacity and conflict misses, by analyzing spatial and temporal reuse of data. Based on the analysis they only prefetch data that will miss in the cache, never prefetch data that is not used and isolate loop iterations that require prefetched data from those that don't via loop splitting (for example, [7]). They sometimes do less well in prefetching on shared memory machines, because of their greater sensativity to additional memory traffic and shared data invalidations[8].

Future work might include the following:

- Since memory latencies will continue to increase relative to CPU speeds, we should pursue compiler-based, rather than hardware solutions for prefetching. Compiler-based prefetching can better handle long latencies, because of its ability to examine a longer window of both instructions and data. It should be particularly successful, when coupled with new static branch prediction heuristics[2].

- Reduce the uniprocessor cache conflicts induced by prefetching via victim caches and increased associativity.

- Develop special prefetching algorithms for shared data, because shared data incurs misses caused by asynchronous (with respect to the CPU) invalidations. For example, exclusive prefetching of shared data with tight use-def sequences.

# 2 Code Scheduling with respect to Loads