# The WM Computer Architectures: Military Standard Manual

Anita K. Jones Rohit Wad

Computer Science Report No. TR-90-19 August 1990

This work was supported in part by the Defense Advanced Research Agency (DARPA) under contract number N00014-89-J1699.

# **Abstract**

This report is a military standard definition of the instruction set of the WM family of computer architectures. The WM instruction set architecture supports microconcurrency at the instruction level; i.e. it facilitates the execution of several scalar instructions concurrently. Also, WM supports vector processing; that is, it has single instructions that apply the same operation to a collection of data items. Another interesting feature of the WM architectures is streaming -- a mechanism for asynchronous loads and stores of "vector-like" data, that is, data with a known displacement between successive items. This facility applies to WM's scalar as well as its vector execution units, and has the effect of potentially executing many load/store operations concurrent with the execution of other instructions.

The report has been patterned after the 1750 military standard manual.

# **Table of Contents**

| Do | cument Derivation                       |        |

|----|-----------------------------------------|--------|

| 1. |                                         |        |

|    | 1.1 Scope                               |        |

|    | 1.2 Purpose                             |        |

|    | 1.3 Applicability                       |        |

|    | 1.4 Benefits                            |        |

|    | Referenced Documents                    |        |

| 3. | Definitions                             |        |

|    | 3.1 Address                             |        |

|    | 3.2 Alignment                           | 3      |

|    | 3.3 Arithmetic logic unit (ALU)         | 3      |

|    | 3.4 Bit                                 |        |

|    | 3.5 Byte                                |        |

|    | 3.6 Concurrent operations               |        |

|    | 3.7 Condition code                      |        |

|    | 3.8 Deadlock                            |        |

|    | 3.9 Device                              |        |

|    | 3.10 Domain                             | 3      |

|    | 3.11 Doubleword                         | …૩     |

|    | 3.12 Entry                              | პ      |

|    | 3.13 First-in-first-out queue (FIFO)    |        |

|    | 3.14 Floating execution unit (FEU)      | 4      |

|    | 3.15 Floating point register            |        |

|    | 3.16 General purpose register           |        |

|    | 3.17 Halfword                           |        |

|    | 3.18 Handler task                       | 4      |

|    | 3.19 Input/output (I/O)                 | 4      |

|    | 3.20 Instruction                        |        |

|    | 3.21 Integer execution unit (IEU)       | 4      |

|    | 3.22 Instruction fetch unit (IFU)       | 4      |

|    | 3.23 Instruction set architecture (ISA) |        |

|    | 3.24 Interrupt                          |        |

|    | 3.25 Load prefetch                      |        |

|    | 3.26 Memory                             |        |

|    | 3.27 Micro-concurrency                  |        |

|    | 3.28 Multi-computer                     |        |

|    | 3.30 Operation code (OPCODE)            | Q      |

|    | 3.31 Prefetch                           | 5<br>= |

|    | 3.32 Program counter (PC)               |        |

|    |                                         |        |

|    | 3.33 Register                           |        |

|    |                                         |        |

|    | 3.35 Right                              |        |

|    | 3.36 Stack                              |        |

|    | 3.37 Stream                             |        |

|    | 3.38 Stream mode                        |        |

|    | 3.39 Streaming                          |        |

|    | 3.40 Task                               | ₩      |

|    | 3.41 Typed protection                          |           |     |

|----|------------------------------------------------|-----------|-----|

|    | 3.42 Vector execution unit (VEU)               |           |     |

|    | 3.43 Vector register                           | 6         |     |

|    | 3.44 Word                                      |           |     |

|    | 3.45 Zero register                             |           |     |

| 4. | General Requirements                           | .7        |     |

| •• | 4.1 Function units                             |           |     |

|    | 4.1.1 Scalar execution units                   |           |     |

|    | 4.1.1.1 Data dependency rule                   |           |     |

|    | 4.1.2 Vector execution unit                    |           |     |

|    | 4.1.3 Instruction fetch unit                   | .1        | 0   |

|    | 4.1.4 Parameter bypass                         | .1        | 1   |

|    | 4.1.5 Streaming                                | 1         | 2   |

|    | 4.1.5 Streaming to and from the IEU and FEU    | 1         | 2   |

|    | 4.1.5.2 Streaming to and from the VEU          | • •       | 3   |

|    | 4.1.5.2 Streaming to and nomine veo            | -1        | 3   |

|    | 4.1.6 Special instructions and synchronization | . !<br>-1 | ı   |

|    | 4.1.7 Deadlock                                 | . !       | -   |

|    | 4.2 Data formats                               | . I       | D   |

|    | 4.2.1 Data alignment                           | ۱.<br>د   | 5   |

|    | 4.2.2 Data sizes                               | ٦.        | 5   |

|    | 4.2.3 Data Types                               | .1        | 5   |

|    | 4.2.3.1 Boolean values                         |           |     |

|    | 4.2.3.2 Signed integer values                  | .1        | 6   |

|    | 4.2.3.3 Floating point values                  | .1        | 6   |

|    | 4.3 Instruction formats                        | .1        | 6   |

|    | 4.3.1 Literals in instructions                 | .1        | 6   |

|    | 4.3.2 Instruction format notation              | .1        | 6   |

|    | 4.3.3 Integer format instructions              | .1        | 6   |

|    | 4.3.4 LOAD/STORE format instructions           | .1        | 6   |

|    | 4.3.5 Floating point format instructions       | .1        | 7   |

|    | 4.3.6 Control format instructions              | .1        | 7   |

|    | 4.3.7 Vector format instructions               | .1        | 8   |

|    | 4.3.8 Special format instructions              |           |     |

|    | 4.4 Registers and support features             | .1        | 8   |

|    | 4.4.1 General registers                        | .1        | 8   |

|    | 4.4.2 Special registers                        | .1        | 2   |

|    | 4.4.3 Stack                                    | .1        | ۶   |

|    | 4.5 Memory                                     |           |     |

|    | 4.5.1 Memory reads & writes                    | 1         | Ç   |

|    | 4.5.1 Memory reads & writes                    | 。,        | r   |

|    | 4.6.1 Task state                               | ے<br>ص    |     |

|    |                                                |           |     |

|    | 4.6.2 Protection                               | <br>^     | -   |

|    | 4.6.3 Address mapping                          | 2         | ÷   |

|    | 4.6.4 Initialization of the machine            |           |     |

|    | 4.7 Devices                                    | 2         | 4   |

|    | 4.8 Input/output                               | 2         |     |

|    | 4.9 Traps (exceptions) and interrupts          | 2         | . 5 |

|    | 4.9.1 Interrupts                               | 2         | . 5 |

|    | 4 9 2 Trans                                    | 2         | 6   |

|    | 4.9.3 Exceptions                                  | 2        | 7      |

|----|---------------------------------------------------|----------|--------|

|    | 4.9.3.1 Integer exceptions                        | .2       | 7      |

|    | 4.9.3.2 Load/Store exceptions                     | .2       | 7      |

|    | 4.9.3.3 Control exceptions                        | .2       | 7      |

|    | 4.9.3.4 Floating point exceptions                 | .2       | 8      |

| 5. | Detailed Requirements                             | .2       | 9      |

|    | 5.1 Instruction set notation                      | .2       | 9      |

|    | 5.1.1 Registers                                   | .2       | 9      |

|    | 5.1.1.1 General registers                         |          |        |

|    | 5.1.1.1.1 IEU registers                           | .2       | 9      |

|    | 5.1.1.1.2 FEU registers                           |          |        |

|    | 5.1.1.1.3 VEU registers                           | .3       | 0      |

|    | 5.1.1.2 Implementation dependent registers        | .3       | 0      |

|    | 5.1.1.3 Special registers                         | .3       | 1      |

|    | 5.1.2 Symbols                                     | .3       | 1      |

|    | 5.1.2.1 "="                                       |          |        |

|    | 5.1.2.1.1 Symbols to the left of ←                |          |        |

|    | 5.1.2.1.2 Symbols to the right of ←               | .3       | 1      |

|    | 5.1.2.2 "←" The assignment operator               | .3       | 1      |

|    | 5.1.2.2.1 Symbols to the left of ←                |          |        |

|    | 5.1.2.2.2 Symbols to the right of ←               | .3       | 2      |

|    | 5.1.2.3 ":" The bit selection operator            | .3       | 3      |

|    | 5.1.2.4 "::" The operator-argument operator       | .3       | 3      |

|    | 5.1.2.5 "Isl" The arithmetic shift left operator  | .3       | 3      |

|    | 5.1.2.6 "asr" The arithmetic shift right operator | .3       | 3      |

|    | 5.1.2.7 "&&" The bitwise and operator             | .3       | 3      |

|    | 5.1.2.9 "  " The bitwise or operator              | .3       | 3      |

|    | 5.1.2.10 "or" The logical or operator             | .3       | 3      |

|    | 5.1.2.11 "EQV" The bitwise equivalence operator   | .3       | 3      |

|    | 5.1.2.12 "+, -, -', *, /, /""                     | .3       | 3      |

|    | 5.1.2.13 "=, <>, <, <=, >=, >"                    | .3       | 3      |

|    | 5.1.2.14 "\phi"                                   | .3       | 3      |

|    | 5.1.3 Functions                                   |          |        |

|    | 5.1.4 Operations                                  |          |        |

|    | 5.1.5 Miscellaneous values                        |          |        |

|    | 5.2 Mnemonic conventions                          |          |        |

|    | 5.3 Execution semantics                           | .ა       | 0      |

|    | 5.4 Integer Arithmetic and Logical Instructions   | .პ<br>ი  | 0      |

|    | 5.4.1 op = +                                      | ა<br>ი   | 0      |

|    | 5.4.2 op = asl                                    | ن.<br>د  | 0      |

|    | 5.4.3 op = <                                      | ۍ.<br>د  | 9      |

|    | 5.4.4 op =                                        | 4<br>A   | 4      |

|    | 5.4.5 op = -'                                     | 4<br>1   | 1      |

|    | 5.4.6 op = and                                    | ,44<br>A | 2      |

|    | 5.4.7 op = or                                     | 4<br>A   | ن<br>ا |

|    | 5.4.8 op = eqv                                    | 4<br>A   | 4      |

|    | 5.4.9 op = *                                      | 4<br>s   | 0      |

|    | 5.4.10 op = /                                     |          |        |

|    | 5.4.11 op = /'                                    | 4        | 1      |

|     | 5.4.12 op = =                                            | 4 {      | 3             |

|-----|----------------------------------------------------------|----------|---------------|

|     | 5.4.13 op = <>                                           | 4 (      | 3             |

|     | 5.4.14 op = <=                                           | 5 (      | )             |

|     | 5.4.15 op = >=                                           | 5 .      | 1             |

|     | 5.4.16 op = >                                            | 5 7      | 2             |

| 5.5 | Floating Point Instructions                              | 5 (      | 3             |

|     | 5.5.1 op = <                                             | 5        | 4             |

|     | 5.5.2 op = +                                             | 5 !      | 5             |

|     | 5.5.3 op =                                               | 5 (      | 6             |

|     | 5.5.4 op = -'                                            | 5        | 7             |

|     | 5.5.5 op = *                                             | 5        | 8             |

|     | 5.5.6 op = /                                             | 5        | 9             |

|     | 5.5.7 op = /'                                            | 6        | 0             |

|     | 5.5.8 op = nop                                           | 6        | 1             |

|     | 5.5.9 op = nop'                                          | 6        | 2             |

|     | 5.5.10 op = =                                            | 6        | 3             |

|     | 5.5.11 op = <>                                           | .6       | 4             |

|     | 5.5.12 op = <=                                           | .6       | 5             |

|     | 5.5.13 op = >                                            | .6       | 6             |

|     | 5.5.14 op = >=                                           | .6       | 7             |

| 5.6 | Vector Instructions: Integer, Logical and Floating Point | .6       | 8             |

|     | 5.6.1 op = iadd                                          | .6       | 9             |

|     | 5.6.2 op = isub                                          | ./       | O.            |

|     | 5.6.3 op = imul                                          | ./       | 7             |

|     | 5.6.4 op = idiv                                          | ./       | 2             |

|     | 5.6.5 op = iasl                                          | .1<br>7  | <u>ح</u>      |

|     | 5.6.6 op = ieql                                          | ./       | 4             |

|     | 5.6.7 op = ineq                                          | ./       | 0             |

|     | 5.6.8 op = igtr                                          | ./<br>7  | 7             |

|     | 5.6.9 op = igeq                                          | ./<br>7  | 0             |

|     | 5.6.10 op = ilss                                         | . /<br>7 | 0             |

|     | 5.6.11 op = ileq                                         | ٠,       | n             |

|     | 5.6.12 op = iaddC                                        | ο.<br>Ω  | 4             |

|     | 5.6.13 op = iandC                                        | φ.       | 7             |

|     | 5.6.14 op = iorC                                         | Ω.       | 2             |

|     | 5.6.15 op = ieqvC                                        | υ.<br>Ω  | 4             |

|     | 5.6.16 op = isubC                                        | Ω.       | 5             |

|     | 5.6.17 op = imulC                                        | Ω.       | 2             |

|     | 5.6.19 op = iaslC                                        | .υ<br>Ω  | 7             |

|     | 5.6.20 op = ieqlC                                        | .υ<br>Ω  | ٠<br>2        |

|     | 5.6.20 op = ieqi0                                        | Ω        | a             |

|     | 5.6.21 op = ineqC                                        | ٥        | n.            |

|     | 5.6.22 op = igtrC                                        | ح<br>۵   | ں<br>1 ا      |

|     | 5.6.23 op = igeqC                                        | ټ<br>۵   | 9             |

|     | 5.6.25 op = ileqC                                        | ت<br>۵   | <u>ب</u><br>ب |

|     | 5.0.6 pg foddo                                           | چ<br>۵   | ري<br>الانا   |

|     | 5.6.26 op = faddC                                        | <br>O    | +<br>2        |

|     | 5.6.27 op = fsubC                                        | <br>0    | ر<br>ء ،      |

|     | 0.0.40 QD = IIIIQQ                                       | J        | U             |

| 5.6.29 op = fdivC                           | <del>)</del> 7 |

|---------------------------------------------|----------------|

| 5.6.30 op = fleqC                           | )8             |

| 5.6.31 op = flssC                           | 99             |

| 5.6.32 op = fgeqC1                          | 100            |

| 5.6.33 op = fgtrC1                          | 101            |

| 5.6.34 op = fneqC                           | 102            |

| 5.6.35 op = feqlC                           | 103            |

| 5.6.36 op = fadd                            | 104            |

| 5.6.37 op = fsub                            | 105            |

| 5.6.38 op = fmul                            | 106            |

| 5.6.39 op = fdiv                            | 107            |

| 5.6.40 op = feql                            | 108            |

| 5.6.41 op = fneq                            | 109            |

| 5.6.42 op = fgtr                            | 110            |

| 5.6.43 op = fgeq                            | 111            |

| 5.6.44 op = flss                            | 112            |

| 5.6.45 op = fleq                            | 113            |

| 5.7 Load and Store Instructions             | 114            |

| 5.8 Control Flow Instructions               | 116            |

| 5.9 Special Instructions                    | 118            |

| 5.9.1 Jumpl                                 | 118            |

| 5.9.2 Calli                                 | 119            |

| 5.9.3 EReturn                               | 120            |

| 5.9.4 Streaming to and from the IEU and FEU | 121            |

| 5.9.5 Streaming to and from the VEU         | 124            |

| 5.9.6 ASSERT                                | 127            |

| 5.9.7 FASSERT                               | 128            |

| 5.9.8 FLDMOV                                | .129           |

| 5.9.9 FLDMOVX                               | .130           |

| 5.9.10 FFB                                  | .131           |

| 5.9.11 CVTIF                                | .132           |

| 5.9.12 CVTFI                                | .133           |

| 5.9.13 TIF                                  | .134           |

| 5.9.14 TFI                                  | .135           |

| 5.9.15 TIV                                  | .136           |

| 5.9.16 TIVx                                 | .137           |

| 5.9.17 TFV                                  | .138           |

| 5.9.18 LLH                                  | .139           |

| 5.9.19 SLL                                  | .140           |

| 5.9.20 ReadPCW                              | .141           |

| 5.9.21 WritePCW                             | .142           |

| 5.9.22 Consumel                             | .143           |

| 5.9.23 ConsumeF                             | .144           |

| 5.9.24 SYNCH                                | .145           |

| 5.9.25 LoadM                                | .146           |

| 5.9.26 FLoadM                               | 147            |

| 5.9.27 VLoadM                               | 148            |

| 5.9.28 StoreM                               | 140            |

| 5.9.29 FStoreM                              | 150            |

| J.3.23 FOIDIEW                              | ., 50          |

| 5.9.30 VStoreM                               | 151 |

|----------------------------------------------|-----|

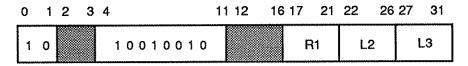

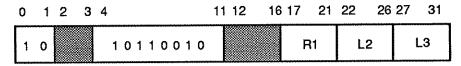

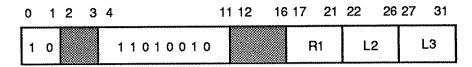

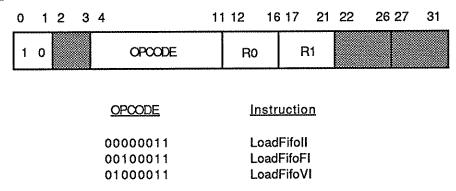

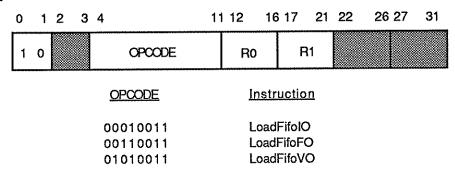

| 5.9.31 LoadFifoII, LoadFifoFI, LoadFifoVI    | 152 |

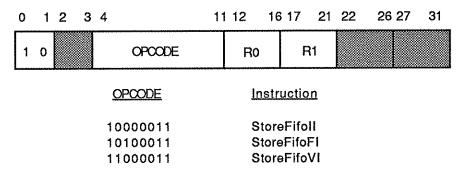

| 5.9.32 LoadFifoIO, LoadFifoFO, LoadFifoVO    | 153 |

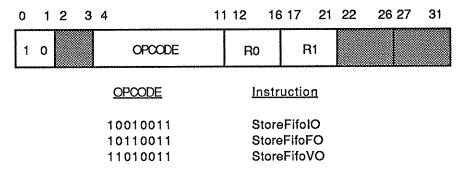

| 5.9.33 StoreFifoII, StoreFifoFI, StoreFifoVI | 154 |

| 5.9.34 StoreFifoIO, StoreFifoFO, StoreFifoVO | 155 |

| 5.9.35 LoadCTX                               | 156 |

| 5.9.36 StoreCTX                              | 157 |

| 5.9.37 SwapCTX                               | 158 |

| 5.9.38 SwapLT                                | 159 |

|                                              |     |

# **Document Derivation**

This report is a draft of the military standard manual for the WM Computer Architectures. The report is derived from "The WM Computer Architectures: Principles of Operation, Wm. A Wulf" (Computer Science Report No. TR-90-02, University of Virginia).

# 1. Scope and Purpose

### 1.1 Scope

This standard defines the WM instruction set architecture family. It does not define specific implementation details.

### 1.2 Purpose

The purpose of this document is to establish a single architecture family suitable for a spectrum of military applications from embedded signal processors to large-scale, high-performance, general purpose multi-computers.

### 1.3 Applicability

This standard is intended to be used to define only the instruction set architecture of a family of computers. System-unique requirements such as speed, weight, power, additional input/output commands, and environmental operating characteristics are defined in the computer specification for each computer. Application of this standard is not restricted to any particular function or specific hardware implementation or specific family member. This standard is not restrictired to implementations of *standalone* computers such as a mission computer or fire control computer.

#### 1.4 Benefits

The expected benefits of this standard instruction set architecture family are the use and re-use of available support software such as compilers and instruction level simulators and the ability to tailor the architecture and implementation to the specific mission capability. Other benefits may also be achieved such as: (a) reduction in total support software gained by the use of a standard instruction set architecture family for two or more computers in a weapon systems, and (b) software development independent of hardware development.

# 2. Referenced Documents

IEEE Floating Point Standard 754.

# 3. Definitions

#### 3.1 Address

An address on the WM architecture is an <u>i</u>-bit signed value which identifies a location in memory where information is stored. Memory is 8-bit byte addressed. Note that addresses are *signed*; valid addresses lie in the range  $-2^{i-1}$  ...  $(2^{i-1}-1)$ .

#### 3.2 Alignment

All instructions are 32-bits in length, and the Program Counter (PC) always specifies a word-aligned address. Default instruction sequencing is linear and increasing (i.e., the execution of the instruction at address XXX+4 follows the execution of the instruction at address XXX).

### 3.3 Arithmetic logic unit (ALU)

That portion of hardware in an execution unit in which arithmetic and logical operations are performed.

#### 3.4 Bit

Contraction of binary digit; may be either zero or one. In information theory, a binary digit is equal to one binary decision or the designation of one of two possible values or states of anything used to store or convey information.

### 3.5 Byte

A group of eight binary digits.

#### 3.6 Concurrent operations

Operations specified by instructions are executed concurrently. The IFU, IEU, FEU and VEU exeucute instructions in parallel. The IEU and FEU have two pipelined ALUs which perform operations in parallel. Streamed LOAD/STORE operations imply potential concurrent performance of operations.

#### 3.7 Condition code

Scalar execution units can perform relational operations which generate condition codes that are to be consumed by conditional jump and consume instructions.

#### 3.8 Deadlock

The condition in which two or more units cannot execute further beacuse each depends upon an action to be taken by another such unit.

#### 3.9 Device

A "device" is one hardware-understood page type. Device-specific operations are performed by reading and storing bit patterns into memory-mapped device registers in such a page.

#### 3.10 Domain

An addressing domain consists of a flat, paged address space; each page in this space has two independent properties: (1) address translation information, and (2) typed protection information; these are defined by a map table and protection table respectively. Pointers to these tables are part of the task state in the TCB. Two tasks can share the same address space but may have different access to portions of that space.

### 3.11 Doubleword

Sixty-four bits.

# 3.12 Entry

A type of page. It is a generalization of the "trap vector" of some other architectures. An "entry call", ECall, instruction may reference (only) an entry page and requires "call rights" to that page. Traps are ECall's on predefined locations (in "page 0").

### 3.13 First-in-first-out queue (FIFO)

A queue of items such that when the queue is read the value returned is the least recently enqueued item which has not been read and as a side effect it is removed from the queue.

#### 3.14 Floating execution unit (FEU)

That portion of a computer that performs floating point arithmetic and relational instructions.

#### 3.15 Floating point register

A register that may be used for floating point arithmetic and relational operations and general storage of temporary floating point data.

# 3.16 General purpose register

A register that may be used for integer arithmetic, relational and logical operations, indexing, shifting, and general storage of temporary integer and logical data.

#### 3.17 Halfword

Sixteen bits.

#### 3.18 Handler task

The task which is dispatched to handle, i.e. react to, a specific kind of interrupt.

### 3.19 input/output (I/O)

That portion of a computer which interfaces to the external world.

#### 3.20 Instruction

A 32-bit word of program code which tells the WM computer what to do.

### 3.21 Integer execution unit (IEU)

That portion of a computer that initiates singleton memory reads and writes and performs integer arithmetic, relational and logical instructions.

### 3.22 Instruction fetch unit (IFU)

That portion of a computer which fetches instructions and dispatches some of them for execution in other units. The IFU executes certain special and control instructions.

### 3.23 Instruction set architecture (ISA)

The attributes of a digital computer as seen by a machine (assembly) language programmer. ISA includes the processor and input/output instruction sets, their formats, operation codes, and addressing modes; memory management and partitioning if accessible to the machine language programmer; the speed of accessible clocks; interrupt structure; and the manner of use and format of all registers and memory locations that may be directly manipulated or tested by a machine language program. This definition excludes the time or speed of any operation, internal computer partitioning, electrical and physical organization, circuits and components of the computer, manufacturing technology, memory organization, memory cycle time, and memory bus widths.

### 3.24 Interrupt

A special control signal that suspends the normal flow of the processor operations and allows the processor to respond to a logically unrelated or unpredictable event. An interrupt is essentially a forced context swap.

### 3.25 Load prefetch

The case in which a load is started well before a memory data being read is needed. The purpose is to reduces the effect of cache misses and long memory access latency.

#### 3.26 Memory

That portion of a computer that holds data and instructions and from which they can be accessed.

# 3.27 Micro-concurrency

The ability to dispatch multiple operations per cycle.

#### 3.28 Multi-computer

A computer composed of multiple WM computer processors capable of communicating with one another via messages.

#### 3.29 Normal mode

A state of a scalar execution unit FIFO register in which the location of data values currently in the FIFO or next to pass through the FIFO are specified by LOAD/STORE instructions.

# 3.30 Operation code (OPCODE)

That part of an instruction that defines the machine operation to be performed.

#### 3.31 Prefetch

Because the IFU runs concurrently with the execution units, it may prefetch the next instruction before the execution unit to execute the current instruction has commenced to do so.

### 3.32 Program counter (PC)

A register in the IFU that holds the address of the next instruction to be fetched.

#### 3.33 Register

A device in an execution unit for the temporary storage of one or more words to facilitate arithmetic, logical, or transfer operations.

### 3.34 Reserved

Must not be used.

# 3.35 Right

Permission to perform a specified access or action.

#### 3.36 Stack

A sequence of memory locations in which data may be stored and retrieved on a last-in-first-out (LIFO) basis.

#### 3.37 Stream

A linear sequence of memory items, all of the same size and type, that start at a known address and are spaced a constant distance (stride) from each other.

#### 3.38 Stream mode

A state of an execuion unit FIFO register in which the location of data values currently in, or next to pass through, the FIFO are specified by a stream instruction.

#### 3.39 Streaming

Asynchronous loads and stores of *vector-like* data, that is, data with a known displacement between successive items. A single instruction can be executed to cause a *stream* of such data items to be delivered to any of WM's execution units. Data items can then be processed at the speed of the consuming algorithm. Streaming permits many load/store operations to execute concurrently with other instructions.

#### 3.40 Task

A task is a "thread of control". The WM hardware supports a hardware-defined "task control block", TCB, to hold the state of the task when it is not executing.

#### 3.41 Typed protection

Each page is typed; only instructions appropriate to the type are permitted to reference a page. A task must have rights appropriate for the instruction.

#### 3.42 Vector execution unit (VEU)

That portion of a computer that performs vector arithmetic and relational instructions.

### 3.43 Vector register

An (implementation-dependent size) block of registers that may be used for arithmetic and logical operations and general storage of temporary data.

#### 3.44 Word

Thirty-two bits.

#### 3.45 Zero register

A register that which has the value zero whenever read.

# 4. General Requirements

### 4.1 Function units

WM has three execution units under common control of the instruction fetch unit. The instruction set is partitioned so that each instruction is executed by a particular unit.

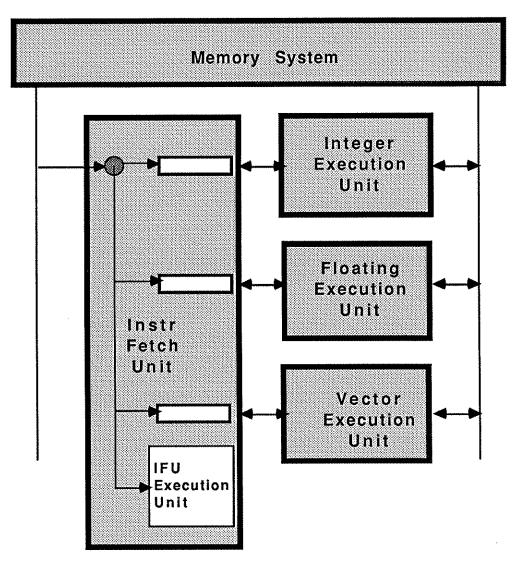

Figure 1: WM System Components

As shown in Figure 1<sup>1</sup>, the IFU can be thought of as enqueuing instructions for execution by each of the other execution units in a set of FIFOs. In addition the IFU

<sup>&</sup>lt;sup>1</sup>This figure and the several that follow it are intended to provide an intuitive, model implementation to explicate the semantics of the WM instruction set. Actual implementations may or, more likely, may not have a similar structure.

executes certain instructions itself, notably control instructions. The other execution units dequeue instructions and execute them as rapidly as their respective implementations permit.

### 4.1.1 Scalar execution units

The scalar data manipulation instructions of WM are implemented by the integer and floating point execution units; each such instruction specifies 3 source operands, 2 operators, and a destination register, and evaluate an assignment of the form:

$$R0 := (R1 \ op1 \ R2) \ op2 \ R3$$

The source operand of integer/logical instructions may be the contents of a register, the contents of an input FIFO, or an unsigned literal; the destination may be either a register or an output FIFO. The source operands of a floating point instruction may be either a register or an input FIFO, and the destination may be either a register or an output FIFO. Floating literals, other than zero, are not supported as source operands.

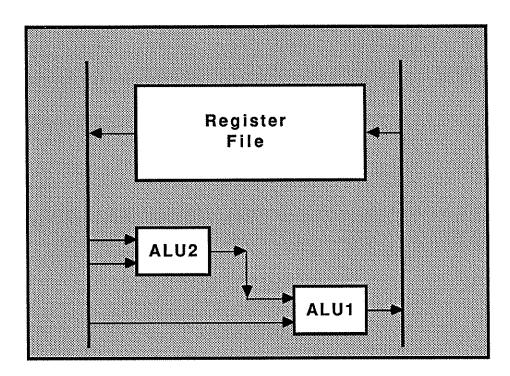

The integer and floating point execution units of WM are implemented as a pair of pipelined ALUs, as shown in Figure 2. In general, while the second (outer, op2) operation of one instruction is being executed in ALU2, the first (inner, op1) operation of the successor instruction is being executed in ALU1. Thus one instruction (two operations) can be dispatched to each of the scalar execution units each cycle.

Integer/logical instructions refer to the integer registers; floating point instructions refer to the floating point registers. Conversion instructions refer to one register of each type as appropriate. In the floating point execution unit literals cannot be specified as operands; only floating register operands are permitted.

Relational operators produce their left operand as a result. They also produce a boolean value. If two relationals exist in the same instruction, their boolean values are either AND'd or OR'd together and written to the conditional bit under control of a PCW bit. Otherwise, the single boolean value sets the condition bit. In either case, if the boolean result is False, then the instruction's register write and exception conditions are nullified. Software must guarantee that exactly one instruction with relational operations is specified before each conditional jump or consume instruction. The number of instructions containing relationals preceding the associated conditional jump or consume instruction must not exceed the size of the condition bit FIFO.

Figure 2: Scalar Execution Unit Structure

### 4.1.1.1 Data dependency rule

The pipelined structure of the WM scalar execution units induces the data dependency rule:

The result of an instruction is not available as an operand of the inner operation of the following instruction for the same execution unit. The value of an inner operand is specifically independent of the effect of the previous instruction.

Valid programs must obey this rule. Clever programs will exploit it.

Data dependencies are defined with respect to instructions for the *same* execution unit!

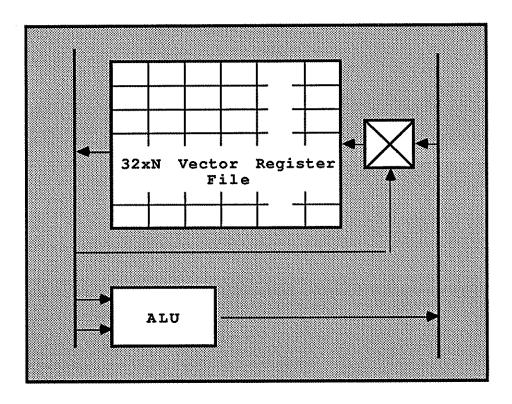

#### 4.1.2 Vector execution unit

The Vector Execution Unit supports integer, logical and floating point operations on "blocks" of N  $\underline{v}$ -bit items, where N is an implementation defined parameter.

The vector instructions of WM specify a single operation. The performance of the operation is conditioned on an item-by-item basis by a boolean vector specified by the third source operand. The boolean "mask" determines whether components of the result vector are affected by the operation. In general, the form of a vector instruction is

R0 := (R1 op R2) if R3

Each instruction performs the computation

for all k,  $0 \le k < N$ ,  $R0_k := if R3_k \ne 0$  then  $(R1_k op R2_k)$  else  $R0_k fi$

At least conceptually all of these operations are performed simultaneously; an implementation may choose to perform them serially (as with a single pipelined ALU), but this is not visible to the program.

The vector relational operations are different from their counterparts for the IEU and FEU; they do not produce a condition code. Rather they produce a vector of boolean values in the specified destination register -- such a vector may, for example, be used to control a subsequent conditional vector operation.

Figure 3: Vector Execution Unit

#### 4.1.3 Instruction fetch unit

The instruction fetch unit fetches sequential instructions from memory based on the value of the Program Counter. Fetched instructions are either executed by the IFU or quequed for execution by the one execution unit capable of executing the fetched instruction. The IFU executes selected special instructions and all control instructions. Control instructions replace the Program Counter with a new value, the target address.

There are eight conditional jumps associated with the two condition FIFOs: "Jump True" and "Jump False" for each of the integer and floating conditions; each jump may predict whether the jump will be taken or not. Conditional Jumps "consume" a condition bit generated by a relational operation. Valid programs must guarantee that exactly one instruction containing a relational operation is executed for each conditional jump.

There are twelve conditional jumps associated with the streaming facility of the machine; these support jumps on the on "stream count not zero" for each of the input and output streams.

There are two call instructions: Call and ECall. Call simply stores the current PC in register 4 and jumps to the specified destination. ECall performs the function of a "supervisor call".

ECall provides the functionality of "supervisor call" in other architectures; it has three effects:

- (1) it changes the protection table pointer to that contained in the entry page (note, the map table pointer is not changed),

- (2) it jumps indirectly through the specified PC-relative location, and

- (3) it saves the prior protection table pointer and program counter in a special protected stack area.

The address specified in by the PC-relative target address must be that of an "Entry Page", and that the task executing the ECall must have "call rights" to this page.

Three instructions that affect control flow are encoded among the "special" instructions because they do not need to specify a PC-relative address: they are Jumpl (Jump Indirect), Call (Call Indirect) and EReturn (Return from ECall).

### 4.1.4 Parameter bypass

Register 1 in each of the scalar execution units is also a FIFO, with somewhat different properties than that of register 0. Specifically, a value stored (computed) into the register 1 output FIFO is immediately enqueued in the register 1 input FIFO. As with register 0, items are dequeued simply by using register 1 as a source operand.

Register 1 can hold a short queue of temporary values -- in particular parameters during a subroutine call. The caller enqueues actual parameters, and the called routine dequeues formals.

A call consists of at least:

```

r1 := p1 -- 1st parameter

..

r1 := pn -- Nth parameter

call subr -- implicitly, r4 := PC

```

#### 4.1.5 Streaming

The WM computer architecture supports a feature called *streaming*. Streaming is a method of loading and storing structured data elements without having to do explicit address computations for each element. It assumes a vector of data elements are present, or are to be created, in memory, and that they are a constant stride (number of bytes) apart from each other. Stream instructions are used to read/write such vectors from/to FIFOs. Streaming is conceptually identical for the IEU, FEU, and VEU, but the implications with respect to the VEU are slightly different and will be discussed separately.

Either register 0 or register 1 in each of the execution units may be used in stream mode. Streaming is the only mode for the VEU; each of these registers supports two modes of operation in the IEU and FEU, normal and streaming mode respectively. Normal mode for register 0 is the LOAD/STORE mode. Normal mode for register 1 is the parameter bypass mode. Stream mode is identical for both registers in all execution units.

When in streaming mode, the first/next data transfer occurs due to a single "start streaming" instruction which initiates the transfer of the entire stream. Asynchronous "stream control units" compute the addresses of the "next" data item(s) and initiate the transfer.

When streaming, data is removed from the input FIFOs in the same manner as in normal mode -- that is, by instructions that reference register 0 or register 1. Similarly, by designating register 0 or register 1 as the destination of an instruction, data is inserted into the output FIFO (same as the normal mode for register 0 but different from register 1's normal mode.) If streaming is performed only with register 0, programs that exploit streaming are functionally identical to those that do not, except that no LOAD/STORE instructions appear in the streaming programs. If register 1 is involved in a stream, however, the parameter bypass capability is not available.

#### 4.1.5.1 Streaming to and from the IEU and FEU

There are 15 instructions that initiate streaming operations to the IEU and FEU. These are analogous to the 15 types of loads and stores. They specify data as integer or floating point and size of the data items. The operands of streaming operations specify a base address (R1), a count<sup>1</sup> (RL2), a stride<sup>2</sup> (RL3), and which FIFO to use (0 or 1).

Finally, there are seven instructions to stop streaming operations. These instructions stop input or output streaming and flush the relevant FIFOs.

A stop instruction applied to an output FIFO will complete pending memory writes (where data is available), reset the stream count, remove any extra addresses which have been calculated and restore the FIFO to normal -- i.e., non-streaming -- mode. A

<sup>&</sup>lt;sup>1</sup> A count of -1 is defined to be an infinitely long stream. That is, the stream will continue until a stop streaming instruction is performed.

<sup>&</sup>lt;sup>2</sup> In bytes.

stop instruction applied to an input FIFO will take the counterpart action, discarding all data currently in the FIFO.

Only one input stream and one output stream per FIFO may coexist. This imposes a maximum of eight (four input and four output) simultaneous streams for the integer and floating point units.

An input FIFO is considered to be in streaming mode until all of its data has been consumed or until the stream is halted by a stop streaming instruction. An output FIFO is considered to be in streaming mode until all data has been written to it or until the stream is halted by a stop streaming instruction.

Note that unlike LOAD/STORE instructions, consistency is not guaranteed between input and output streams. More specifically, when streaming both in and out of the same locations, the memory system has no responsibility of maintaining the order between memory reads and writes.

Streaming instructions may cause Page Fault exceptions. If a Page Fault exception occurs during a memory read, the exception is not raised until an attempt to read register 0 or 1 unsuccessfully. If such an exception occurs during a write of register 0 or 1 (to be written into memory), the exception is raised immediately.

# 4.1.5.2 Streaming to and from the VEU

Streaming to and from the VEU is conceptually similar to streaming to and from the IEU and FEU; however, it differs in a few details:

- data is moved in "blocks" of N entities.

- because there are no LOAD or STORE instructions for the VEU, there is only one "mode" for the VEU FIFOs. Note specifically that v1 cannot be used as a parameter bypass.

- because the VEU supports integer, logical, and floating operations, appropriate streaming operations are provided to do the proper form of operand expansion or contraction.

- because the operations of the VEU may be controlled by 1-bit (boolean) control vectors, the ability to stream such vectors is provided.

Vector streaming occurs in "blocks" of N items, where N is the implementation-defined number of items per vector register. In the event that the stream count is not a multiple of N the "last block" of items read or written will contain less than N items. On input the block will be padded with suitable values, and any addressing violations resulting from attempting to access these invalid values will be suppressed. Similarly, on output, only the valid items will be written to memory, and no inappropriate addressing violations will be raised. The implication of these rules is that the program does not need to worry about the "boundary conditions".

# 4.1.6 Special instructions and synchronization

Responsibility for execution of the special instructions resides in the Instruction Fetch Unit; in reality, however, one or more of the other execution units may be involved. When more than one execution unit is involved, the IFU must ensure that the

proper synchronization of the other units occurs so that sequential semantics are enforced<sup>1</sup>.

The class of special instructions include instructions to

- provide access to special state, to help save and restore the state of the processor and the individual FIFOs efficiently and to perform context loads, stores and swaps.

- convert between the integer and floating numeric data types. Convert instructions reference one register in the integer execution unit and one in the floating execution unit as appropriate. In addition, there exist transfer instructions, which use "bit copy" semantics to transfer between two registers in different execution units (integer, floating and vector). No data conversion is performed except as necessary to expand/contract their representation<sup>2</sup>.

- determine if a value is within certain bounds. If it is not, a hardware Assert

Fault is generated. Unlike the integer and floating point relationals, the two

boolean values are AND'd together by these instructions and no condition code

is enqueued.

- move, with or without sign extension, a field within a word in the IEU. These

instructions provide for field extraction (with or without sign extension)

and basic shifts.

- find the first (different) bit, i.e. the location of the most significant bit that is different from the sign bit in a value.

- consume one condition code as do conditional jump instructions without dependence on its value.

- read and write the Program Control Word.

The SYNCH instruction causes the processor to synchronize the IFU, IEU, FEU, and VEU. In effect, it will inhibit instruction dispatch until a consistent, "as though the instructions were really executed sequentially" state is reached.

### 4.1.7 Deadlock

Certain sequences of operations may lead to a deadlock situation (each of the IFU, IEU and FEU unable to make progress). Such programs are invalid. The WM computer will detect a deadlock and trap.

The minimum sizes of the various FIFOs are specified that it is always possible to construct a valid WM program. For example, the minimum size of the input FIFOs are 3 so that, at worst, an instruction requiring 3 source operands from memory can be emitted, and consume, its operands without blocking.

<sup>&</sup>lt;sup>1</sup> In general this may imply waiting for all previous instructions to complete and inhibiting all subsequent instructions until the special instruction has completed. In practice, however, many relatively simple optimizations can be detected by an implementation.

<sup>&</sup>lt;sup>2</sup> Aside from the obvious "bit hacking" these instructions allow, they may also be used to get more streams to one of the executions units if the other has them free.

#### 4.2 Data formats

The instruction set shall support <u>i</u>-bit fixed point precision, <u>f</u>-bit floating point single precision, and <u>v</u>-bit vector (fixed and floating) point precision data in twos complement representation. A member of the family is denoted by three parameters, and is denoted  $WM_{\underline{i},\underline{f},\underline{v}}$ . The parameters denote the size, and implicitly the existence, of the integer, floating, and <u>vector</u> data manipulation operations of the family member. The parameters are constrained such that:

<u>i</u> ε {16, 32, 64} <u>f</u> ε {0, 32, 64} <u>y</u> ε {0, 32, 64}

Data format determines what LOAD and STORE instructions are supported on a particular family member: on 32-bit versions of the machine, 8-, 16-, and 32-bit integer data types are supported in memory, and operations are provided to load these data types into the registers. On a 16-bit version of the family, only 8- and 16-bit integer data types are supported, and the operation to load a 32-bit integer is illegal.

# 4.2.1 Data alignment

Data elements are assumed to be aligned. For example, addresses of halfword data elements are assumed to have a zero least significant bit, thus specifying a halfword boundary. This least significant address bit is ignored when accessing such data elements. Instructions are aligned on word boundaries. Doublewords are aligned on sixty-four bit boundaries.

#### 4.2.2 Data sizes

Data elements in memory may be stored in 8-bit byte, 16-bit halfword, 32-bit word, or 64-bit doubleword sizes.

#### 4.2.3 Data Types

The WM architecture supports values of several types: boolean values, signed integer values, and floating point values.

Bits within bytes, halfwords, words, and doublewords are numbered from left to right starting with 0. The lefthand side is the most significant. Bytes within larger entities, such as words, are also numbered from left to right starting with 0. The last byte (number 3) in word 327 is just before the first byte (number 0) in word 328.

#### 4.2.3.1 Boolean values.

No explicit instructions exist to support operations on boolean values. However, the available operations were created with such support in mind. In particular, any bit in an integer register may be set, tested, or selected in one instruction, and any bit may be cleared in two instructions. These macro functions are synthesized by the proper operation combination. Vectors of boolean values may be loaded from and stored to memory as bytes, halfwords, words, or doublewords. i-bit boolean vectors may be logically manipulated with register/register instructions. Shorter boolean fields may also be extracted from larger vectors with a single instruction.

# 4.2.3.2 Signed integer values

Arithmetic on 2's-complement i-bit signed integers with the most significant bit (MSF) as the sign bit is supported by individual operations. While, on appropriate family members, signed integers may be loaded and stored as doublewords, words, halfwords, or bytes, all integer arithmetic is performed on i-bit register quantities. Unsigned integers are not supported by the machine. Explicit underflow checking is required when synthesizing unsigned arithmetic with this architecture.

### 4.2.3.3 Floating point values

Arithmetic is performed using the <u>f</u>-bit value obeying the IEEE floating point standard.

### 4.3 Instruction formats

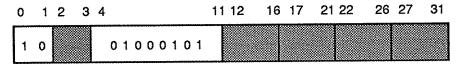

Six instruction formats are supported. Each instruction is 32-bits. The operation code consists of bits 4..11 or 8..11 of the instruction.

#### 4.3.1 Literals in instructions

Certain instructions may specify unsigned, 5-bit literals as operands. These literals are the integers 1-32 and are encoded in the obvious way, except that 32 is encoded as zero.

#### 4.3.2 Instruction format notation

The WM ISA definition has five instruction formats.

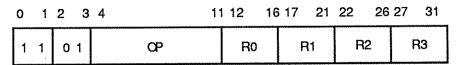

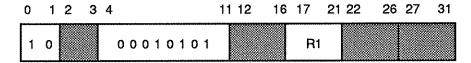

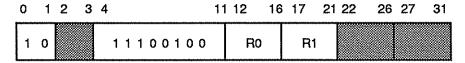

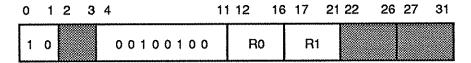

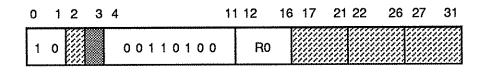

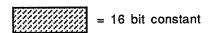

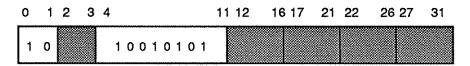

# 4.3.3 Integer format instructions.

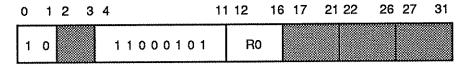

Integer arithmetic and logical instructions are executed by the IEU. The three source specifiers -- R1, RL2 and RL3 -- may name integer registers. RL2 and RL3 may also name 5-bit literals. OP1 is the operation with source inputs R1 and RL2. OP2 is the operations with source inputs consisting of the result of OP1 and RL3. R0 is the destination integer register.

| 0123  | 4 7 | 8 11 | 12 16 | 17 21 | 22 26 | 27 31 |

|-------|-----|------|-------|-------|-------|-------|

| 00 RL | OP1 | OP2  | RO    | R1    | RL2   | RL3   |

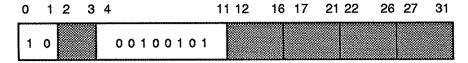

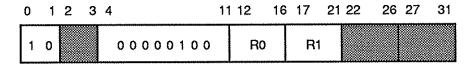

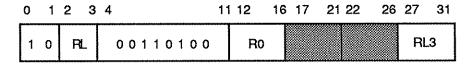

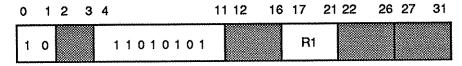

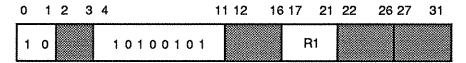

### 4.3.4 LOAD/STORE format instructions.

Load and Store instructions are executed by the IEU. R0, R1, RL2 and RL3 may name integer registers. RL2 and RL3 may name 5-bit literals. OP1 is the operation with source inputs R1 and RL2. OP2 is the operations with source inputs consisting of the result of OP1 and RL3. R0 is the destination register into which a computed address is stored.

| 0 | 1  | 23 | 4 | 7   | 8  | 11 | 12 | 16 | 17 | 21 | 22 | 26 | 27 | 31 |

|---|----|----|---|-----|----|----|----|----|----|----|----|----|----|----|

|   |    |    |   |     | ор | ор |    |    |    |    |    |    |    |    |

|   | )1 | RL | - | SOP | ١, | 2  | RC | )  | R  | 1  | RI | _2 | R  | L3 |

The LOAD and STORE instructions specify two things: (1) the address of the data to be read or written, and (2) the size/type of the data (e.g., byte vs. halfword vs. double-precision floating point). The type specified implicitly determines the execution unit involved.

The address computation is formally and semantically identical to the assignments of the integer/logical instructions:

$$R0 := (R1 \text{ op1} RL2) \text{ op2} RL3$$

The only differences are that the set of operators is smaller and the result of the computation is sent to the memory system in addition to being sent to the destination register. The permitted operations are:

- + addition

- subtraction

- multiplication

asl arithmetical shift left

The type/size of the data to be read or written is specified by the LOAD or STORE instruction.

The memory system ensures that certain sequences of load/store operations are performed properly. Loads and stores from one execution unit are not synchronized with those of the other!

There are no LOAD/STORE instructions for the Vector Execution Unit. All memory-VEU transfers are accomplished with streaming instructions.

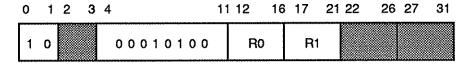

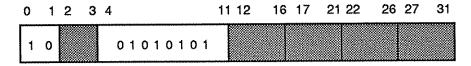

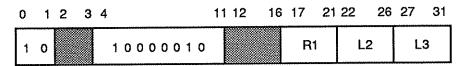

### 4.3.5 Floating point format instructions

Floating point arithmetic instructions are executed by the FEU. R0, R1, R2 and R3 may name floating registers. OP1 is the operation with source inputs R1 and R2. OP2 is the operations with source inputs consisting of the result of OP1 and R3. R0 is the destination register.

| _ | 0 1 | 23 | 4 7 | 8 11 | 12 16 | 17 21 |    | 27 31 |

|---|-----|----|-----|------|-------|-------|----|-------|

|   | 11  | 00 | OP1 | OP2  | RO    | R1    | R2 | R3    |

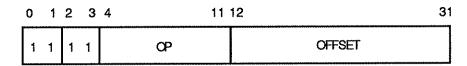

### 4.3.6 Control format instructions

Control instructions are executed by the IFU.

| 0123  | 4 11 | 12 31  |

|-------|------|--------|

| 11 11 | OP   | OFFSET |

The offset is extended tih two least significant zero digits.

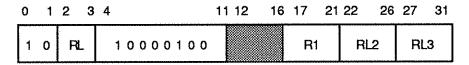

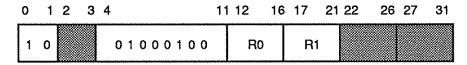

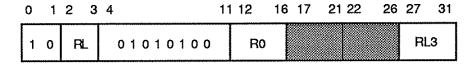

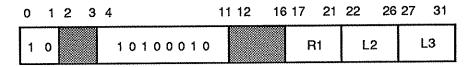

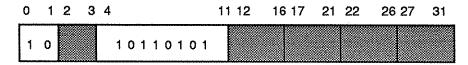

# 4.3.7 Vector format instructions.

Vector instructions are executed by the VEU.

| 0123  | 4 1 | 1 12 16 | 3 17 21 | 22 26 | 27 31 |

|-------|-----|---------|---------|-------|-------|

| 11 01 | OP  | RO      | R1      | R2    | R3    |

R0, R1, R2, and R3 are vector registers. R0 is the destination.

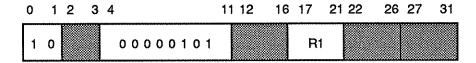

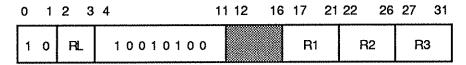

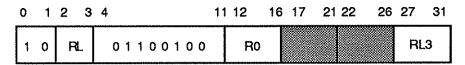

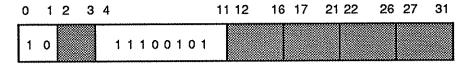

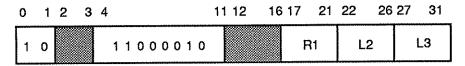

# 4.3.8 Special format instructions

Special instructions are executed by the IFU.

| 0 1 | 2 3 | 4 11 | 12 1 | 6 1 7 | 21 22 | 26 27 | 31 |

|-----|-----|------|------|-------|-------|-------|----|

| 10  | RL  | ОР   | RO   | R1    | RL2   | RI    | L3 |

R0, the destination register, and R1 are general registers. RL2 and RL3 are either literals or general registers.

# 4.4 Registers and support features

### 4.4.1 General registers

There are 32 general register names that may be specified in an instruction -however integer, floating point, and vector registers are distinct, providing 96 total

register names. As an aid in computation, register 31 in all three units are defined to be

identically zero. Although it is possible to write to these registers, whenever read, their

value is zero.

#### 4.4.2 Special registers

Other aspects of the machine state, such as the Program Counter (PC), the Cycle Counter (CC), the Program Control Word (PCW), and the Program Status Word (PSW) cannot be directly accessed by instruction (other than certain bits of the PSW which may be set as a side effect of another instruction -- e.g., condition codes); these registers are only (re)set as a consequence of a context-swap. Details of the special registers are discussed in section 4.6.

#### 4.4.3 Stack

The WM architecture defines

- Stack Limit as register 2, and

- Stack Index as register 3 of the integer execution unit.

The Stack Limit register is guaranteed by software to lie on a page boundary, thus having its lower bits be zero accordingly. (The page size is implementation-dependent, so the number of zeroed lower bits is not specified by the architecture.) The Stack Index contains an integer such that the address of the top of stack is computed as follows:

The Stack Index normally has a negative value. The stack grows towards the positive addresses, and a transition from negative to positive Stack Index is the overflow condition. This condition is checked by hardware whenever the Stack Index is written; an exception is generated if it is met. The Stack Limit may only be written by programs with proper privileges. No push or pops are supported, nor needed, on this machine.

#### 4.4.4 Register convention

The conventions with respect to register usage are:

- r3 SI

- r 0 input integer FIFO; always assumed empty at calls

- r 1 input integer FIFO; contains 1st N parameters on calls, and the result(s) on returns

- f 0 input floating FIFO; always assumed empty at calls

- f1 input floating FIFO; contains 1st N parameters on calls and the result(s) on returns

- v0 input vector FIFO; always assumed empty at calls

- v 1 input vector FIFO; always assumed empty at calls

- r 5 FP (frame-pointer; software convention)

- r 6 HP (exception-handler pointer; software convention)

### 4.5 Memory

### 4.5.1 Memory reads & writes

WM interposes FIFOs ("first in, first out queues") between the register sets and the memory. LOAD and STORE instructions are operations on these FIFOs, and are executed by the IEU when the queues are in normal mode.

LOADs and STOREs specify an address. A LOAD is a request to enqueue data from memory into a specified input FIFO, and a STORE is a request to dequeue data from a specified output FIFO and store it to memory.

Data manipulation instructions (executed by the IEU, FEU, or VEU), which can name registers as operands, use "register 0" to name the input and output FIFOs.

To dequeue data from an input FIFO, an instruction references register 0 as a source operand. To enqueue data in an output FIFO, an instruction specifies register 0 as the destination of a computation. "Register 0" is interpreted differently when used as a source and destination operand; as a source operand it refers to an input FIFO of the execution unit, and as a destination operand it refers to an output FIFO of the execution unit.

LOAD and STORE instructions are executed by the Integer execution unit, but may imply that the data to be loaded or stored is destined for either the Integer or Floating execution Unit FIFOs; memory operations for the Vector Execution Unit are handled by streaming.

Multiple LOAD instructions (with implementation dependent limits) may be executed; the data is enqueued in an input FIFO in the order of the LOAD instructions. Access to register 0 dequeues the next value from the FIFO for use.

LOADs precede access to the read value. STOREs and the production of the data value to be outure may occur in either order. The action of writing to memory is taken only when an appropriate pair of instructions have **both** been executed. Several STORE instructions could have been executed before the first value to be stored is computed into register 0; the addresses are queued until the value to be stored is computed.

The WM architecure defines minimum sizes of the input and output FIFOs; actual sizes are implementation defined. The architecture requires at least:

- 3 i-bit entries in the integer unit's input FIFOs

- 1 j-bit entry in the integer unit's output FIFO

- 3 f-bit entries in the floating unit's input FIFOs,

- 1 f-bit entry in the floating unit's output FIFO,

- 3 N-component blocks of y-bit entries in the vector unit's input FIFO, and

- 1 N-component block of <u>v</u>-bit entries in the vector unit's input FIFO.

These minimums ensure that any single instruction can execute, even if it names all its source operands and it's destination operand as FIFOs.

For any particular implementation, hence specific FIFO sizes, it is possible to construct a program that will deadlock -- for example, by trying to enqueue more than a particular FIFO can hold. Such programs are *invalid*.

### 4.6 Operating system support

#### 4.6.1 Task state

A task is a thread of control. Whenever a task is saved or restored, all of its processor state is transferred to or from its hardware-defined Task Control Block. This is an area in memory with room for:

- (1) State visible to the program

- integer, floating point and vector registers.

- Program Counter, PC.

- Program Control Word, PCW.

- Program Status Word, PSW.

- Cycle Counter, CC.

- Last TCB Pointer, LTP.

- Protection Table Pointer, PTP.

- Map Table Pointer, MTP.

- (2) State visible only indirectly by the program

- input/output FIFO state.

- streaming state.

- other implementation-defined state

In general, the amount and description of the state is implementation-dependent. Only the TCB format for the state visible to the program is defined. Some of the architecturally-defined state is discussed below.

The PCW and PSW are two architecturally-defined CPU device registers. Implementations may add other registers (e.g., to control hardware diagnostics).

The Program Control Word collects a number of fields whose values affect the execution of a task, such as the bit which indicates whether the results of two relational operators in an instruction are AND'd or OR'd as well as the bits that enable/disable certain traps. The PCW consists of:

| Bit# | Meaning                            |

|------|------------------------------------|

|      | AND/OD voletionals (AND 4)         |

| 0    | AND/OR relationals (AND == 1)      |

|      | Exceptions Enabled (enabled == 1): |

| 1    | Attempted Stack Limit Modification |

| 2    | Stack Index Negative               |

| 3    | Assert Fault                       |

| 4    | Integer Divide By Zero             |

| 5    | Floating Divide By Zero            |

| 6    | Integer Arithmetic Overflow        |

| 7    | Integer Arithmetic Underflow       |

| 8    | Floating Arithmetic Overflow       |

| 9    | Floating Arithmetic Underflow      |

| 10   | Cycle Counter Overflow             |

| 11   | Raise Address                      |

| 12   | Raise Call                         |

| 13   | Raise Jump                         |

The Program Status Word collects a number of fields that reflect status of the task, such as the run/halt bit, the interrupt enabling bit, the priority and the condition FIFOs. For example, the PSW could include:

Bit # Meaning

O Run/Halt (run == 1)

Interrupts Enabled

2:5 Priority[0:3]

6:8 Integer Condition FIFO Bits

9:10 integer Condition FIFO Depth

11:13 Floating Condition FIFO Bits

14:15 Floating Condition FIFO Depth

The Cycle Counter is a 32-bit register that is incremented by one every cycle that the task executes. It may overflow (once every ~200 seconds with a 50ns cycle time), in which case an exception may be raised.

The Last TCB Pointer, LTP, in general points to a TCB. When an interrupt occurs, a forced context swap is performed and the LTP of the *new* task is set to point to the TCB of the task that was running at the time of the interrupt. Thus, in the case of nested interrupts, the LTPs form a chained "stack" of the suspended handlers; the SwapLT instruction will resume the previous task.

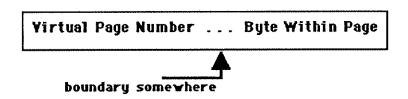

A task's virtual address space is divided into pages. An address is divided into two parts, the virtual page number, and the byte within page address. The boundary between these parts is implementation-dependent, as is the structure of the tables (one-level, two-level, etc.). Pages must, however, be at least 512 bytes.

Assume K bits of virtual page number and j-K bits that specify the byte within the page. Associated with every virtual page number is a protection table and map table entry, as described below.

#### 4.6.2 Protection

Each task has a Protection Table that defines its memory access rights on a page-by-page basis. The Protection Table Pointer (PTP) in the TCB is either null (zero), or the physical address of the base of this table and virtual address page numbers are used to index into it. If the PTP is null no type or rights checking is performed, otherwise protection is checked as specified below<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>The PTP may be null because protection is not implemented on a certain model of WM. In addition, however, PTP is null when the processor is first "booted" -- this corresponds to the "most privileged state".

A Protection Entry is a byte, with the following format:

| type | rights |

|------|--------|

|      |        |

The first four bits define the page type. This field is interpreted as:

| 0000      | Memory   |     |          |

|-----------|----------|-----|----------|

| 0001      | TCB      |     |          |

| 0010      | Entry    |     |          |

| 0011      | Device   |     |          |

| 0100-0111 | reserved | for | hardware |

| 1000-1111 | reserved | for | software |

Only the first four are hardware defined. Accesses to pages with reserved protection types raise a memory protection exception.

An access to "Memory" pages may either be reads, writes, or executes. The rights bits are R, W, and X, and determine if such operations are allowed, or if they result in memory protection exceptions.

Accesses to a TCB page may be reads, writes, or context save/restore/swap; the protection bits are correspondingly, R, W, and S. Note that saving context is not a privileged operation.

Accesses to an Entry page may be reads, writes, or ECalls; the protection bits are correspondingly, R, W, and C.

Accesses to Device pages may be only reads and writes, and the corresponding rights bits are R and W.

# 4.6.3 Address mapping

Each task has a Map Table that defines its virtual-to-physical address translation. The Map Table Pointer (MTP) in the TCB is either null (zero), or the physical address of the base of this table and virtual address page numbers are used to index into it. If the MTP is null, no translation is performed; otherwise translation proceeds as specified below<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>The MTP may be null because virtual memory is not implemented on a certain model of WM. In addition, however, MTP is null when the processor is first "booted" -- this corresponds to the "unmapped processor state".

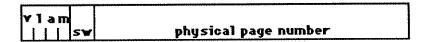

Map table entries have the following format:

and their bits are interpreted as follows:

- 0 Valid this page exists in physical memory

- 1 Locked --this page is locked into memory<sup>1</sup>

- 2 Accessed this page has been read

- 3 Modified this page has been written

- 4:5 Software usable/defined

- 6:31 Physical Page Number 26 bits

The 26-bit physical page number is catenated with the Byte Within Page field to form the physical address. This limits the physical memory (without bank-switching) to an address space of 26 plus size(Byte Within Page) bits.

### 4.6.4 Initialization of the machine

Machine implementation determines initialization.

#### 4.7 Devices

Each device connected to WM must conform to the following conventions:

- 1. The device must "know" the physical TCB address to which it is to interrupt. This may be wired-in for certain devices, or may be a settable register.

- 2. DMA devices must use "the zero-th register", the zero-th location relative to the device page, as the memory address register; non-DMA devices are advised not to use this location at all. The memory translation hardware recognizes stores into the zero-th location of device pages, and assumes the value to be stored is a virtual address; it then

- verifies that the specified page is both valid and locked, and

- stores the translated (physical) address rather than the virtual one.

- 3. DMA transfers may not cross a page boundary, thus the maximum size block that can be transferred is a page.

<sup>&</sup>lt;sup>1</sup> The "locked bit" is a software convention; it is, however, checked by hardware when DMA IO transfers are specified. See Section 4.5.

# 4.8 Input/output

Control of input/output devices is "memory mapped". A portion of the physical address space reserved for "device registers". Unpriviledged applications program are permitted to directly access IO devices.

At least three devices are required of all implementations:

- "the CPU", control and status registers for the processor itself. One processor can probe or start/stop another or itself with bit set/reset operations on the appropriate device register.

- one or more "timers", which are 32-bit counters that decrement each 100ns and, if enabled, interrupt when they become negative (but continue counting until reset), and,

- a "calendar" which is a 64-bit counter that is incremented each 100ns, runs continuously when power is enabled, and will interrupt when it overflows.

# 4.9 Traps (exceptions) and interrupts

Non-programmed control flow changes can occur through two types of events:

interrupts these are asynchronous with respect to instruction execution and may not be associated with the currently executing task.

traps these are hardware-defined and are the direct result of an instruction just executed.

Interrupts are implemented as context-swaps to a handler task; traps are implemented as ECall's to handler entries. The terms "trap" and "exception" are used interchangeably.

### 4.9.1 Interrupts

Interrupts are best viewed as communication (messages) from asynchronous cooperating processes that happen to be implemented in hardware -- and as such, the task mechanism is the proper one for handling them. Thus, the effect of an interrupt is almost identical to a SwapCTX instruction; the only difference is that, on interrupts, the LTP (last TCB pointer) of the new task is set to point to the TCB of the task that was running at the time of the interrupt.

Note that each device capable of interrupting the processor must retain one or more addresses of the TCBs for the handlers of the interrupts it generates, and present this address to the processor along with the priority of the interrupt.

An interrupt (context swap) will be performed to the handler task if the priority of the interrupt is higher than that of the processor, and indeed, is the highest of all outstanding interrupts.

# 4.9.2 Traps

The page zero of a program's virtual memory (starting at address 0) must contain an Entry Page. A trap is implemented as an ECall on a hardware-understood location within this page. The hardware-defined locations are:

| Location | Exception                                    |

|----------|----------------------------------------------|

| 0        | (reserved)                                   |

| 8        | Load While Input Streaming                   |

| 16       | Store While Output Streaming                 |

| 24       | Input FIFO Full                              |

| 32       | Input FIFO Empty                             |

| 40       | Output FIFO Full (Data Capacity Exceeded)    |

| 48       | Output FIFO Full (Address Capacity Exceeded) |

| 56       | Condition FIFO Full                          |

| 64       | Condition FIFO Empty                         |

| 72       | (reserved)                                   |

| 80       | Undefined Instruction                        |

| 88       | Memory Protection Violation                  |

| 96       | Attempted Stack Limit Modification           |

| 104      | Stack Index Negative                         |

| 112      | Jump On Stream Count while not streaming     |

| 120      | Double Stream                                |

| 128      | (reserved)                                   |

| 136      | Assert Fault                                 |

| 144      | Integer Divide By Zero                       |

| 152      | Floating Divide By Zero                      |

| 160      | Integer Arithmetic Overflow                  |

| 168      | Integer Arithmetic Underflow                 |

| 176      | Floating Arithmetic Overflow                 |

| 184      | Floating Arithmetic Underflow                |

| 192      | (reserved)                                   |

| 200      | Cycle Counter Overflow                       |

| 208      | Raise Address                                |

| 216      | Raise Call                                   |

| 224      | Raise Jump                                   |

| 232      | (reserved)                                   |

| 240      | Page Fault                                   |

| 248      | (reserved)                                   |

The exceptions are ordered. If an instruction produces more than one exception, the one that vectors to the lowest memory location is selected. The other exceptions related to that instruction are nullified. An exception handling routine may itself cause an exception.

The EReturn instruction is used to return from an exception, just as from an ECall.

#### 4.9.3 Exceptions

Exceptions are listed by function unit:

# 4.9.3.1 Integer exceptions

The following arithmetic conditions result in exceptions unless masked off in the PSW:

- Input FIFO 0/1 Empty: an attempt to read r0 or r1 was made when no value is present in the FIFO, nor is any value scheduled to be loaded.

- Output FIFO 0/1 Full (Data Capacity Exceeded): an attempt to write r0 or r1

was made when the associated output FIFO was already full, and no value is

scheduled to be stored.

- Overflow/Underflow: an arithmetic operation overflowed or underflowed

- Divide by 0: an attempt to divide by zero was made

# 4.9.3.2 Load/Store exceptions

The following exceptions may occur as a result of a load or store instruction:

- Input FIFO 0/1 Empty: as per integer instructions when used as a source operand in the address calculation.

- Input FIFO 0 Full: an attempt was made to perform a load when the input FIFO was already full, or will be full after some pending loads complete.

- Output FIFO 0 Full (Address Capacity Exceeded): an attempt has been made to perform a store when the output FIFO is empty and no further address can be buffered.

- Output FIFO 0/1 Full (Data Capacity Exceeded): as per integer instructions when specified as the destination register for the address calculation.

- Overflow/Underflow: an arithmetic operation overflowed or underflowed.

- Memory Protection Violation: an attempt to read, write, or execute from/to a memory location without proper access privilege (see Chapter 4 for a more complete discussion).

- Load While Input Streaming: a load instruction while register 0 is in input streaming mode.

- Store While Output Streaming: a store instruction while register 0 is in output streaming mode.

#### 4.9.3.3 Control exceptions

The following exceptions may be raised as the result of a control flow instruction:

- Condition FIFO Empty: A JumpIT(JumpFT) or JumpIF(JumpFF) instruction is being executed, and the condition bit has not been set (and is not in the process of being set) by a previous relational operator.

- Memory Protection Violation: An attempt was made to transfer control to a page without proper access privileges (see Chapter 4 for a more complete discussion).

- Page Fault: In a virtual memory system, an attempt to execute from a virtual address that does not exist in physical memory.

# 4.9.3.4 Floating point exceptions

The following arithmetic conditions result in exceptions unless masked off in the PCW:

- Overflow/Underflow: as per integer instructions.

- Divide by 0: as per integer instructions.

- Condition FIFO overflow: As per the integer instructions.

Note that input/output FIFO empty/full are not exception conditions for the floating point instructions as they were for the integer and load/store instructions. This allows the integer and floating point units to proceed asynchronously preparing/consuming addresses and data -- but does require a more global detection of erroneous (deadlocked) programs.

## 5. Detailed Requirements

#### 5.1 Instruction set notation

#### 5.1.1 Registers

### 5.1.1.1 General registers