# The Design and Evaluation of an Off-Host Communications Protocol Architecture

A Thesis

Presented to

the Faculty of the School of Engineering and Applied Science

University of Virginia

In Partial Fulfillment

of the Requirements for the Degree

Master of Science (Computer Science)

by

Jeffrey R. Michel

August 1993

# **APPROVAL SHEET**

This thesis is submitted in partial fulfillment of the requirements for the degree of Master of Science (Computer Science)

Author

This thesis has been read and approved by the Examining Committee:

Thesis Advisor

Committee Chairman

Accepted for the School of Engineering and Applied Science:

Dean, School of Engineering and Applied Science

August 1993

# Abstract

The University of Virginia Computer Networks Laboratory has developed an implementation of the SAFENET lightweight suite of communication protocols using an off-host implementation of the Xpress Transfer Protocol (XTP). We used an attached protocol processor to test the hypothesis that such an architecture could simultaneously optimize protocol performance (by giving it a dedicated coprocessor) and user application performance (by freeing the host from the burden of protocol processing). Our experience indicates that the choice of implementation architecture has a profound impact upon the overall system performance. This work surveys the design issues inherent to off-host communications architectures and discusses the design choices made in our own architecture. Also presented are our performance results and the many lessons learned from the analysis of our implementation architecture. We also provide a survey of related work performed by other researchers. To assist the designers of future off-host architectures and to evaluate the degree to which we exploited our particular architecture, we develop a simple analytic model to predict the performance of an off-host architecture using readily-obtainable input parameters. The predictions of the model as applied to our system are compared with the system's observed performance.

# Acknowledgments

Many deserve appreciation for helping to bring this work to fruition. First of all I would like to thank our sponsor, SPAWAR, for funding this research. Further, I wish to acknowledge my colleagues Robert Simoncic, Bert Dempsey, John Fenton, and Alex Waterman for their invaluable assistance on our project. In particular, I wish to thank Alex for generously providing preliminary results from his on-host XTP implementation. I am also indebted to Craig Meyers for his extensive cooperation and Bob Ross for his hardware expertise. Thanks are especially due to my advisor, Alfred Weaver, whose wisdom and guidance have allowed me to make achievements here at the University of which I can be proud. Above all, I wish to thank my parents for their endless support, which has made all of this possible.

# **Table of Contents**

| Chapter 1 | Introduction                                                   | 1  |

|-----------|----------------------------------------------------------------|----|

| - 1.1.    | Background                                                     | 1  |

| 1.2.      | A General Model of Communication                               | 2  |

| 1.3.      | Protocol Implementation Possibilities                          | 5  |

|           | 1.3.1. On-Host Implementation                                  | 6  |

|           | 1.3.2. Off-Host Implementation                                 | 8  |

| 1.4.      | Possible Advantages of an Off-Host Protocol Implementation     | 9  |

|           | 1.4.1. Host Benefits                                           |    |

|           | 1.4.2. Protocol Benefits                                       | 10 |

| 1.5.      | Possible Pitfalls of Using an Off-Host Protocol Implementation | 12 |

|           | 1.5.1. Incurring Operating System Overhead                     |    |

|           | 1.5.2. Overtaxing the Host Processor                           |    |

|           | 1.5.3. Increased Data Path Complexity                          |    |

| 1.6.      | Summary                                                        | 14 |

|           |                                                                |    |

| Chapter 2 | <b>Design Issues in Off-Host Communications</b>                |    |

|           | Architecture                                                   | 16 |

| 2.1.      | Overview                                                       | 16 |

| 2.2.      | The Host-Processor Interface to the Protocol Processor         | 16 |

|           | 2.2.1. Command Stream                                          | 17 |

|           | 2.2.2. Status Stream                                           | 17 |

|           | 2.2.3. Data Stream                                             | 18 |

|           | 2.2.4. Options Stream                                          |    |

| 2.3.      | Hardware and Software Architectural Levels                     | 19 |

|           | 2.3.1. User Level                                              | 20 |

|           | 2.3.2. Kernel Level                                            | 21 |

|           | 2.3.3. Bus Level                                               | 22 |

|           | 2.3.4. Protocol-Processor Level                                | 23 |

|           | 2.3.5. Network-Interface Level                                 | 23 |

| 2.4.      | Communication Mechanisms Between Levels                        | 24 |

|           | 2.4.1. Communication Between the User and Kernel Levels        | 24 |

|           | 2.4.2. Communication Between Hardware Components               | 28 |

| 2.5.      | Architectural Integration Continuum                            |    |

|           | 2.5.1. Continuum Choices                                       | 36 |

|           | 2.5.2. Trade-Offs                                              | 36 |

|           | Deleted Work                                                   | 30 |

| Chapter 3 | Related Work                                                   |    |

| 3.1.      | Overview                                                       |    |

| 3.2.      | Chesson                                                        |    |

| 3.3.      | Kanakia and Cheriton                                           |    |

| 3.4.      | Cooper et al.                                                  |    |

| 3.5.      | Netravali et al.                                               | 45 |

| 3.6.      | Beach                                          | 47 |

|-----------|------------------------------------------------|----|

| 3.7.      | MacLean and Barvick                            | 49 |

| 3.8.      | Mitchell et al.                                | 50 |

| 3.9.      | Siegel et al                                   | 51 |

| 3.10.     | Summary                                        | 52 |

| Chapter 4 | An Off-Host Communications Architecture for    |    |

|           | SAFENET                                        | 54 |

| 4.1.      | Overview                                       | 54 |

| 4.2.      | SAFENET                                        | 54 |

| 4.3.      | Host Computer System                           |    |

| 4.4.      | Architectural Constraints                      | 57 |

| 4.5.      | Design Choices                                 |    |

|           | 4.5.1. Hardware Components                     |    |

|           | 4.5.2. Software Layers                         |    |

|           | 4.5.3. Inter-Layer Communications Mechanisms   |    |

|           | 4.5.4. A Data Flow Example                     | 67 |

| Chapter 5 | Performance Analysis                           | 70 |

| 5.1.      | Overview                                       |    |

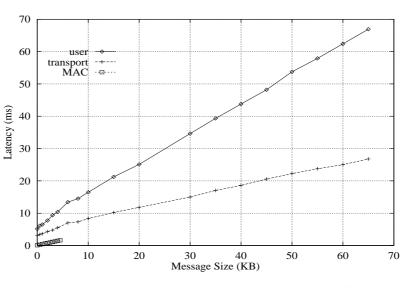

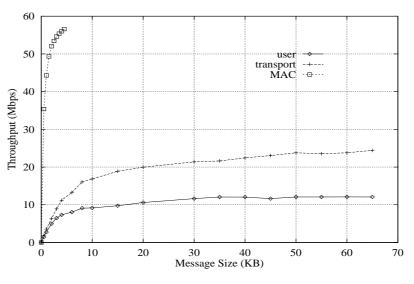

| 5.2.      | Performance Observed at Various Service Levels |    |

| 5.2.      | 5.2.1. MAC Level                               |    |

|           | 5.2.2. Transport Level                         |    |

|           | 5.2.3. User Level                              |    |

| 5.3.      | Performance Profile                            |    |

| 5.4.      | Host Load                                      |    |

| 5.5.      | Performance Bottlenecks                        |    |

|           | 5.5.1. ASDU Length-Independent Overhead        |    |

|           | 5.5.2. ASDU Length-Dependent Overhead          |    |

| Chapter 6 | A Simple Model to Predict Performance          | 84 |

| 6.1.      | Motivation                                     | 84 |

| 6.2.      | Background                                     |    |

| 6.3.      | Goals of the Model                             |    |

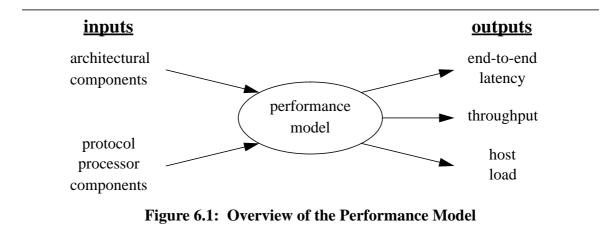

| 6.4.      | Model Overview                                 |    |

|           | 6.4.1. Input Components                        |    |

|           | 6.4.2. Determination of Outputs                |    |

|           | 6.4.3. Communication Operations Considered     |    |

| 6.5.      | Assumed Class of Architectural Design          |    |

| 6.6.      | Input Parameters for our Architectural Class   |    |

| 6.7.      | Performance Derivations                        |    |

|           | 6.7.1. Period Derivation                       |    |

|           | 6.7.2. Throughput Derivation                   |    |

|           | 6.7.3. Host Load Derivation                    |    |

|           | 6.7.4. Delay Derivation                        | 96 |

| 6.8.         | Model Predictions for our Architecture                              | 97  |

|--------------|---------------------------------------------------------------------|-----|

|              | 6.8.1. Input Parameter Values                                       | 97  |

|              | 6.8.2. Throughput and Latency Predictions                           | 98  |

|              | 6.8.3. Host Load Predictions                                        | 99  |

| 6.9.         | Comparison with Empirical Results                                   | 100 |

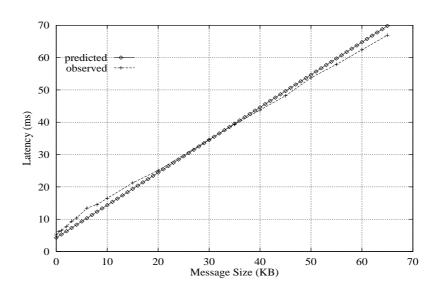

|              | 6.9.1. Validation of Throughput and Latency Predictions             | 100 |

|              | 6.9.2. Validation of Host Load Predictions                          | 100 |

| 6.10.        | Possible Extensions to the Model                                    | 100 |

|              | 6.10.1. Support for Other Architectural Classes                     | 101 |

|              | 6.10.2. Implementation-Dependent Components                         |     |

|              | 6.10.3. Consideration of More Communication Operations              |     |

|              | 6.10.4. Use of Queueing Theory                                      | 102 |

| Chapter 7    | Conclusions                                                         | 104 |

| 7.1.         | Summary                                                             | 104 |

| 7.2.         | Evaluated Advantages of our Off-Host Architecture                   |     |

|              | 7.2.1. Host Benefits                                                | 106 |

|              | 7.2.2. Protocol Benefits                                            | 108 |

| 7.3.         | Evaluated Pitfalls of our Off-Host Architecture                     | 109 |

|              | 7.3.1. Incurring Operating System Overhead                          | 109 |

|              | 7.3.2. Overtaxing the Host CPU with Protocol Processor              |     |

|              | Driving                                                             | 110 |

|              | 7.3.3. Increased Data Path Complexity                               |     |

| 7.4.         | Critique of the Simple Performance Model                            | 112 |

| 7.5.         | Suggestions for Future Work                                         |     |

| 7.6.         | The Suitability of Off-Host Communications Architectures            | 117 |

| References   | \$                                                                  | 119 |

|              |                                                                     |     |

| Appendix A   | A: Time-Average Measurement of Architectural                        | 104 |

| A 1          | Input Parameters                                                    |     |

| A.1.<br>A.2. | Rationale for Time-Average Measurement                              |     |

| A.2.<br>A.3. | Test Harness                                                        |     |

| A.3.         | Measurement of Specific Parameters                                  |     |

|              | A.3.1. System Call Overhead<br>A.3.2. User-Level Interrupt Overhead |     |

|              | A.3.3. Bus Transfer Overhead                                        |     |

| A.4.         | Elimination of "Noise"                                              |     |

|              |                                                                     |     |

| Appendix 1   | B: Extrapolation of Protocol Processor Input<br>Parameters          | 120 |

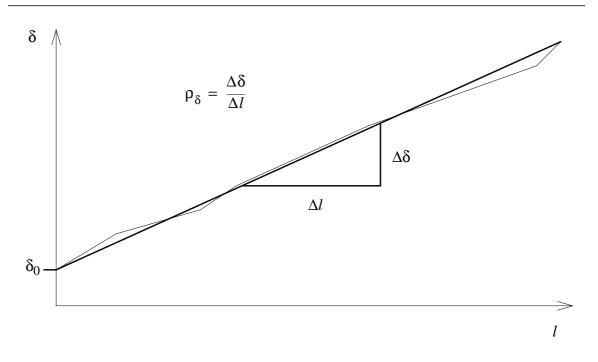

| B.1.         | Rationale for Protocol Processor Performance Plots                  |     |

| В.1.<br>В.2. | Protocol Processor Input Parameter Calculation                      |     |

| D.2.         |                                                                     | 129 |

v

# **List of Figures**

| Chapter 1 Int                                                                                            | roduction                                                                                                                                                                                                                                                                                      | 1                                  |

|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Figure 1.1:                                                                                              | The ISO/OSI Reference Model                                                                                                                                                                                                                                                                    | 3                                  |

|                                                                                                          |                                                                                                                                                                                                                                                                                                |                                    |

| _                                                                                                        | sign Issues in Off-Host Communications                                                                                                                                                                                                                                                         |                                    |

|                                                                                                          | chitecture                                                                                                                                                                                                                                                                                     |                                    |

| Figure 2.1:                                                                                              | Architectural Levels                                                                                                                                                                                                                                                                           | 20                                 |

| Chapter 4 An                                                                                             | <b>Off-Host Communications Architecture for</b>                                                                                                                                                                                                                                                |                                    |

| SA                                                                                                       | FENET                                                                                                                                                                                                                                                                                          | 54                                 |

| Figure 4.1:                                                                                              | SAFENET Protocol Architecture                                                                                                                                                                                                                                                                  | 55                                 |

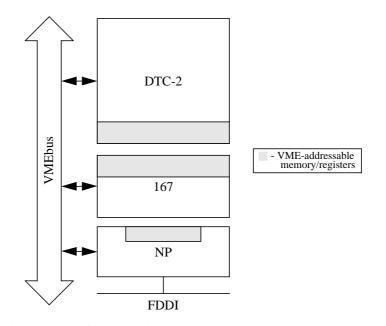

| Figure 4.2:                                                                                              | Communications Hardware Architecture                                                                                                                                                                                                                                                           | 60                                 |

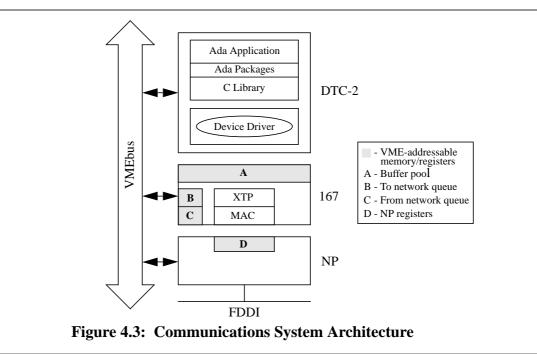

| Figure 4.3:                                                                                              | Communications System Architecture                                                                                                                                                                                                                                                             | 61                                 |

| Chapter 5 Per                                                                                            | formance Analysis                                                                                                                                                                                                                                                                              | 70                                 |

| -                                                                                                        | End-to-End Latency vs. Message Size                                                                                                                                                                                                                                                            |                                    |

| -                                                                                                        | Throughput vs. Message Size                                                                                                                                                                                                                                                                    |                                    |

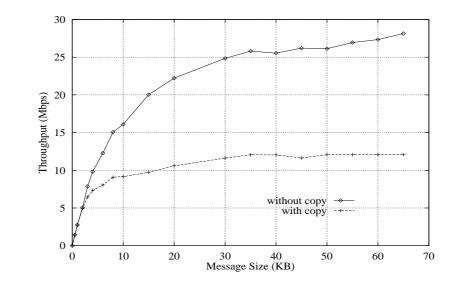

| Figure 5.3:                                                                                              | Data Copy Effects upon Throughput vs. ASDU Size                                                                                                                                                                                                                                                |                                    |

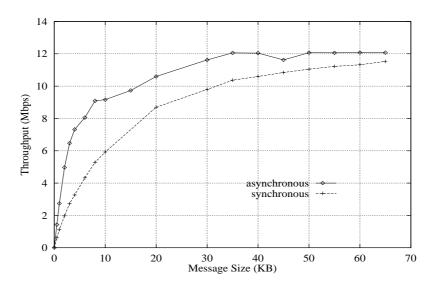

| Figure 5.4:                                                                                              | API Mode Effects upon Throughput vs. ASDU Size                                                                                                                                                                                                                                                 |                                    |

| Chapter 6 A S                                                                                            | imple Model to Predict Performance                                                                                                                                                                                                                                                             | 84                                 |

| Figure 6.1:                                                                                              | Overview of the Performance Model                                                                                                                                                                                                                                                              |                                    |

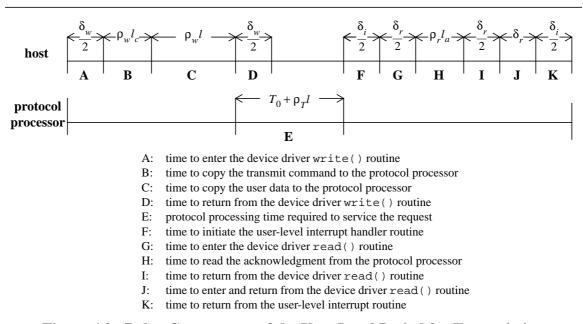

| Figure 6.2:                                                                                              | Delay Components of the User-Level Period for                                                                                                                                                                                                                                                  |                                    |

| -                                                                                                        | Transmission                                                                                                                                                                                                                                                                                   | 93                                 |

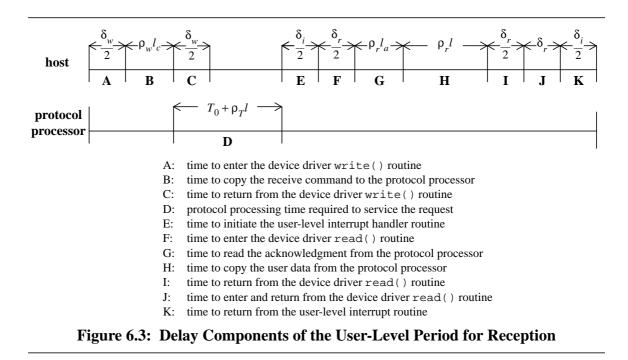

| Figure 6.3:                                                                                              | Delay Components of the User-Level Period for                                                                                                                                                                                                                                                  |                                    |

|                                                                                                          |                                                                                                                                                                                                                                                                                                |                                    |

|                                                                                                          | Reception                                                                                                                                                                                                                                                                                      | 94                                 |

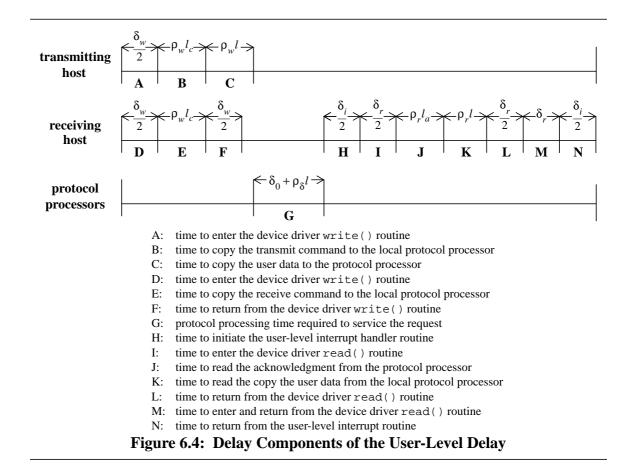

| Figure 6.4:                                                                                              | Reception<br>Delay Components of the User-Level Delay                                                                                                                                                                                                                                          |                                    |

| Figure 6.5:                                                                                              | Delay Components of the User-Level Delay<br>End-to-End Latency vs. ASDU Size                                                                                                                                                                                                                   | 97<br>98                           |

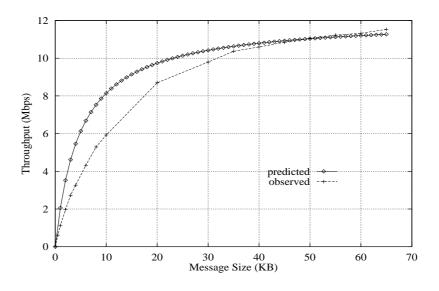

| Figure 6.5:<br>Figure 6.6:                                                                               | Delay Components of the User-Level Delay<br>End-to-End Latency vs. ASDU Size<br>Synchronous Throughput vs. ASDU Size                                                                                                                                                                           | 97<br>98<br>99                     |

| Figure 6.5:                                                                                              | Delay Components of the User-Level Delay<br>End-to-End Latency vs. ASDU Size                                                                                                                                                                                                                   | 97<br>98<br>99                     |

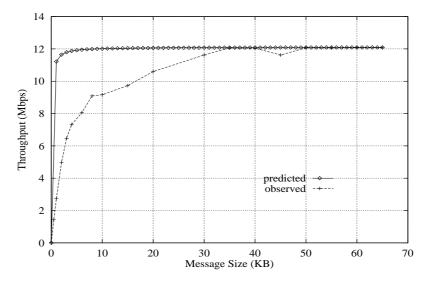

| Figure 6.5:<br>Figure 6.6:<br>Figure 6.7:                                                                | Delay Components of the User-Level Delay<br>End-to-End Latency vs. ASDU Size<br>Synchronous Throughput vs. ASDU Size<br>Asynchronous Throughput vs. ASDU Size                                                                                                                                  | 97<br>98<br>99                     |

| Figure 6.5:<br>Figure 6.6:<br>Figure 6.7:<br>Appendix A: Ti                                              | Delay Components of the User-Level Delay<br>End-to-End Latency vs. ASDU Size<br>Synchronous Throughput vs. ASDU Size<br>Asynchronous Throughput vs. ASDU Size                                                                                                                                  | 97<br>98<br>99<br>99               |

| Figure 6.5:<br>Figure 6.6:<br>Figure 6.7:<br>Appendix A: Ti<br>In                                        | Delay Components of the User-Level Delay<br>End-to-End Latency vs. ASDU Size<br>Synchronous Throughput vs. ASDU Size<br>Asynchronous Throughput vs. ASDU Size                                                                                                                                  | 97<br>98<br>99<br>99<br>99         |

| Figure 6.5:<br>Figure 6.6:<br>Figure 6.7:<br>Appendix A: Ti<br>In<br>Figure A.1:                         | Delay Components of the User-Level Delay<br>End-to-End Latency vs. ASDU Size<br>Synchronous Throughput vs. ASDU Size<br>Asynchronous Throughput vs. ASDU Size<br>ime-Average Measurement of Architectural<br>put Parameters<br>Test Harness                                                    | 97<br>98<br>99<br>99<br>99         |

| Figure 6.5:<br>Figure 6.6:<br>Figure 6.7:<br>Appendix A: Ti<br>In<br>Figure A.1:<br>Appendix B: E:       | Delay Components of the User-Level Delay<br>End-to-End Latency vs. ASDU Size<br>Synchronous Throughput vs. ASDU Size<br>Asynchronous Throughput vs. ASDU Size<br>ime-Average Measurement of Architectural<br>put Parameters<br>Test Harness<br><b>xtrapolation of Protocol Processor Input</b> | 97<br>98<br>99<br>99<br>124<br>125 |

| Figure 6.5:<br>Figure 6.6:<br>Figure 6.7:<br>Appendix A: Ti<br>In<br>Figure A.1:<br>Appendix B: E:<br>Pa | Delay Components of the User-Level Delay<br>End-to-End Latency vs. ASDU Size<br>Synchronous Throughput vs. ASDU Size<br>Asynchronous Throughput vs. ASDU Size<br>ime-Average Measurement of Architectural<br>put Parameters<br>Test Harness<br>xtrapolation of Protocol Processor Input        | 97<br>98<br>99<br>99<br>99         |

# **List of Tables**

| Chapter 5 Performance Analysis                                   | 70         |

|------------------------------------------------------------------|------------|

| Table 5.1: Profile of a One-Byte SEND_MESSAGE                    | 74         |

| Table 5.2: Profile of a One-Byte GET_MESSAGE                     | 74         |

| Table 5.3: Profile of a 64-KB SEND_MESSAGE                       |            |

| Table 5.4: Profile of a 64-KB GET_MESSAGE                        | 76         |

| Chapter 6 A Simple Model to Predict Performance                  | <b>Q</b> / |

| Chapter 6 A Simple Model to Predict Performance                  |            |

| Table 6.1: Architectural Input Parameters                        | 91         |

| Table 6.2: Protocol Processor Input Parameters                   | 92         |

| Table 6.3: Input Parameter Values for our SAFENET Implementation | 98         |

# **1** Introduction

# 1.1. Background

Although modern local area networks (e.g., FDDI, desktop ATM, and HiPPI) promise both high performance (100 Mbps or more of throughput) and new functionality (synchronous bandwidth), traditional computer system and application designs—those that have functioned well for older networks (e.g., Ethernet) operating asynchronously and at lower data rates—have had difficulty delivering on such promises. Since the modern technology brings significantly-increased bandwidth into which computer systems may tap, one might naively assume that similar improvements occur in throughput from the perspective of application processes. Recent measurements, however, show that this is not the case. For example, although FDDI provides a transmission rate ten times higher than that of Ethernet, the throughput available to an application process using FDDI is typically only double or triple that available from Ethernet.

The reason for such problems becomes apparent when one recognizes that between the high-speed network medium and an application process stands an architectural gauntlet of computer system hardware, communication protocols, and operating system software. As system designers have attempted to supply more of the growing network-media bandwidth to application programs, they find that these architectural fixtures are becoming more and more of a bottleneck. In particular, it has been observed that the execution of communications protocols has played a major role in constraining user application throughput. The research in this thesis is concerned with attacking the problem of protocol execution.

The recent criticism of protocols has prompted a rethinking of their implementation architectures. Although many variations exist, there are only two *basic* choices for where to execute protocols; either application processes and protocols must share the host processor and contend for its cycles, or the protocols must run off-host on dedicated coprocessor hardware and pay the penalty for the communication between their processor and the host computer system. The former represents the classical approach (e.g., TCP/IP embedded in a UNIX kernel) and has been well studied; the latter is novel and has not been the subject of as much academic investigation. At least in theory, the off-host approach seems to be a route for improved performance. By off-loading the host of its communications processing responsibilities, application processes will have more host processing cycles available, and by giving communications protocols their own processor, their implementations may be tuned to provide better performance to applications. In addition, the dedicated cycles which the protocol processor provides to protocol processing may be essential for maintaining the real-time communications processing deadlines inherent in continuous-media applications that make use of synchronous bandwidth. It is reasonable to expect, however, some additional sources of overhead with the off-host approach due to the complexity of its architecture. The identification of this overhead and its minimization through proper design choices are principal subjects of this thesis.

The goals of this thesis are: (a) to identify the general design issues inherent in offhost communications protocol architectures, (b) to study an actual off-host protocol architecture, presenting its design, implementation, and performance, (c) to identify the performance bottlenecks in the architecture, relating them to architectural considerations in its design, (d) to develop an analytic model of the performance of off-host communications architectures and to validate it through comparison with observed performance, and (e) to make qualitative judgements about the suitability of off-host communications architectures.

# **1.2.** A General Model of Communication

Before delving into the issues of off-host protocol implementations, we first present an overview of our general model of computer communication, including the topics of computer networking and communication protocols. This prepares us for the discussion of communication architectures employing off-host protocol implementations. A *computer*  *network* consists of a set of geographically-distributed, autonomous computers, termed *hosts*, that are connected via communications links. Physical links between the individual hosts provide the basic ability to communicate through the modulation of fundamental physical signals such as electrical potential differences and electromagnetic radiation. In addition to this physical media, certain conventions are needed to provide a discipline for the use of the media and to give meaning to the signals it carries. These conventions are expressed in the form of *protocols*, sets of rules governing issues such as the physical links themselves, the interaction between network hosts, and the syntax and semantics of the information they transmit and receive.

These communications protocols are quite numerous and have perform varying services. To organize this complexity, they are structured into *protocol hierarchies* consisting of multiple layers of functionality. For the purposes of our discussion, we shall use the hierarchical organization of the ISO/OSI reference model [24] to refer to the protocol layers and to imply the functionality supported at each. This seven layer model, illustrated in Figure 1.1, is structured such that a protocol at layer *n* in the hierarchy employs the services of the protocols at layer (n - 1) to provide communications services to the protocols at layer (n + 1). Below the first layer are the physical communications media, and above the seventh layer are application processes.

| Application Process |              |         |  |

|---------------------|--------------|---------|--|

|                     | Application  | layer 7 |  |

|                     | Presentation | layer 6 |  |

|                     | Session      | layer 5 |  |

|                     | Transport    | layer 4 |  |

|                     | Network      | layer 3 |  |

|                     | Data Link    | layer 2 |  |

|                     | Physical     | layer 1 |  |

|                     |              | _       |  |

Physical Medium

Figure 1.1: The ISO/OSI Reference Model

A brief summary of the functionality of the protocols present at each layer in the OSI reference model is as follows.

- An *application layer* protocol is responsible for dictating the format of distributed data structures and defining the sequence of data unit exchanges for a given type of application. The protocol directly serves the application programs above it.

- A *presentation layer* protocol provides a standardized syntax for application layer data which preserves the semantics of the information, even in the face of host system heterogeneity. Operations such as encryption may also be done at this layer.

- A *session layer* protocol exists to organize and synchronize presentation layer data units. Connection establishment and release may be done at this layer.

- A *transport layer* protocol is responsible for the end-to-end transfer of data units with certain reliability semantics from a session layer protocol in one host to a peer protocol in another. Issues such as multiplexing data units from several user processes onto a single network are often handled here. In addition, segmentation and reassembly of data units and error and flow control are often performed at this layer.

- A *network layer* protocol provides the means to route a transport layer data unit across subnetworks and through intermediate hosts to its final destination host. One of several access points to separate network links may be chosen at this layer in order to forward a data unit to its proper destination.

- A *data link layer* protocol enables the exchange of framed network layer data units between adjacent hosts on a multi-access or point-to-point network link. Various reliability semantics and error detection are often supported here.

- A *physical layer* protocol provides the ability to transfer the bits of data link protocol data units on the underlying physical medium. It specifies the mechanical and electrical standards of the medium as well as the signalling techniques involved.

Taken together, these protocols exist to provide communications services to application programs. The *data path* of a data unit sent from one application process to another starts at a sending process that submits data to the application layer. The data descends through all seven layers of the model and onto the physical medium. From there it propagates through the network, possibly ascending and descending through the protocols at layers one through three of the reference model in intermediate hosts. The data eventually reaches the receiving host, where it ascends all seven protocol layers before reaching the receiving application process. We refer to a collection of communications protocols organized into a stack covering each layer of the reference model as a *network protocol architecture*. In practice, one protocol may span multiple layers and some layers may be null. An example of a protocol architecture is the SAFENET architecture, which is discussed further in chapter four. A subset of the protocols in a protocol architecture that still covers each layer of the reference model is termed a *protocol suite*. An example of a protocol suite is the lightweight suite of SAFENET, which is also discussed in chapter four.

#### **1.3.** Protocol Implementation Possibilities

In this work we shall be concerned not with the details of the protocols residing at the layers of the reference model, but rather with their *implementation*. Particularly, we shall study the implementation of the transport and network layer protocols. When a protocol suite is to be realized in terms of an actual computer system and physical network hardware, we must concern ourselves with the production of each of its protocol layers. We introduce the term *communications architecture* to refer to the realization of an entire suite of protocols, serving a host computer system. Some components of the communications architecture may be built in host software, while others may be constructed off-host in additional hardware or firmware.

In the early history of computer networking, all but the physical layer communications protocols were implemented in the host computers, i.e., they were built in software executed by the host's central processing unit (CPU). Since physical layer protocols must modulate the physical medium and dictate mechanical standards, such protocols were necessarily implemented using special hardware devices. As time progressed, much of the functionality of the OSI data link layer has been implemented in additional VLSI hardware circuitry complementary to the host CPU [4][19][42]. The goal of this hardware has been twofold: (1) to perform protocol operations at generally higher rates of speed, and (2) to lower the burden of protocol processing on the host CPU [28]. The trend has been for an increasing amount of higher-layer protocol functionality to be performed in special-purpose hardware without the involvement of the host CPU. Following this trend, we investigate the implementation options for protocols at the network and transport layers. For the remainder of this work we assume that the physical and data link protocols are implemented on an integrated hardware device, hereby referred to as a *network interface*. In addition, protocols present at or above the session layer of the reference model are assumed to be implemented in host software and are not considered in any further detail. In the following sections we contrast the in-host versus off-host approaches to protocol implementation.

### 1.3.1. On-Host Implementation

The traditional approach to transport and network layer protocol implementations has been to place them in software on the host platform and execute all protocol operations using the host CPU. Once the choice has been made to use an on-host implementation, there are actually several possibilities concerning where its software may reside within the host. The choice of where to place the protocol implementation will likely be dictated by operating system architecture and security concerns.

In single-user or embedded computer systems, the secure use of shared resources between multiple processes is not typically a concern. Furthermore, there is seldom any address space partitioning between user processes and the operating system. In this environment, a protocol implementation may acceptably be in the form of library code linked with the code of an application program [41]. This approach has the benefit of avoiding operating system security concerns and complex address space issues. As a result, the protocol implementation is likely simpler and its performance is typically higher than that of other approaches. For example, with this implementation architecture, protocol services can be invoked via the relatively efficient mechanism of subprogram calls, thus promoting a low end-to-end latency. In systems with multiple processes or multiple users, shared resources often need to be managed in a more secure fashion. This is typically accomplished through the use of an operating system kernel residing in a protected address space. In such situations, transport and network protocol implementations reside in the kernel. The provision of security is necessary because such protocols may use special I/O address spaces, shared network resources, or shared data structures that must be kept with some degree of integrity.

In this kernelized scenario, application programs typically request protocol services from the kernel through system calls. The protocol software may be loosely integrated into the kernel as a device driver accessed through the operating system's I/O system calls [37], or it may be tightly integrated into the kernel and accessed with its own set of networking system calls [30]. Such calls are more sophisticated than subprogram calls; hence, they may result in a significant overhead. In addition, if the kernel resides in a protected address space, the cost of some means of accessing protocol data residing in the calling process' address space must be incurred. An additional drawback to the kernelized approach is that it complicates the software of the kernel.

A hybrid approach is to use a privileged server process, referred to here as a *protocol server*, to contain the protocol implementation. In such a situation, an application process desiring network service acts as a client, sending a request message for protocol service to the server via interprocess communication. The server process later sends a reply message to the client when it has completed the request [26]. Access to the shared resources is restricted to the server process, which, like the kernel, has a protected address space. This approach has the benefit of providing secure access to shared resources without adding to the complexity of the operating system kernel. In addition, no special system calls are required for network communication. It is not clear, however, whether the overhead of system calls is reduced or increased by this scheme. Furthermore, a unique source of overhead due to the protocol server approach is that process context swaps must occur between the client and server processes. No matter how the code of the protocol implementation is distributed in the host software, the host CPU has the sole responsibility of performing all protocol operations. The options mentioned vary only in the means in which higher layer protocols communicate with the protocol implementation. The actual approach to developing protocol software, once its in-host placement is determined, has been well studied.

# 1.3.2. Off-Host Implementation

Recent efforts have resulted in the implementation of network and transport layer protocols *off-host*. That is, such protocols are executed off-host by additional hardware rather than by the host's CPU. We refer to this additional hardware as a *protocol processor* device. Off-host protocol processor designs have been developed based on the use of a custom VLSI chipset, a general-purpose single-board computer, or a hybrid solution using both general-purpose microprocessor hardware and custom VLSI. This work is surveyed in detail in chapter three.

VLSI implementation is performed through the design of a chipset consisting of several application-specific integrated circuits. It has the advantage of (1) providing the very fast implementation of protocol functions through the use of custom circuits and (2) execution of protocol operations in parallel. The major drawback to this approach is that it is difficult to design VLSI circuits which perform complex tasks. As a result, the class of protocols that can be implemented in VLSI may be only those designed to be simple enough for that task [8][44].

With a general-purpose single-board computer (SBC), protocol operations may be carried out by a RISC or CISC microprocessor. Such an approach has the advantage that it is capable of handling even the most complex of protocols using software similar to that of an on-host implementation. The microprocessor approach has several drawbacks, however, with respect to performance. The speed of particular protocol operations performed on the microprocessor will almost certainly be lower than that of such operations performed with specialized VLSI circuits. In addition, the parallelism between individual protocol operations obtainable with VLSI circuits can simply not be achieved with a single microprocessor. The SBC approach may also suffer from fact that most general-purpose SBCs are not likely to feature an adequate combination of stock components, such as a large bank of high-speed static RAM, DMA controllers, and an on-board network interface, which may be necessary for a high-performance protocol implementation.

Hybrid solutions may be composed of a combination of custom VLSI circuitry and perhaps several microprocessors. With clever design choices, it may be possible to achieve much of the high performance and parallelism of a pure VLSI approach while still being able to tractably implement complex network and transport layer protocols by taking advantage of the flexibility of the SBC approach.

## 1.4. Possible Advantages of an Off-Host Protocol Implementation

Regardless of the specifics of hardware-assisted protocol implementation, the approach offers several potential advantages to network applications. An off-host communications architecture can benefit both the host processor and the protocol implementation. As a result, host applications can run faster and more predictably and the performance of the protocol services provided to such applications can be optimized.

### 1.4.1. Host Benefits

When using an off-host communications architecture, the host processor can potentially receive the following advantages:

*Reduced host load.* Since all protocol processing activities are handled on the protocol processor, no host processor cycles are consumed for protocol processing.

*Predictable application processing*. Since transport and network protocols perform retransmissions, react to incoming traffic, and sometimes block on network access, the execution times for protocol processing are nondeterministic. When using an off-host architecture, such nondeterministic activity occurs on the protocol processor and not on the host.

As a result, the CPU demands of host processes become more deterministic, thus promoting the predictable operation of such processes.

*Reduced and bounded host interrupt arrivals*. A transport or network layer protocol typically receives interrupts from its underlying data link service in order to indicate frameoriented activity. Some minimum number of frames are necessary for each transport service data unit (TSDU), and, in addition, an unbounded number of frames may arrive from other hosts or result from retransmissions. Each frame can cause a processor interrupt. When transport and network protocols run on a protocol processor, the host can be shielded from these interruptions. In such a scenario, host interrupts need only be performed by the protocol processor; thus, they can occur on a per-TSDU, rather than a per-frame, basis. This may result in substantially fewer host interrupts per TSDU. At the very least, these characteristics enable application processes to place a bound on the amount of interrupt handling in which the host will engage.

*Reduction of incident TSDU traffic*. One feature of hardware implementations of data link protocols in broadcast local area networks is that they, rather than the host CPU, filter incident traffic that is not addressed the host. Similarly, a transport and network protocol processor can deliver to the host only those TSDUs which the host desires to receive, thus shielding it from an accidental or malicious barrage of TSDU arrivals. Such a feature has been referred to as a "network firewall" [27].

### **1.4.2.** Protocol Benefits

A communications protocol can receive the following benefits when run on protocol processor hardware:

*Dedicated processing cycles.* When run on the host, a communications protocol must contend with application processes for processor cycles, thereby losing potential CPU cycles and incurring overhead from scheduling and context swaps. These effects can reduce the amount of work the host processor can perform for its application, cause slow response

to protocol events, and lower protocol throughput. With dedicated protocol processing hardware, all processing cycles are available to the protocol, thereby raising throughput, and context swaps can be avoided, thereby lowering latency and preventing protocol buffer overflow. Furthermore, such dedicated cycles, may be crucial in order for the protocol to handle the real-time processing requirements of continuous-media traffic such as voice and video.

*Specialized hardware*. Network and transport protocols can benefit from special hardware such as high-speed RAM, efficient DMA controllers, and custom checksumming circuitry. Such hardware may allow certain protocol operations to be accelerated or performed in parallel. Components providing these services can be utilized on the protocol processor device, providing performance not attainable with the general-purpose hardware of the host system.

Optimized data path to the network interface. Modern transport and network layer protocols make multiple accesses to the network interface for each TSDU passing through the session layer. Due to segmentation, protocol headers and trailers, and retransmissions, the traffic across the boundary between the data link layer protocol and the network layer protocol can be much heavier than that across the boundary between the session layer protocol and transport layer protocol. Thus the throughput of the former pathway should be optimized. One method of optimizing this path is through the placement of the network interface on the same circuit board as the protocol processor device.

*Ideal operating system environment*. It has been recognized that an operating system environment can place severe restrictions on a protocol's performance and proper implementation [48]. The timer, buffer, and lightweight process management services provided by the host operating system may be relatively inefficient for protocol tasks. In addition, the host operating system may impose security restrictions and other overhead which can hinder protocol performance. With an attached protocol processor board, one is free to choose the ideal operating system for the protocol implementation, including none at all.

#### **1.5.** Possible Pitfalls of Using an Off-Host Protocol Implementation

Several pitfalls may be encountered when using an off-host protocol implementation. The first set of pitfalls concerning operating system overhead are shared by both onhost and off-host approaches; however, the other pitfalls, those of overtaxing the host CPU and complicating the data path, are unique to off-host architectures.

# 1.5.1. Incurring Operating System Overhead

It is fallacious to believe that the problems of operating system overhead discussed in section 1.3.1 no longer exist when one uses an off-host protocol architecture. In secure, multitasking operating system environments the protocol processor hardware becomes a shared resource which must be managed by a trusted server process or the kernel. As a result, much or all of the system call and context swap overhead experienced in-host implementations can still occur in the off-host case. Address space complications imposed by the operating system may also pose a problem.

## 1.5.2. Overtaxing the Host Processor

The benefits of off-loading the host by partitioning protocol processing onto an attached processor may be eroded due to several sources of overhead:

*Control, Status, and Data Transfer.* When using an off-host architecture, the host processor has to perform a certain amount of communication with the protocol processor device. The host processor must, to some extent, drive the protocol processor by sending it control information and reading its status. Such overhead can not be avoided; however, care should be taken to minimize it, lest the host processor become overburdened. The transfer of TSDUs to and from the protocol processor is a prime concern. If the host processor is burdened with this task, the data transfer may consume a significant number of processor cycles. This overhead may be amplified if the protocol processor resides on a separate board on the host's I/O bus. This bus may have relatively low bandwidth and high latency in comparison to the data paths on the CPU board. The designers of an off-host protocol

architecture should seek to minimize the bus transfers required by the host CPU to use the services of the communication processor.

*Management of Shared Data Structures*. The host may also be made to allocate shared data structures such as buffers for communication between itself and the protocol processor. Similarly, designers may wish for the host to manage various protocol processor resources such as open connections. These tasks should ideally be performed only by the protocol processor device. If not, they should at least be avoided in the common case of data transfer.

*Multiplexing and Demultiplexing Command Requests and Status Responses*. In situations where multiple application processes may use the protocol processor, the host may also be required to multiplex protocol commands descending from multiple processes and demultiplex protocol status ascending toward one of many processes. This may require the protocol processor device driver to manage a state vector mapping protocol processor response data to a particular process. The management of such a data structure results in another source of host processing overhead.

*Notification of Command Completion.* Since the protocol processor executes asynchronously with the host processor, there must be a way for the host to discover when protocol processor status responses have arrived for it to receive. This results in the need for either an asynchronous notification mechanism such as hardware interrupts or the use of periodic polling of the protocol processor response stream. The host must expend some processor cycles to perform these tasks and also to act upon the such responses when they are present.

### **1.5.3.** Increased Data Path Complexity

Another set of pitfalls results from the complexity introduced by the addition of the protocol processing hardware into the network data path. These pitfalls may significantly affect protocol performance.

Low Bandwidth Connection to the Protocol Processor. The protocol processor may communicate with the host processor and host memory over a data path having relatively low performance. For example, the protocol processor may reside on a separate circuit board which resides on the host computer's I/O bus. Such a bus typically has lower throughput and higher latency than the host's CPU-memory bus. As a result, the off-host architecture may cause a performance drop on accesses to memory. Similarly the off-host architecture may force the data path between the protocol and the network interface to be over a low-performance medium; this may further degrade performance.

Additional Data Copies. Data from the higher-layer protocols may reside in the host's on-board memory, and addressing restrictions may require that this data be copied to local memory on the protocol processor device for processing. This copy occurs in addition to one that must eventually be performed to the network interface device. The effect of this additional copy may be a profound increase in latency. Furthermore, if the two copies are not performed in parallel, they may also have a serious effect upon protocol throughput.

Additional Bus Contention. If the protocol processor resides on the host's I/O bus, communication between it and the host may result in contention with other bus mastering devices such the network interface. This contention may erode system parallelism or may cause unpredictable protocol throughput or response times. Even if simultaneous requests for the use of the bus are not present, there may be an increased cost in the overhead of bus arbitration time due to alternating requests for bus mastership.

# 1.6. Summary

In this chapter we have motivated the study of off-host communications protocol architectures and discussed the possible benefits and pitfalls of employing such designs. In chapter two we cover the design issues inherent in off-host protocol architectures. Related work on off-host communications architectures from the literature is summarized in chapter three. Chapter four presents the design and implementation of an actual off-host communications architecture, and chapter five summarizes and profiles its performance, identifying system bottlenecks. In chapter six we develop an analytic model to predict the performance of off-host communications architectures, apply it to our own design, and validate its predictions against the observations in chapter five. In chapter seven we conclude, evaluating our off-host communications architecture and analytic model and making suggestions for future work. Methods of obtaining input parameters for the analytic model are presented in the appendices.

# 2 Design Issues in Off-Host Communications Architecture

# 2.1. Overview

In this chapter we present the issues intrinsic to the design of off-host communications protocol architectures. These center around the components of such architectures, their placement, and the communication between them. We first consider the interface between the host and protocol processor. Later we discuss the architectural levels spanned by an off-host communications architecture, followed by the hardware and software mechanisms used to communicate between the components at each level. In conclusion we discuss the philosophical extremes of off-host communications architecture design.

# 2.2. The Host-Processor Interface to the Protocol Processor

We restrict our discussion to communications protocol architectures in which the transport and network layer protocols run on an off-host protocol processor, the higher-layer protocols reside in the host, and the data link layer and below are on a network inter-face device<sup>1</sup>. Given this situation, we must have the ability to send and receive a transport service data units between the host CPU and the protocol processor. In addition, we must have a way to command transport layer services from the protocol processor and receive an indication of protocol processor status. Some architectures may employ additional mechanisms to provide options with the command and status information. In this section we discuss the attributes of the various streams over which this information must flow. These streams may span several architectural layers, and several communications mechanisms may be employed to implement their interlayer flow of information. These issues will be covered below in sections 2.3 and 2.4.

<sup>1.</sup> The issues involved in the protocol processor's communication with the network interface are similar to those of the host CPU's communication with the protocol processor. Furthermore, the network interface may be integrated into the protocol processor, eliminating these communication issues altogether. Therefore such issues will not be covered in this work.

# 2.2.1. Command Stream

The session layer must be able to request various services from the transport layer. When using an off-host protocol implementation, the session layer must request these services through the use of a well-defined set of protocol processor commands issued by the session layer to the protocol processor device driver, which is charged with submitting them to the transport layer on the protocol processor hardware via the command stream. As a result, some host processing overhead for executing protocol processor device driver software is unavoidable when using an off-host communications architecture. Since the protocol processor executes asynchronously, there must be a mechanism for the protocol processor to recognize that a command is pending for it to process. This may be accomplished through hardware interrupts or through polling as discussed in section 2.4. An additional concern is that the interarrival time of commands from the host CPU may be shorter than the protocol processor service time for such commands. As a result, queuing of protocol processor commands may be necessary, and a stochastic queueing delay may become a component of the overall latency of the off-host communications architecture. The queue may utilize one of several queueing disciplines such as first-in-first-out or priority-driven. In addition, such a queue is likely to be of finite length, or there may be a limit to the number of commands which can be pending for a given transport service access point. As a result, the session layer may have to block on submitting a command to the protocol processor device.

### 2.2.2. Status Stream

The protocol processor device driver must somehow become aware of the status of commands submitted to the protocol processor. This can be done using two styles of interaction and a *status stream*. One form of interaction is that the session layer may query the status of a command issued to the protocol processor. Another is that the transport layer may indicate to the session layer asynchronously that an event has occurred. These styles of interaction are similar to the use of interrupts and periodic polling. The protocol processor and its device driver may interrupt the session layer to indicate asynchronously the presence of pending status information from the transport layer, or the session layer may poll to synchronously read the status of the transport protocol as provided by the protocol processor. Interrupts and polling are discussed further in section 2.4. As with the command stream, the interarrival time of status information from the protocol processor may be shorter than the time for the host CPU to consume such information. As a result, queuing of protocol processor status may be necessary, and another source of stochastic queueing delay may be introduced into the aggregate latency of the off-host communications architecture. As is the case with a command queue, a status queue may employ one of many queuing disciplines. Note also that if there is a limit on the length of the queue used to supply status to the host CPU, the protocol processor may be forced to block on providing status to the host.

### 2.2.3. Data Stream

Each command or item of status information passed to or from the protocol processor may have a Transport Service Data Unit (TSDU) associated with it. This TSDU must be carried over some *data stream* between the two processors. It is important to point out that this data stream need only logically carry the data; that is, the data need not be physically copied between the protocol processor and host. In fact, copies of protocol data should be avoided since significant latencies and loss of throughput for large messages can result from introduction of extra data copies in a communications architecture. Architectural considerations and the nature of particular transport and network layer protocols may conceivably dictate the need for a physical data copy, however. Note that all data must undergo at least one physical copy in the communications architecture; such a copy is either to or from the network interface hardware. The data may pass either physically or logically through the data stream between the host and protocol processor, but it must always move physically through the network interface. In contrast with the command and status streams, queueing of data in the data stream may not be physically necessary since pointers to such data may be part of the command or status information which already undergo any necessary queuing. If queueing is required, however, it introduces issues similar to those discussed above.

#### 2.2.4. Options Stream

An *options stream*, similar to the data stream, may also be employed to pass options associated with commands and status between the host and protocol processor. Commands which require these options will incur additional overhead on both the host and protocol processor since additional processing is required to transfer and process this information. The benefit of an options stream is that it can minimize the amount of information present in the command and status streams. Information that need not flow in the common case of protocol processor activity can be left out of the command and status stream and included in the seldom-used options stream. The end result is that a minimum amount of command and status traffic occurs in the common case.

# 2.3. Hardware and Software Architectural Levels

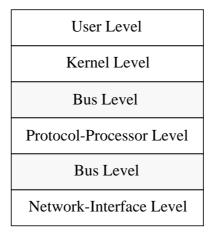

An off-host communications architecture consists of several levels of software and hardware architecture. These levels are the user level, kernel level, bus level, protocol-processor level, and network-interface level; the user, kernel, protocol-processor, and network-interface levels are structured such that they lay atop one another. The user and kernel levels are simply subdivisions of host software, whereas the protocol-processor and network-interface are hardware levels separated from each other and the host levels by the bus level. The relationship between the levels is illustrated in Figure 2.1. In some architectures, the kernel level is not present, or the protocol-processor and network-interface levels are unified. As discussed below, the nature of these levels is somewhat dictated by the operating system environment and hardware organization of the host computer system.

**Figure 2.1:** Architectural Levels

The components of the communications architecture, including the application program interface and specific protocol layers of the ISO OSI reference model, are distributed over each of the architectural levels. In this work we consider communications architectures in which the transport and network layer are implemented off-host on a dedicated protocol processor, the session layer and above are implemented in-host, and the data link layer and below are implemented on a network interface device. Our concern here is chiefly with the details of the protocol processor and its interconnection to other architectural components; however, we briefly sketch certain details of the implementation of surrounding protocol layers in order to explain how they fit into the complete off-host communications protocol architecture.

# 2.3.1. User Level

The user level refers to that at which application processes run in the host operating system. Such processes may send and receive application service data units (ASDUs) located in the memory of their address space. Applications transfer these ASDUs by invoking communication primitives from an Application Program Interface (API). An example of such an API is the socket interface of BSD UNIX [30]. At least part of the API implementation must reside at the user level so that it may be accessed by applications; however, much of the API implementation may also occur at the kernel level.

Another component of the communications architecture which may reside at the user level is the protocol processor device driver. For host operating systems such as MS-DOS [18] in which secure access to shared resources is not a concern, the protocol processor device driver may safely run at the user level. In such cases, the driver may be in the form of library code linked with an application program or it may be installed as a operating system device driver where its code still resides in the user-level address space.

In host computer systems with multiple processes or users, secure access to the protocol processor device may be a concern. In such cases it may be necessary to place the protocol processor device driver in a protected operating system kernel. An alternative to this approach, employed in operating systems such as Mach [1], allows device drivers to run securely at the user level. Such drivers run as privileged server processes as discussed in section 1.3.1. In these scenarios a small amount of kernel software may be required to perform privileged hardware operations that manage processor interrupts or to map hardware registers into the server process' address space. Note that in order to provide protection for shared resources, the server process' address space, albeit at the user level, must still be somewhat disjoint from that of the client processes requesting protocol processor service.

Program code for implementations of protocols at and above the session layer may also reside at the user layer. Such protocols may be in the form of library code linked with the code of an application, or the protocols may run as server processes.

# 2.3.2. Kernel Level

In operating systems such as UNIX [30] which provide the secure management of shared resources for multiple user processes, host memory is divided into protected address spaces. Each process has a private address space which it is separated from that of other processes and especially the operating system  $kernel^2$ ; the process may only access its own

address space. This protects kernel data structures and hardware devices from unsafe or malicious use. To ensure the secure use of an off-host protocol implementation in such an environment, the protocol processor device driver may be run in the operating system kernel. (A secure alternative employing a protocol server is discussed in the previous section.) When at the kernel level, the device driver executes in its own distinct address space. User-level applications may request secure services from the device driver through a restricted set of system calls. Software executing in the kernel layer typically executes in a privileged CPU mode that enables certain processor instructions useful in device drivers which are unavailable to user-layer software. For example, only kernel-level code may be able to execute privileged I/O machine instructions or enable, disable, and handle hardware interrupts. The software implementation of protocols at or above the session layer may also reside at this layer as may portions of the API implementation.

# 2.3.3. Bus Level

The hardware components of an off-host communications architecture must be connected with some variety of buses. Such hardware components are the host CPU, protocol processor, network interface, and memory. All communication between these components must occur over a bus as discussed in section 2.4.2.3. Note that there may be several buses within the host computer system and that some buses may allow multiple masters and some may not. The individual buses may have varying performance characteristics. One specialized type of bus is designed to have high performance, and is used to connect only a few high-speed components such as a processor and memory; such a bus is often termed a *memory bus*. Another type of bus is designed to be versatile; it typically connects I/O devices with varying response times and is termed an *I/O bus*. An I/O bus typically has slots to allow the insertion of several *modules* which are simply circuit boards that may contain

<sup>2.</sup> Note that in many operating systems, the term *kernel* refers only to the software which provides core system services and encapsulates the hardware; security features such as a protected address space and privileged instructions are not implied by this term. It should be recognized that in this work we use the term kernel in a stronger sense, implying the presence of these security features.

memory, a processor, or an I/O device. Some rare memory bus designs may also support the insertion of a small number of high-performance modules. Due to their flexible design, I/O buses typically have lower performance than memory buses.

# 2.3.4. Protocol-Processor Level

As discussed in section 1.3.2, the protocol processor may take the form of a custom VLSI application specific integrated circuit (ASIC) chipset, a general-purpose SBC, or a hybrid of the two. In this thesis we consider the case where the protocol processor implements both the transport layer protocol and the network layer protocol. Such a processor may reside either directly on the host CPU circuit board or as a module on a bus connected to it. The protocol processor may use its own local memory which may allow a faster access time than that of the memory used by the host processor. In fact, it may even be difficult or impossible for the protocol processor to address specific regions of host memory. This can be particularly true when the host uses virtual memory. The protocol processor makes use of a network interface device supporting the data link layer and below.

# 2.3.5. Network-Interface Level

In chapter one, we refer to the device supporting the data link layer and below as the network interface. This device is used by the protocol processor to transmit and receive data link layer SDUs, hereafter referred to as *frames*, to and from the network. The network interface may reside on the same board as the protocol processor, or it may be on a separate bus module. The network interface is unique in that it has some special data interface such as FIFO memory buffers which temporarily hold incoming and outgoing frames. It is at some point necessary for frames to be copied to these buffers in order to reach the network, regardless of the protocol or communications architecture in use. Similarly, it is necessary for incoming frames to be copied from these buffers. Hence, all communications architectures will require *at least one* copy of the data contained in application service data units.

# 2.4. Communication Mechanisms Between Levels

A critical issue determining the performance of a communications architecture is the set of communication mechanisms employed between its components. This section describes the possible mechanisms which may be used between the components at each layer of a communications architecture. We first examine communication between the software components of the host computer system, followed by that between the hardware components of the communications architecture.

Before we examine how data transfer can occur between the layers of the communications architecture, we first review what sort of information will be transferred. We take as an example the interlayer communication necessary for transmission of an ASDU onto the network media from an application process. The ASDU exists as a data structure physically located in the host computer's memory and logically in the user-level address space of the application process. It passes through the protocol suite enroute to the network. As it does, protocol control information is appended to the message as it becomes an SDU for the various protocol layers. This data migrates through each of the architectural levels discussed in the previous section. In addition to this data transfer, control, status, synchronization information, and perhaps options must pass between certain layers of the communications architecture. For example, a protocol processor device driver at the kernel level must write control information to the protocol-processor device at the protocol-processor level and read the device's status. In addition, the host CPU may need to synchronize with the protocol processor in order to notify it that a command is pending. Likewise, the protocol processor may need to notify the host of the completion of a command.

## 2.4.1. Communication Between the User and Kernel Levels