# THE WM COMPUTER ARCHITECTURE DEFINITION AND RATIONALE Version 1

Wm. A. Wulf

Computer Science Report No. TR-88-22 October 21, 1988

# The WM Computer Architecture Definition and Rationale Version 1

Wm. A. Wulf

Computer Science Department University of Virginia Charlottesville, Va.

21 October, 1988

### **Table of Contents**

| Abstract                                                       | .1       |

|----------------------------------------------------------------|----------|

| Acknowledgements                                               | .1       |

| Chapter 1. General Features                                    | .2       |

| Chapter 2. Logical Machine Structure                           | .5       |

| 2.1. Addresses & Data                                          | 5        |

| 2.2. Integer and Floating Point Execution Units                | 7        |

| 2.3. Memory Reads & Writes                                     |          |

| 2.5 IO                                                         |          |

| Chapter 3. Instruction Descriptions                            | .16      |

| 3.1. Integer Arithmetic & Logical Instructions                 | 16       |

| 3.2. Load & Store Instructions                                 |          |

| 3.3. Control Flow Instructions                                 |          |

| 3.4. Floating Point Instructions                               |          |

| 3.5. Special Instructions                                      |          |

| Chapter 4. Task, Program, and System Framework                 |          |

| 4.1. Task State                                                |          |

| 4.2. Protection Table                                          |          |

| 4.3. Map Table                                                 |          |

| 4.4. Traps (Exceptions) and Interrupts                         |          |

| 4.5. Devices                                                   |          |

| Appendix A. Summary of Restrictions on Valid Software          | 40       |

| Appendix B                                                     |          |

| B.1. Integer Format and Operation Encodings                    |          |

| B.2. Load/Store Format and Operation Encodings                 |          |

| B.3. Floating Point Format and Encodings                       |          |

| B.4. Control Format and Operation Encodings                    |          |

| B.5. Special Format and Operation Encodings                    | 44       |

| Appendix C. WM Assembly Language                               |          |

| C.1. Lexical Structure                                         |          |

| C.2. Instructions                                              |          |

| Appendix D. Streaming Versus Vectorizing                       |          |

| D.1. The Issue                                                 |          |

| D.2. An Example, Matrix Multiply                               |          |

| D.3. Another Example, an IIR Filter                            |          |

| D.4. Another Example, FFT Inner Loop                           |          |

| D.5. Other Applications of Streaming                           |          |

| Appendix E. Rationale Behind Chosen Operation Sets             |          |

| E.1. Integer & Logical                                         |          |

| E.2. Floating Point                                            |          |

| E.3. Load/Store Instructions                                   |          |

| E.4. Control Instructions                                      |          |

| E.5. Special Instructions                                      |          |

| Appendix F. Constructing WM Software Suggestions and Rationale |          |

| F.1. Calling Sequence and Register Conventions                 |          |

| F.2. Ada Exceptions                                            |          |

| F.3. Parameter Passing                                         |          |

|                                                                | 04<br>6⊿ |

| F 4 Loop Control                                               |          |

| F.5. T | he | Display        | 35 |

|--------|----|----------------|----|

|        |    | lute Addresses |    |

.

### **Abstract**

This report is a preliminary definition of, and rationale for, the WM computer architecture. It is not quite a rigorous architectural definition, nor a thoroughly motivated tutorial. Rather it is something in between. Its purpose is to put a stake in the ground; we expect there will be changes as we implement the machine, but this is the point from which the implementation will proceed. Thus we attempt here to capture not only the current design, but something of the philosophy and rationale behind the decisions in the design -- so that, as we go forward, we can retain some consistency of vision.

It can be said that there is very little in the WM design that has not appeared in some other computer previously -- just as it can be said that Frank Lloyd Wright used the same old doors and windows as his predecessors. Architecture is not about the components of a design, it is about their composition. Specifically, it is about how a particular composition affects a very complex objective function.

In the case of computer architecture the objective function has never been formulated, and, indeed, many of the arguments about the desirability of brand X vs. brand Y are really arguments about the relative importance of aspects of the objective function. In the case of WM, at least, we tried to maximize concerns as diverse as

- performance: cycle time (critical paths), multiple operations per cycle,

realistic peak vs. sustainable performance, ...

- implementability: testability, pin counts, memory bandwidth, available

chip densities, ...

- specificity: precise architectural definition without over-constraining

implementations

- compilability: availability and efficacy of algorithms, ...

- system issues: real-time applications, OS overheads in multi-user

systems, use in embedded applications, use in multi-

computer systems, ....

- applicability: don't favor one class of computation over another

- algorithms: eschew need for algorithm (re)invention

The WM architecture should be evaluated in terms of how well the composition of its components affects these objectives.

### Acknowledgements

A number of people have made contributions to the design of WM. Professor Charles Hitchcock of Dartmouth has been involved from the beginning, and is responsible for a number of the machine's unique features. Professor Anita Jones, has been a patient sounding board, and has developed some of the WM software. Jim Aylor, Alan Batson, Jack Davidson, Barry Johnson, Anita Jones, Peter Kester, Sunil Pamidi, Max Salinas and Tim Sigmon are the core of the WM team at Virginia. Ivan Sutherland and Bob Sproull asked the right, sometimes embarrassing, questions at just the right time.

WAW

### Chapter 1. General Features

WM is a computer architecture designed to support rapid execution and compact representation of programs written in high-level languages. It is a combination of innovative computer architecture and fast, modern machine features. Its elements support each other quite synergistically. The net result is an architecture with (a) roughly the hardware complexity associated with RISC machines, (b) roughly the code densities associated with CISC machines, and (c) roughly the performance associated with "mini-supercomputers" -- and all this is achieved with almost no increase in compiler complexity.

The most important additions to computer performance are found in three features:

#### Concurrent ALUs

A single machine instructions may specify two integer/logical or two floating point operations; each such instruction may operate on 2, 3, or 4 operands. The integer and floating point units are separated so that an integer and a floating point instruction can be dispatched simultaneously. Moreover, the integer and floating point units are each implemented by pipelined ALUs. In principle, therefore, WM can dispatch 4 arithmetic operations per cycle.

### Streaming

A mechanism is provided for asynchronous accesses of "vector-like" data, that is, data with a known displacement between successive items. A single instruction can be executed to cause a "stream" of such data items to be delivered to WM's execution units, which can then be processed at the speed of the consuming algorithm. This scheme is similar to, but more general than that found in "vector" supercomputers, and gives the effect of executing

as many as 8 load/store instructions per cycle in addition to the 4 arithmetic operations per cycle.

Fast Conditionals

A new approach to conditional jumps is taken that allows most such operations to take NO execution time -- that is, their execution time can be completely overlapped with that of other instructions.

The net effect of these three features is a peak performance 13 RISC-like operations per cycle. Other important architecture features that further enhance the performance and applicability of WM include:

Micro-concurrence

The ability to dispatch multiple operations per cycle is significantly enhanced by a careful decoupling of independent execution units, and synchronizing their actions through FIFOs.

32-bit Instructions All instructions are 32-bits. This aids in numerous ways, such as by expanding the relative jump distance, providing quicker decoding, eliminating awkward page-fault situations, and simplifying the prefetch requirements.

Load Prefetch

WM is a load/store machine, but loads can be started well before a memory data item is needed. This reduces the effect of a long memory access latency.

Large Register Set

64 register names are provided -- of which 28 are integer/logical "general" registers, 30 are floating-point registers, and 6 are functionally specific (see section 2.3 concerning the WM memory/processor interface).

Parameter Passing

A parameter passing mechanism is incorporated that is faster and more convenient than previous methods.

Ada Influence

WM was designed with the needs of high-level languages, as well as the capabilities of modern optimizing compilers, in mind. Of particular interest was rapid execution of Ada programs -- both because of the growing importance of Ada and because it provided a good "stress test" on the success of this aspect of the design. in particular, constructs that are awkward on other modern computers, such as proper loop control, exceptions, constraint checking, and tasking, are smoothly supported on WM.

Operating System Support

WM provides a number of features to support operating systems; the general philosophy being to move as much functionality as possible safely into ordinary,

unprivileged "user level" code. The result is that it is possible to

- directly handle IO devices from user programs

- have user programs act as a scheduler for a set of other user tasks

- build a compartmented, multi-level military security system easily

Each of these provides the possibility of significant reductions in operating system overheads.

### Chapter 2. Logical Machine Structure

This chapter describes the basic framework of the WM machine, such as its data types, logical memory interface, and implied stack structure. Those familiar with modern computer architectures may wish only to skim the material on data and addressing. However, there are several unusual aspects of the WM design covered in the sections "Execution Units" and "Memory Reads & Writes"; these should be read carefully.

### 2.1. Addresses & Data

#### 2.1.1. Addresses

Addresses on the WM architecture are 32-bit values and memory is 8-bit byte addressed. WM systems are "paged", and addresses are translated and protected as described in Chapter 4.

#### 2.1.2. Data Sizes

Data elements in memory may be stored in 8-bit byte, 16-bit halfword, 32-bit word, or 64-bit doubleword sizes. Data elements are assumed to be aligned. For example, addresses of halfword data elements are assumed to have a zero least significant bit, thus specifying a halfword boundary. In fact, this least significant address bit is ignored when accessing such data elements. All instructions are 32-bits in length, and the Program Counter (PC) always specifies a word-aligned address. Default instruction sequencing is linear and increasing (i.e., the execution of the instruction at address XXX+4 follows the execution of the instruction at address XXX).

WM is a "load/store architecture", that is, data manipulation can only be performed on (between) registers. Separate instructions are required to move data between the registers and memory. There are 32 general register names that may be specified in an instruction -- however integer and floating point registers are distinct, providing 64 total register names. Four register names in the integer unit and two in the floating point unit are reserved for special meanings, as will be discussed in section 2.3.

### 2.1.3. Data Types

These data types are supported by the WM architecture:

### Boolean Values

No explicit instructions exist to support operations on boolean values. However, the available operations were created with such support in mind. In particular, any bit in a register may be set, or selected in one instruction, and any bit may be cleared or tested in 2 instructions. These macro functions are synthesized by the proper operation combination. Vectors of boolean values may be loaded from and stored to memory as bytes, halfwords, words, or doublewords. 32-bit boolean vectors may be logically manipulated with register/register instructions. Shorter boolean fields may also be extracted from larger vectors with a single instruction.

### Signed Integer

Values

Arithmetic on 2's-complement 32-bit signed integers is supported by individual operations on this machine. While signed integers may be loaded and stored as words, halfwords, or bytes, all integer arithmetic is performed on 32-bit register quantities. Unsigned integers are not supported by the machine; they are viewed as a subset of the signed integers (as Ada defines NATURAL). Explicit underflow checking is required when synthesizing unsigned arithmetic with this architecture.

#### Floating Point

Values

Both single- and double-precision floating point formats of the IEEE floating point standard are supported. The terms "float" and "double" in this document refer to single- and double-precision floating point data and/or operations, respectively.

### 2.1.4. Data Numbering

The current architecture description is "big-endian", although a simple rewrite could make it "little-endian" without substantive change. It seems more important that the description be consistent, which we have tried to do.

Bits within bytes, halfwords, words, and doublewords are numbered from left to right starting with 0. The lefthand side is the most significant. Bytes within larger entities, such as words, are also numbered from left to right starting with 0. The last byte (number 3) in word 327 is just before the first byte (number 0) in word 328.

### 2.2. Integer and Floating Point Execution Units

The data manipulation instructions of WM specify 3 source operands, 2 operators, and a destination register, and evaluate an assignment of the form:

$$R0 := (R1 \text{ op1 } R2) \text{ op2 } R3$$

The source operand of integer/logical instructions may be the contents of a register, the contents of an input FIFO (see the next section), or unsigned literals; the destination may be either a register or an output FIFO. The source operands of a floating point instruction may be either a register or an input FIFO, and the destination may be either a register or an output FIFO (floating literals are not supported as source operands).

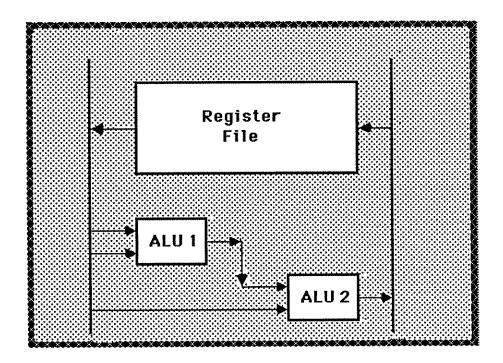

The execution units of WM are implemented as a pair of pipelined ALUs, as shown in the following figure. In general, while the second (outer, op2) operation of one instruction is being executed in ALU2, the first (inner, op1) operation of the successor instruction is being executed in ALU1.

The pipelined structure of the WM execution units induces the data dependence rule:

The result of an instruction is not available as an operand of the inner operation of the following instruction. The value of an inner operand is specifically independent of the effect of the previous instruction.

Valid programs must obey this rule. Clever programs will exploit it.

The integer/logical registers are distinct from the floating point registers. Integer/logical instructions refer to the integer registers; floating point instructions refer to the floating point registers. Conversion instructions (e.g., "convert integer to floating") refer to one register of each type as appropriate. Integer instructions are used for address computation, and to specify data transfers between memory and registers of both types.

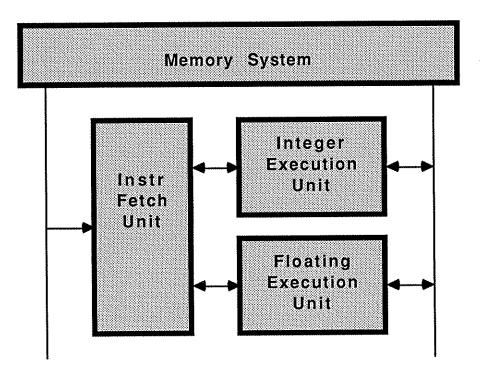

Since integer/logical and floating point operations as well as data are distinct, the proper conceptual model of WM is one with two execution units (of the general form shown above) under common control of the "instruction fetch unit". Note that the independence of the integer and floating point units permits concurrent execution under most circumstances. A more precise definition of when concurrence is not allowed will be discussed later.

### 2.3. Memory Reads & Writes

The method of accessing memory in WM is somewhat unusual:

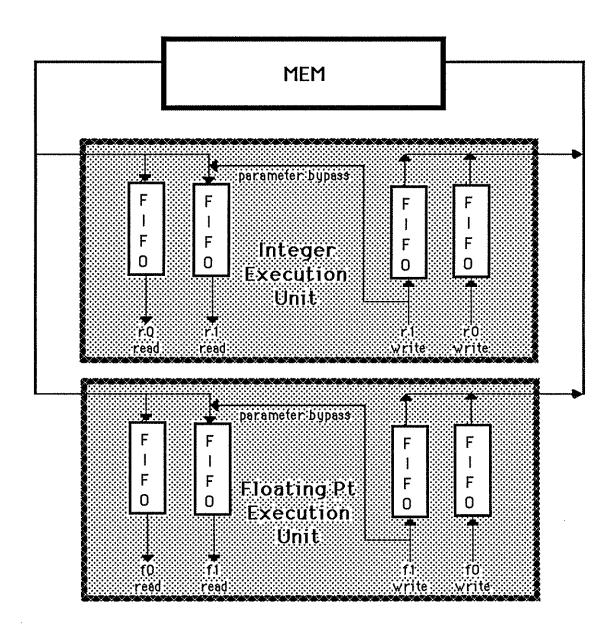

- 1. WM interposes FIFOs ("first in, first out queues") between the register set and the memory. Load and store instructions are operations on these FIFOs.

- 2. In most machines, memory reads and writes require specifying two quantities: a register name and a memory address -- e.g., "load the contents of location 42 into register 13". In WM, by contrast, loads and stores specify only an address, because

- a load is a request to enqueue data from memory into an input FIFO, and

- a store is a request to dequeue data from an output FIFO and store it to memory.

In both cases, only the memory address is required.

3. To dequeue a datum from an input FIFO, an instruction need only reference register 0 as a source operand. To enqueue a datum in an output FIFO, an instruction need only specify register 0 as the destination of a computation.

To read a value from memory, a LOAD instruction is first used to compute a memory address. This is passed to the memory system and the data transfer is initiated. Multiple load instructions may be executed; the data is read in the order of the LOAD instructions and queued in an input FIFO. The execution units access the queued data by referencing register 0. When register 0 is read as part of a computation, the next value is taken out of the FIFO and used.

To write a value to memory, that value may first be written (or computed) into register 0; as a consequence it is enqueued in an output FIFO. Then, at some later time, a STORE instruction may be issued which computes a memory address. Once both actions have been completed, a copy of the value that was written into register 0 is written to memory at the computed address. Because "register 0" is a FIFO, several values can be computed into it before a STORE instruction is executed.

The write to a memory location could have been accomplished in the other order -the STORE instruction could have been executed before the instruction that computes the

value to be stored; the action of writing to memory is taken only when an appropriate

pair of instructions have **both** been executed. And again, several STORE instructions

could have been executed before the first value to be stored is computed into register 0;

the addresses are queued until the value to be stored is computed.

Note that register name 0 specifies different things when read and when written. Reading register 0 takes a value from the memory input FIFO. Writing register 0 prepares a value to be written to memory.

Finally, note that the LOAD and STORE instructions themselves are executed on the integer/logical unit and the addresses they compute are directed to the proper FIFO (i.e., the address computed by the "load floating" instruction is directed to the floating point FIFO).

The size of the input and output FIFOs are implementation defined, although the architecture requires at least:

- 3 32-bit entries in the integer unit's input FIFOs

- 1 32-bit entry in the integer unit's output FIFO

- 3 64-bit entries in the floating unit's input FIFOs, and

- 1 64-bit entry in the floating unit's output FIFO.

These minimums are adequate to ensure that a single instruction can execute, even if it names all its source operands and it's destination operand as FIFOs. Generally, implementations should provide more entries in each of the FIFOs in order to allow software to perform better.

For any particular implementation, hence specific FIFO sizes, it is possible to construct a program that will deadlock -- for example, by trying to enqueue more than a particular FIFO can hold. Such programs are *invalid*. See appendix A for a more complete discussion of invalid programs.

### 2.3.1 Parameter Bypass

Register 1 is also a FIFO, albeit with somewhat different properties than that of register 0. Specifically, a value stored (computed) into register 1 is immediately enqueued in the register 1 input FIFO. As with register 0, items are dequeued from the register 1 input FIFO simply by using register 1 as a source operand.

Thus, register 1 is a short buffer that might be used, for example, to hold a short queue of temporary values. The primary intent of this mechanism, however, is to hold parameters during a subroutine call -- the caller enqueues actual parameters, and the called routine dequeues formals. See Appendix F for a discussion of the suggested WM calling sequence.

### 2.3.2 Streaming

The memory system also supports the reading and writing of "streams" of data. A data stream is an linear sequence of memory items, all of the same size and type, that start at a known address and are spaced a constant distance (stride) from each other.

Either register 0 or register 1 may be used in stream mode; that is, each of these registers supports two modes of operation, normal and streaming mode respectively. Normal mode for register 0 is the LOAD/STORE mode described at the beginning of section 2.3. Normal mode for register 1 is the parameter bypass mode described in section 2.3.1. Stream mode is identical for both registers, and is described here.

When in streaming mode, no load or store instructions need to be issued in order to initiate the next data transfer; a single "start streaming" instruction initiates the transfer of the entire stream. Asynchronous "stream control units" compute the addresses of the "next" data item. and initiate the transfer.

When streaming, data is removed from the input FIFOs in the same manner as in non-streaming mode -- that is, by instructions that reference register 0 or register 1. Similarly, by designating register 0 or register 1 as the destination of an instruction, data is inserted into the output FIFO (same as the normal mode for register 0 but different from register 1's normal mode.) If streaming is performed only with register 0, programs that exploit streaming are functionally identical to those that do not, except that the effect of the LOAD and STORE instructions in non-streaming programs is performed asynchronously by the stream control units. If register 1 is involved in a stream, however, the parameter bypass capability is not available.

Streaming provides functionality and performance similar to that of high speed "vector" architectures, but

- it is more general in the sense that it can do everything that a vector unit can, plus a great deal more. Computations done by vector instructions are typically "small" -- e.g., simple component-by-component adds or multiplies. Computations on streamed data are, by contrast, arbitrary software combinations of WM's "scalar" instructions. In particular, this

- allows streaming of computations involving recurrences (which cannot be vectorized) and reductions (which are supported on only some vector machines).

- it requires no additional hardware (e.g., no vector registers, no separate ALUs, etc.).

- much simpler and more complete compiler algorithms can be used to detect streaming opportunities than to detect vectorization opportunities.

### 2.4. Stack Structure

The WM architecture has Stack Limit and Stack Index registers defined to be registers 2 and 3 of the integer execution unit, respectively. The Stack Limit register is guaranteed by software to lie on a page boundary, thus having its lower bits be zero accordingly. (The page size is implementation-dependent, so the number of zeroed lower bits is not specified.) The Stack Index contains an integer such that the address of the top of stack is computed as follows:

TOS := SL + SI

The Stack Index normally has a negative value. The stack grows towards the positive addresses, and a transition from negative to positive Stack Index is the overflow condition. This condition is checked by hardware whenever the Stack Index is written; an exception is generated if it is met. The Stack Limit may only be written by programs with proper privileges. No push or pops are supported, nor needed, on this machine. The stack is not for expression evaluation, but merely for procedure interface. As such, being able to adjust the effective top of stack is sufficient, given that most parameters are passed via the input FIFO associated with register 1.)

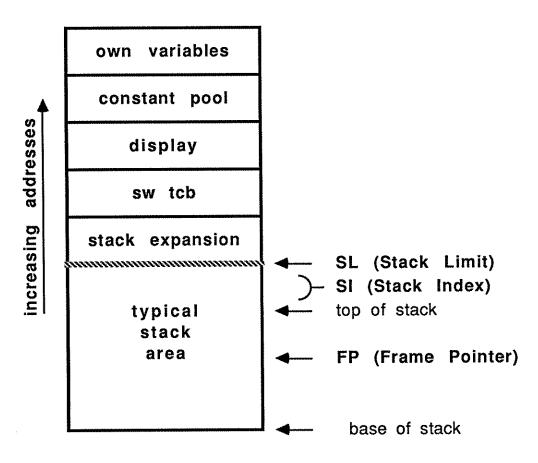

The hardware support for the stack, together with the general instruction set facilities of WM, encourage an overall stack layout such as shown in the figure below below. The various areas of the stack are:

- stack expansion area: this area is normally unused -- but provides temporary stack expansion while, for example, a exception is taken and the program stack was near its limit (this implies that exception handlers must be careful about the amount of stack they use, but allows graceful handling of otherwise awkward situations).

- software task control block: this is a software-defined area for recording task status. There is also a hardware-defined task save area that has special protection associated with it (see chapter 4 for further detail.).

- display: this area is, by software convention, used to hold the display (note, the display is somewhat different than the usual; see Appendix F).

- constant pool: this area, by software convention, is used for storing constants larger than those that can be synthesized in normal instructions.

- own variables: this area is, again, by software convention, used for statically allocated variables and the constant pool for the task.

Note that, in general, Ada requires a "cactus stack"; only one branch of this stack is shown here. In general, the display elements may point into lower branches of the stack.

Besides registers 0, 1, 2, and 3, all other register names specify truly general purpose registers. Note, however, that the hardware uses some of the general registers (e.g., the PC is stored in register 4 by a CALL instruction), and that software may impose additional conventions -- thus not all 28 general registers are available for computation. Appendix F discusses this in more detail.

Other aspects of the machine state, such as the Program Counter (PC), the Cycle Counter (CC), the Program Control Word (PCW), and the Program Status Word (PSW) cannot be directly accessed by instruction (other than certain bits of the PSW which may be set as a side effect of another instruction -- e.g., the condition code); these registers are only (re)set as a consequence of a context-swap.

### 2.5 10

Control of input/output devices is "memory mapped"; that is, there is a portion of the physical address space reserved for "device registers". This, together with the address translation and protection mechanism discussed in Chapter 4, provides great flexibility -- it even allows one to safely permit unprivileged applications programs to directly access IO devices, thus eliminating operating system overhead from them.

At least three devices are required of all implementations:

- "the CPU", control and status registers for the processor itself. Chapter 4 contains more details, but, for example this allows one processor to start/stop another, allows diagnostic probing of the processor, and replaces a number of instructions (such as HALT) with bit set/reset operations on this device register.

- one or more "timers", which are 32-bit counters that decrement each 100ns and, if enabled, interrupt when they become negative (but continue counting until reset), and,

- a "calendar" which is a 64-bit counter that is incremented each 100ns, runs continuously when power is enabled, and will interrupt when it overflows.

### Chapter 3. Instruction Descriptions

The WM instructions are grouped by function and decoding into the following five categories:

- Integer Arithmetic & Logical

- Load & Store

- Control Flow

- Floating Point

- Special

The following sections describe each set of instructions in some detail.

### 3.1. Integer Arithmetic & Logical Instructions

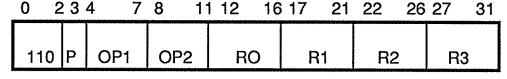

The integer arithmetic and logical instructions all take the form1:

$$R0 := (RL1 \text{ op1 } RL2) \text{ op2 } RL3$$

There are three source specifiers (RL1, RL2, and RL3), two operation specifiers (op1 and op2), and a destination specifier, R0. R0, RL1, RL2, and RL3 may specify one of 32 register names. Alternatively, RL1, RL2, and RL3 may specify a 5-bit literal (which is zero-extended to 32-bits); the RL field determines this interpretation. The operands are either 32-bit signed integers or a vector of 32 boolean values, depending on the operation specified. The instruction format is:

<sup>&</sup>lt;sup>1</sup>Here and in the following, we observe the convention that capital "R" denotes a register field of an instruction, and a lower case "r" denotes a specific register. "RL" denotes an instruction field that may be either a register or a literal.

| 0 | 1 3 | 4 7 | 8 11 | 12 16 | 17 21 | 22 26 | 27 31 |

|---|-----|-----|------|-------|-------|-------|-------|

| 0 | RL  | 0P1 | 0P2  | RO    | RL1   | RL2   | RL3   |

Bits 1, 2, and 3 specify if RL1, RL2, and RL3, respectively, are 5-bit literals (bit equal 1) or register names (bit equal 0). The operation fields, op1 and op2, are encoded identically. The 16 functions they can specify are:

| +          | addition                                                                                                                                                                                                        |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *          | subtraction                                                                                                                                                                                                     |

| -1         | reverse subtraction: (a-b)==(b-'a)                                                                                                                                                                              |

| and        | bitwise AND                                                                                                                                                                                                     |

| or         | bitwise OR                                                                                                                                                                                                      |

| eqv        | bitwise EQUIVALENCE                                                                                                                                                                                             |

| *          | multiplication                                                                                                                                                                                                  |

| /          | division                                                                                                                                                                                                        |

| <i>/</i> * | reverse division: (a/b)==(b/'a)                                                                                                                                                                                 |

| asl        | arithmetically shift (to the left) the left operand by the amount of                                                                                                                                            |

|            | the right operand (performs scaling)                                                                                                                                                                            |

| conx       | shift the left operand left 5 bits and or it with the lower 5 bits of<br>the right operand. If the left operand is a literal, then it is sign-<br>extended. (Used to create 10- and 15-bit signed<br>literals.) |

| =          | equal                                                                                                                                                                                                           |

| <          | less than                                                                                                                                                                                                       |

| <=         | less than or equal                                                                                                                                                                                              |

| >=         | greater than or equal                                                                                                                                                                                           |

| >          | greater than                                                                                                                                                                                                    |

Note that there are no unary (monadic) operators in this collection; this is because the monadic operations can be synthesized from the dyadic ones and literals. Specifically,

$$-x == (0-x)$$

, and not  $(x) == (x \text{ eqv } 0)$

The last five operations are the relationals. They produce their left operand as a result. They also produce a boolean value. If two relationals exist in the same instruction, their boolean values are or'd together and written to the conditional bit. Otherwise, the single boolean value sets a condition bit in the PSW<sup>1</sup>. If the boolean result is False, then the condition bit is set, but the instruction's register write and exception conditions are nullified. As will be discussed later, valid programs must adhere to the rule that exactly one instruction with relational operations is executed (dynamically) for each conditional jump instruction executed.

<sup>&</sup>lt;sup>1</sup>Note, there is a small FIFO of condition bits in the PSW.

Such relationals support general conditional branching for loops and if-then-else constructs found in high-level languages. Their semantics also allow for efficient Ada looping and range checking. An Ada loop may use Integer'Last as its upper bound. In such cases, a comparison of the bound and the loop counter must be made before the counter is incremented. Otherwise, an overflow would result, which it shouldn't. The instruction:

provides this function efficiently. The relationals also allow for Ada range checking in a single instruction. The instruction:

checks to see if the value in register 8 is in the range [1..12], since the result of the two relationals is OR'd together.

### 3.1.1. Exceptions

The following arithmetic conditions result in exceptions unless masked off in the PSW:

- Input FIFO 0/1 Empty: an attempt to read r0 or r1 was made when no value is present in the FIFO, nor is any value scheduled to be loaded.

- Output FIFO 0/1 Full: an attempt to write r0 or r1 was made when the associated output FIFO was already full, and no value is scheduled to be stored.

- Overflow/Underflow: an arithmetic operation overflowed or underflowed

- Divide by 0: an attempt to divide by zero was made

### 3.2. Load & Store Instructions

The LOAD and STORE instructions specify two things: (1) the address of the data to be read or written, and (2) the size/type of the data (e.g., byte vs. halfword vs. double-precision floating point).

(1) The address computation is formally and semantically identical to the assignments of the integer/logical instructions:

$$R0 := (R1 \text{ op1 RL2}) \text{ op2 RL3}$$

The only differences are that the set of operators is smaller, R1 cannot be a literal, and, more importantly, the result of the computation is sent to the memory system in addition to being sent to the destination register. The permitted operations are:

+ addition

- subtraction

asl arithmetical shift left

conx form constant

The definition of each of these is the same as it's integer/logical counterpart.1

(2) The type/size of the data to be read or written is specified by the LOAD or STORE instruction.

#### On LOADs:

- word, halfword, and byte requests (possibly sign-extended) are sent to the input FIFO associated with register 0 in the integer execution unit.

- floating and double requests are sent to the input FIFO associated with register 0 in the floating point execution unit.

#### On STOREs

- word, halfword, and byte requests (possibly checked for range violations) are sent to the output FIFO associated with register 0 in the integer execution unit.

- floating and double requests are sent to the output FIFO associated with register 0 in the floating point execution unit.

Once a load instruction has been issued, a following instruction may attempt to read the associated input FIFO (by referencing register 0). This instruction will not be issued until a value from memory is available. In fact, a single instruction may reference register 0 three times as a source operand, and thus read up to three values from the input FIFO, so long as a LOAD has been performed for each such reference.

The memory system is responsible for ensuring that certain sequences of load/store operations are performed properly, as specified below. However, these sequences are guaranteed to function properly *only* with respect to the IEU and FEU separately; loads and stores from one execution unit are not synchronized with those of the other!

```

STORE (to address X)

LOAD (from address X)

```

loads the same value as was stored. Conversely, the sequence:

```

LOAD (from address X) STORE (to address X)

```

reads the "previous value" of location X. Finally, the sequence:

```

r0 := Y

STORE (to address X)

r0 := Z

STORE (to address X)

```

must result with the value Z at location X in memory.

<sup>&</sup>lt;sup>1</sup> Note: prepending these operator codes with "00" produces the integer/logical encodings of the same operators.

The format of load and store instructions is:

| 0 1 | 23 | 4 7  | 8  | 11 | 12 16 | 5 17 | 21 | 22 26 | 27 31 |

|-----|----|------|----|----|-------|------|----|-------|-------|

|     |    |      | ор | ٥р |       |      |    |       |       |

| 10  | RL | LSOP | 1  | 2  | RO    | R    | 1  | RL2   | RL3   |

Bits 2 and 3 specify whether RL2 and RL3, respectively, are 5-bit literals (bit equal 1) or register names (bit equal 0). R1 must name a register. The LSOP field encodes the load/store function, which may be one of:

| LD<br>LF<br>LW<br>LH<br>LB<br>LHX<br>LBX | Load Double Load Floating Load Word Load Halfword zero extended Load Byte zero extended Load Halfword sign-eXtended Load Byte sign-eXtended |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| SD<br>SF<br>SW<br>SH<br>SB               | Store Double Store Floating Store Word Store Halfword Store Byte                                                                            |

| SHA<br>SBA                               | Store Halfword with Arithmetic range check<br>Store Byte with Arithmetic range check                                                        |

The last two store instructions, SBA and SHA, verify that the value to be stored is arithmetically representable in the storage unit into which it will be stored; e.g., SBA checks that the value is in the range -128..127. The SB and SH instructions, by contrast, simply store the least significant 8 and 16 bits of the value, respectively.

There are 14 LSOP operations; the other two opcodes are illegal and will produce an illegal instruction trap if used.

Other instructions that are related to the loads and stores, but are discussed in the Special Instruction section, include:

- Context Save and Restore

- Streaming Instructions

### 3.2.1. Exceptions

The following exceptions may occur as a result of a load or store instruction:

- Input FIFO 0/1 Empty: as per integer instructions when used as a source operand in the address calculation.

- Input FIFO 0 Full: an attempt was made to perform a load when the input FIFO was already full, or will be full after some pending loads complete.

- Output FIFO 0 Empty: an attempt has been made to perform a store when the output FIFO is empty and no further address can be buffered.

- Output FIFO 0/1 Full: as per integer instructions when specified as the destination register for the address calculation.

- Overflow/Underflow: an arithmetic operation overflowed or underflowed

- Illegal Access: an attempt to read, write, or execute from/to a memory location without proper access privilege (see Chapter 4 for a more complete discussion).

- Load While Input Streaming: a load instruction while register 0 is in input streaming mode.

- Store While Output Streaming: a store instruction while register 0 is in output streaming mode.

### 3.3. Control Flow Instructions

The set of control flow instructions include Jumps and Calls. These instructions replace the Program Counter with a new value, the target address. In all but one case, this is a PC-relative address, and is formed by concatenating two zeros to the bottom of the sign-extended offset and adding this value to the current Program Counter<sup>1</sup>.

There are four conditional jumps associated with the two condition FIFOs: "Jump True" and "Jump False" for each of the integer and floating conditions. Conditional Jumps "consume" a condition bit generated by a relational operation. Valid programs must guarantee that exactly one instruction containing a relational operation is executed for each conditional instruction.

There are eight conditional jumps associated with the streaming facility of the machine (see below); these support jumps on the on "stream count not zero" for each of the input and output streams.

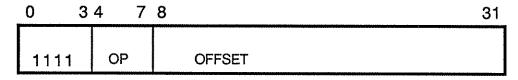

There are two call instructions: Call and ECall. Call simply stores the current PC in register 4 and jumps to the specified destination. ECall performs the function of a "supervisor call", and will be discussed in detail in Chapter 4. The format of control instructions is:

<sup>&</sup>lt;sup>1</sup>The exception is ECall, whose target address is determined indirectly from the PC-relative address described above.

| _ | 0 3  | 4 7 | 8      | 31 |

|---|------|-----|--------|----|

|   |      |     |        |    |

|   | 1111 | OP  | OFFSET |    |

The opcode may specify one of 15 operations:

| Jump   | the basic unconditional jump.                                      |

|--------|--------------------------------------------------------------------|

| JumplT | jumps only if the Integer condition bit is True.                   |

| JumplF | jumps only if the Integer condition bit is False.                  |

| JumpFT | jumps only if the Floating condition bit is True.                  |

| JumpFF | jumps only if the Floating condition bit is False.                 |

| JNI r0 | "Jump on Stream Count Not Zero; Integer Input FIFO 0".             |

| JNI r1 | "Jump on Stream Count Not Zero; Integer Input FIFO 1".             |

| JNO r0 | "Jump on Stream Count Not Zero; Integer Output FIFO 0".            |

| JNO r1 | "Jump on Stream Count Not Zero; Integer Output FIFO 1".            |

| JNI fO | "Jump on Stream Count Not Zero; Floating Input FIFO 0".            |

| JNI f1 | "Jump on Stream Count Not Zero; Floating Input FIFO 1".            |

| JNO f0 | "Jump on Stream Count Not Zero; Floating Output FIFO 0".           |

| JNO f1 | "Jump on Stream Count Not Zero; Floating Output FIFO 1".           |

| Call   | Store PC of the next instruction in r4; jump to specified address. |

| ECall  | Entry Call; see below                                              |

Note that there are 15 operations in this class; 1111 is not a valid control flow opcode. In particular, an instruction that is all ones will trap as an undefined instruction!

ECall provides the functionality of "supervisor call" in other architectures; it has three effects:

- (1) it changes the protection table pointer to that contained in the entry page (note, the map table pointer is not changed),

- (2) it jumps indirectly through the specified PC-relative location, and

- (3) it saves the prior protection table pointer and program counter in a special protected stack area.

The rationale for each of these actions will become clearer in Chapter 4. Note, however, that the address specified in by the PC-relative target address must be that of an "Entry Page", and that the task executing the ECall must have "call rights" to this page.

Three instructions that affect control flow are encoded among the "special" instructions since they do not need to specify a PC-relative address (see section 3.5 for the format of special instructions). Nonetheless, we will discuss them here; they are Jumpl (Jump Indirect), Call (Call Indirect) and EReturn (Return from ECall).

Jump Indirect. An unconditional jump that gets its target address from the register named in the R1

field. This instruction can be used for "case table" jumps, to branch more than 2\*\*24 instructions, and to return from procedure calls.

Calll

Call Indirect stores the current PC in register 4 and gets its target address from the register named in the R1 field.

EReturn

Entry Return. This is the complementary instruction to ECall; it restores the protection table pointer and PC from the protected stack.

### 3.3.1. Exceptions

The following exceptions may be raised as the result of a control flow instruction:

- Condition Unset: A JumpIT(JumpFT) or JumpIF(JumpFF) instruction is being executed, and the condition bit has not been set (and is not in the process of being set) by a previous relational operator.

- Protection Violation: An attempt was made to transfer control to a page without proper access privileges (see Chapter 4 for a more complete discussion).

- Page Fault: In a virtual memory system, an attempt to execute from a virtual address that does not exist in physical memory.

### 3.4. Floating Point Instructions

The floating point instructions are quite similar to the integer/logical instructions. Their general computation is:

R0 := (R1 op1 R2) op2 R3

Notice, however, that literals cannot be specified; only register operands are permitted -- these are always the "floating registers". The instruction format is:

| 0 | 2  | 3 | 4   | 7 | 8 1 | 1 | 12 | 16 | 17 | 21 | 22 | 26 | 27 | 31 |

|---|----|---|-----|---|-----|---|----|----|----|----|----|----|----|----|

|   |    |   |     |   |     | Τ |    |    |    |    |    |    |    |    |

| 1 | 10 | Р | OP: | 1 | OP2 |   | R  | 0  | R  | 1  | R  | 2  | R  | 3  |

The "p" bit specifies if the instruction's operands are single-precision (= 0) or double-precision (= 1). These values are expressed in IEEE floating point standard format. Pairs of registers are used when double-precision is specified. In such cases, even/odd pairs are specified. For example, both f4 and f5 specify the value (f4 catenate

f5). When either register f0 or f1 is specified in a register read, the corresponding FIFO has two word values read from it and catenated to form a 64-bit value. The first word read is on the most significant end (i.e., the "left").

The op1 and op2 fields are encoded identically. They may specify any of the following 15 operations:

| +        | addition                                        |

|----------|-------------------------------------------------|

| -        | subtraction                                     |

| - 1      | reverse subtraction                             |

| *        | multiplication                                  |

| /        | division                                        |

| /'       | reverse division                                |

| <b>6</b> | unary minus (negates its right operand)         |

| G *      | reverse unary minus (negates it's left operand) |

| nop      | no operation; returns its left operand          |

| nop'     | no operation; returns its right operand         |

| =        | equal                                           |

| <=       | less than or equal                              |

| < .      | less than                                       |

| >        | greater than                                    |

| >=       | greater than or equal                           |

|          |                                                 |

Note that, unlike the integer instructions, there are four monadic operations in the floating point set -- this is because there are no literals, and hence the monadic operations cannot be synthesized.

The last five operations are the relationals. They produce their left operand as a result. They also produce a boolean value. If two relationals exist in the same instruction, their boolean values are or'd together and written to the conditional bit. Otherwise, the single boolean value sets the condition bit. If the boolean result is False, then the instruction's register write and exception conditions are nullified. Software must guarantee that exactly one instruction with relational operations is specified before a conditional jump.

### 3.4.1. Exceptions

The following arithmetic conditions result in exceptions unless masked off in the PCW:

- Overflow/Underflow: as per integer instructions.

- Divide by 0: as per integer instructions.

- Condition FIFO overflow: As per the integer instructions.

Note that input/output FIFO empty/full are not exception conditions for the floating point instructions as they were for the integer and load/store instructions. This allows the integer and floating point units to proceed asynchronously preparing/consuming

addresses and data -- but does require a more global detection of erroneous (deadlocked) programs.

### 3.5. Special Instructions

Only a few types of instructions are encoded in this category. Each type will be discussed separately, however the common format for these instructions is:

| 0   | 3 | 4  | 9 | 101 | 112 | 16 | 17 | 21 | 22 | 26 | 27 | 31 |

|-----|---|----|---|-----|-----|----|----|----|----|----|----|----|

|     |   |    |   |     |     |    |    |    |    |    |    |    |

| 111 | 0 | OP |   | RL  | RO  |    | R  | 1  | RI | _2 | RL | .3 |

### 3.5.1. Streaming

The WM computer architecture supports a feature called "streaming". Streaming is a method of loading and storing structured data elements without having to do explicit address computations. It assumes a vector of data elements are present, or are to be created, in memory, and that they are a constant stride (number of bytes) apart from each other. Stream instructions are used to read/write such vectors from/to FIFOs.

There are 14 instructions that initiate streaming operations. These are analogous to the 14 types of loads and stores. They may specify data as doublewords, floating, words, halfwords (zero- or sign-extended/arithmetically checked), or bytes (zero- or sign-extended/arithmetically checked). The operands specify a base address (R1), a count (RL2), a stride<sup>1</sup> (RL3), and which FIFO to use (0 or 1); this last parameter is taken as the least significant bit of the R0 field.

Finally, there are five instructions to stop streaming operations. These instructions stop input or output streaming and flush the relevant FIFOs.

To summarize the operations, they are:

| SinD  | Stream In Doublewords (to the floating execution unit)            |

|-------|-------------------------------------------------------------------|

| SinF  | Stream in Floating (to the floating execution unit)               |

| SinW  | Stream In Words (to the integer execution unit)                   |

| SinH  | Stream In Halfwords (to the integer execution                     |

| SinB  | Stream In Bytes (to the integer execution unit)                   |

| SinHX | Stream In Halfwords sign-eXtended (to the integer execution unit) |

| SinBX | Stream In Bytes sign-eXtended (to the integer execution unit)     |

| SoutD | Stream Out Doublewords (from the floating execution unit)         |

| SoutF | Stream Out Floating (from the floating execution unit)            |

| SoutW | Stream Out Words (from the integer execution unit)                |

|       |                                                                   |

<sup>&</sup>lt;sup>1</sup> In bytes.

| SoutH   | Stream Out Halfwords (from the integer execution unit)            |

|---------|-------------------------------------------------------------------|

| SoutB   | Stream Out Bytes (from the integer execution unit)                |

| SoutHA  | Stream Out Halfwords with Arithmetic range checking               |

| SoutBA  | Stream Out Bytes with Arithmetic range checking                   |

| StopAll | Stop all Streaming operations                                     |

| StopII  | Stop Integer Input Streaming operations on FIFO specified by R0   |

| StopiO  | Stop Integer Output Streaming operations on FIFO specified by R0  |

| StopFI  | Stop Floating Input Streaming operations on FIFO specified by R0  |

| StopFO  | Stop Floating Output Streaming operations on FIFO specified by R0 |

An example of a valid assembly instruction is:

```

SinW r1, r9, 22, 16 -- FIFO, address, count, stride

```

This instruction would cause a vector of 22 words, whose base address is contained in r9, and which are displaced 16 bytes from each other, to be streamed to FIFO "r1" in the IEU.

A stop instruction applied to an output FIFO will complete pending memory writes (where data is available), reset the stream count and restore the FIFO to non-streaming mode. A stop instruction applied to an input FIFO will take the counterpart action, discarding all data currently in the FIFO.

Streaming instructions may cause Page Fault exceptions. If made during a memory read, the exception is not raised until an attempt to read register 0 or 1 unsuccessfully. If made during a write of register 0 or 1 (to be written into memory), the exception is raised immediately.

All start streaming instructions require implicit synchronization with the Integer Execution Unit. Stop integer streaming instructions also require implicit synchronization with the IEU while stop floating streaming instructions require synchronization with both execution units.

### 3.5.2. State Manipulation

There are a few instructions to provide access to special state and to help save and restore state efficiently.

| LOADM   | R1, | L2, | L3 |

|---------|-----|-----|----|

| FLOADM  | R1, | L2, | L3 |

| STOREM  | R1, | L2, | L3 |

| FSTOREM | R1, | L2, | L3 |

These instructions load and store a series of registers, from register number L2 to register number L3, with L3 guaranteed by software to be a greater register number than L2. Note separate instructions specify IEU and FEU registers. The RL field is ignored by this instruction and literals are always specified by RL2 and RL3. The storage location involved is specified by R1.

LOADFIFO R1 STOREFIFO R1 FLOADFIFO R1 FSTOREFIFO R1

These instructions load and store the FIFO state from/to the address specified in R1. The amount and format of this information is implementation dependent. Again, separate instructions specify IEU and FEU FIFOs.

The above floating load and store instructions require implicit synchronization with both execution units while their integer counterparts only require synchronization with the IEU.

LOADCTX R1 STORCTX SWAPCTX R1 SWAPLT

These instructions perform context load, store, and swap. LOADCTX restores context from the a block of storage whose address is specified in R1. STORCTX stores the current context at a known location for the current task. SWAPCTX combines the previous two operations. SWAPLT, "swap to last task", is identical to SWAPCTX, except that the address of the new TCB is implicitly the "last TCP pointer" (see Chapter 4).

The LOADCTX and SWAPCTX instructions verify that R1 contains the address of a "TCB page" (see Chapter 4). Every piece of vital CPU state is loaded or stored by these instructions. Consequently, if context is saved and later restored, then the next instruction is executed as if no context save/restore had occurred.

All context switching instructions require implicit synchronization of the entire machine (see the SYNCH instruction in section 3.5.6).

#### 3.5.3. Type Conversion

Instructions exist to convert between the three internal numeric data types. The opcodes and their corresponding instructions are:

CVTIF R0 := R1

CVTID R0 := R1

CVTFI R0 := R1

CVTFD R0 := R1

CVTDI R0 := R1

CVTDF R0 := R1

There interpretation is the obvious one, ConVerT from Integer, Floating, or Double, to another data type. Note that these instructions reference one register in the integer

execution unit and one in the floating execution unit as appropriate. In addition, two instructions are included for transferring data unmodified between the two units:

These have the obvious "Transfer from Integer to Floating", and "Transfer from Floating to Integer" interpretations<sup>1</sup>.

Note: although in general the IEU and FEU operate asynchronously, they are synchronized for the convert and transfer instructions -- that is, the basic sequential semantics of program execution are preserved.

### 3.5.4. Constraint Checking

There are two instructions for checking arithmetic constraints:

```

ASSERT (R1 >= RL2) <= RL3

FASSERT (R1 >= R2) <= R3

```

The ASSERT and FASSERT instructions determine if a value is within certain bounds. If it is not, a hardware RANGE trap is generated. Unlike the integer and floating point relationals, the two boolean values are ANDed together by these instructions and no condition code is enqueued. Note that it is possible to check only a single bound, for example,

```

ASSERT (r8 \ge r8) \le 13 to check only the upper bound, and ASSERT (r8 \ge 13) \le r8 to check only the lower bound.

```

#### 3.5.5. Field Manipulation

Fields can be moved within a word with the following instructions:

```

FLDMOV R0 := R1, RL2, RL3 -- FieLD MOVe

FLDMOVX R0 := R1, RL2, RL3 -- FieLD MOVe (sign-eXtended)

```

These may be thought of as being implemented using more primitive arithmetic and logical shifts<sup>2</sup>:

```

FLDMOV R0 := (R1 IsI RL2) Isr RL3

FLDMOVX R0 := (R1 IsI RL2) asr RL3

```

They may be used to perform several functions, including:

<sup>&</sup>lt;sup>1</sup> Aside from the obvious "bit hacking" these instructions allow, they may also be used to get more streams to one of the executions units if the other has them free.

<sup>&</sup>lt;sup>2</sup> "Isr" is "logical shift right"; "Isl" is logical shift left; "asr" is arithmetic shift right.

field extraction

an arbitrary signed or unsigned field may be taken out of a word and placed in an aligned, signed or unsigned, format. For example, "FLDMOVX r5 := r7,8,24" takes a signed byte from byte 1 of register 7 and transforms it into a signed 32-bit integer in register 5.

basic shifts

Isl, Isr, and asr are the basic functions within these instructions. By using the appropriate zero literal, each can be synthesized. For example, "FLDMOV r5 := r7,0,7" performs a 7-bit logical shift right. Since asl is provided in the basic instruction set, all basic shifts are represented.

Shift amounts of greater than 32 perform the same function as a shift by 32, namely the clearing (or setting if asr of a negative number) of the result. Field insert is not explicitly supported in the instruction set since it can be expressed in three instructions with the existing instruction set.

Finally, the "find first (different) bit" is provided:

FFB R0 := R1

This instruction finds the first bit that is different from the sign bit, starting from the left. It returns the bit number of the bit found. If all the bits in the 32-bit word are the same, then the value 0 is returned. Taking this instruction as a function and applying it to some shorter examples, we get:

3 = FFB(000101001)

1 = FFB(010000010)

4 = FFB(111100101)

0 = FFB(1111111111)

#### 3.5.6 Pipeline Synchronization

The instruction

**SYNCH**

causes the processor to synchronize the IFU, IEU and FEU. In effect, it will inhibit instruction dispatch until a consistent, "as though the instructions were really executed sequentially" state is reached. See section E.5.6.

Certain special instructions, such as those performing context switching and type conversion, require implicit synchronization of the machine. These instructions can be thought of as always having an implied SYNCH instruction preceding them.

Other special instructions, as noted preciously, require implicit synchronization of only one of the execution units with the IFU. Synchronization, in these cases, can be

| accomplished by inhibiting instruction dispatch to the appropriate execution unit until the contents of that unit's instruction buffer have been consumed. |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                            |

|                                                                                                                                                            |

|                                                                                                                                                            |

|                                                                                                                                                            |

|                                                                                                                                                            |

|                                                                                                                                                            |

|                                                                                                                                                            |

|                                                                                                                                                            |

|                                                                                                                                                            |

|                                                                                                                                                            |

|                                                                                                                                                            |

|                                                                                                                                                            |

|                                                                                                                                                            |

## Chapter 4. Task, Program, and System Framework

This chapter is concerned with that collection of architectural issues that support an "operating system" -- issues such as memory mapping, protection, control of input-output devices, interrupts and traps, system calls, and the hardware notion of "process" or "task".

WM approaches these issues in a manner that allows many of the functions normally associated with an operating system to be safely delegated to applications programs, thus eliminating unnecessary overhead from these functions and, perhaps more importantly, eliminating inefficiencies due to circumlocutions when the operating system provides the wrong facility. It is possible, for example, for an important data-base application to be safely allocated its own disk; this allows the data-base system to (1) avoid expensive operating system calls for data transfers, and (2) format the disk in a manner appropriate to the application.

The same WM facilities that allow operating system functions to be safely handled by applications, are also powerful structuring tools for building more conventional operating systems. Using the WM facilities it is possible to construct a variety of novel, secure, and highly efficient operating environments -- including an efficient multi-level military security system. At the same time, the WM hardware does not favor one style of operating system over another, and does not impose a performance penalty on simple systems; it is possible to implement a traditional system such as UNIX *very* efficiently.

Before starting into the details, we'll briefly introduce, and hopefully motivate, the concepts to be discussed:

Tasks: As usually defined, a task is a "thread of control". The WM hardware understands the notion of a task, and supports a hardware-defined "task

control block", TCB, to hold the state of the task when it is not executing. There are instructions to save, restore and "swap to" tasks; for purposes of these instructions, tasks are named by the address of their TCBs.

An "interrupt" is essentially a forced context swap; in general, different sources of interrupts may specify different tasks as their "handler tasks".

Domains: A task executes in an addressing domain. The domain consists of a flat, paged address space; each page in this space has two independent properties: (1) address translation information, and (2) typed protection information; these are defined by a "map table" and "protection table" respectively. Pointers to these tables are part of the task state in the TCB. These properties are separated so that, for example, two tasks can share the same address space but have different access to portions of that space.

The concept of a typed protection system is especially powerful. Each page is typed; only instructions appropriate to the type are permitted to reference a page, and the task must have rights appropriate for the instruction. For example, TCB is a type. The instruction to perform a context swap may be executed only on this type of page -- and then only if the task has "swap rights" to that particular page.

Entries: An "entry" is another type of page, and is a generalization of the "trap vector" of some other architectures. An "entry call", ECall, instruction may reference (only) an entry page and requires "call rights"; if executed, it has three effects:

- (1) it changes the protection table pointer to that contained in the entry page (note, the map table pointer is not changed),

- (2) it transfers indirectly through the location specified in the ECall, and

- (3) it saves the prior protection table pointer and program counter in a special protected stack area in the TCB.

ECall provides the functionality of the "supervisor call" or "system call" instruction of other architectures, but does not make a rigid N-level distinction between "user" and "system". Instead, a particular operating system can provide a variety of, possibly nested, entry pages with greater, lesser, or merely different accesses.

The "EReturn" instruction unstacks and restores the protection state and PC of the caller.

Traps are merely ECall's on predefined locations (in "page 0").

**Devices:** A "device" is yet another hardware understood page type, and corresponds to the memory-mapped device registers in many architectures. Device-specific operations are performed by storing bit patterns into these locations (registers). Device status, and sometimes data, is accessed by reading these locations.

A goal of the WM design was minimal operating system overhead in critical applications -- such as accessing sensor data in embedded systems, and interprocess communication in multi-computer complexes. A key to achieving this is the ability of an application program to directly control a device, and do so safely. The ability to map devices into an application's address space provides the mechanism to achieve the goal.

The following sections discuss each of the above items in more detail.

#### 4.1. Task State

Whenever a task is saved or restored, all of its processor state is transferred to or from its hardware-defined Task Control Block. This is an area in memory with room for:

- (1) State visible to the program

- integer and floating point registers.

- Program Counter, PC.

- Program Control Word, PCW.

- Program Status Word, PSW.

- Cycle Counter, CC.

- Last TCB Pointer, LTP.

- Protection Table Pointer, PTP.

- Map Table Pointer, MTP.

- (2) State visible only indirectly by the program

- input/output FIFO state.

- streaming state.

- other implementation-defined state

In general, the amount and description of the state is implementation-dependent. Only the TCB format for the state visible to the program is defined. The size of the hardware TCB is restricted to be 128 words, however. Some of the architecturally-defined state is discussed below.

The PCW and PSW are two architecturally-defined CPU device registers. Implementations may add other registers (e.g., to control hardware diagnostics).

The Program Control Word collects a number of fields whose values affect the execution of a task, such as the bits that enable/disable certain traps. The PCW consists of:

| Bit#  | Meaning                 |

|-------|-------------------------|

|       |                         |

| 0     | Run/Halt (run == 1)     |

| 1     | Interrupts Enabled      |

|       | Exceptions Enabled:     |

| 2     | Assert                  |

| 3     | Integer Divide By Zero  |

| 4     | Floating Divide by Zero |

| 5     | Integer Overflow        |

| 6     | Floating Overflow       |

| 7     | Integer Underflow       |

| 8     | Floating Underflow      |

| 9     | Cycle Counter Overflow  |

| 10    | Raise Address           |

| 11    | Raise Call              |

| 12    | Raise Jump              |

| 13:16 | Priority[0:3]           |

The Program Status Word collects a number of fields that reflect status of the task, such as the condition FIFOs. For example, the PSW could include:

| Bit # | Meaning                       |

|-------|-------------------------------|

|       | M                             |

| 1:3   | Integer Condition FIFO Bits   |

| 4:5   | integer Condition FIFO Depth  |

| 6:8   | Floating Condition FIFO Bits  |

| 9:10  | Floating Condition FIFO Depth |

The Cycle Counter is a 32-bit register that is incremented by one every cycle that the task executes. It may overflow (once every ~200 seconds with a 50ns cycle time), in which case an exception may be raised.

The Last TCB Pointer, LTP, in general points to a TCB. When an interrupt occurs, a forced context swap is performed and the LTP of the *new* task is set to point to the TCB of the task that was running at the time of the interrupt. Thus, in the case of nested interrupts, the LTPs form a chained "stack" of the suspended handlers; the SWAPLT instruction (see Sec. 3.5.2) will resume the previous task.

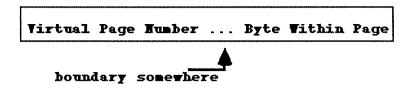

The MTP and PTP are discussed in the next two subsections. Note first, however, that a task's virtual address space is divided into "pages" in the conventional manner. An address is divided into two parts, the virtual page number, and the byte within page address. The boundary between these parts is implementation-dependent, as is the structure of the tables (one-level, two-level, etc.). Pages must, however, be at least 512 bytes.

Assume N bits of virtual page number and 32-N bits that specify the byte within the page. Associated with every virtual page number is a protection table and map table entry, as described below.

#### 4.2. Protection Table

Each task has a Protection Table that defines its memory access rights on a page-by-page basis. The Protection Table Pointer (PTP) in the TCB is either null (zero), or defines the base of this table and virtual address page numbers are used to index into it. If the PTP is null no type or rights checking is performed, otherwise protection is checked as specified below<sup>1</sup>.

A Protection Entry is a byte, with the following format:

| type | rights |  |  |  |

|------|--------|--|--|--|

|      | 1 1 1  |  |  |  |

The first four bits define the page type. This field is interpreted as:

| 0000 | ) Mem  | югу      |     |          |

|------|--------|----------|-----|----------|

| 0001 | TCB    | -        |     |          |

| 0010 | ) Entr | y        |     |          |

| 0011 | Devi   | ce       |     |          |

| 0100 | 0-0111 | reserved | for | hardware |

| 1000 | )-1111 | reserved | for | software |

Only the first four are hardware defined. Accesses to pages with reserved protection types raise a memory protection exception.

An access to "Memory" pages may either be reads, writes, or executes. The rights bits are R, W, and X, and determine if such operations are allowed, or if they result in memory protection exceptions.

Accesses to a TCB page may be reads, writes, or context save/restore/swap; the protection bits are correspondingly, R, W, and S. Note that saving context is not a privileged operation.

<sup>&</sup>lt;sup>1</sup>The PTP may be null because protection is not implemented on a certain model of WM. In addition, however, PTP is null when the processor is first "booted" -- this corresponds to the "most privileged state".

Accesses to an Entry page may be reads, writes, or ECalls; the protection bits are correspondingly, R, W, and C.

Accesses to Device pages may be only reads and writes, and the corresponding rights bits are R and W.

It should be noted that W-rights (write-rights) to TCB and Entry pages are *very* potent rights since they allow changing PTPs; normally these rights would be granted only to the most trusted portion of a system.

## 4.3. Map Table

Each task has a Map Table that defines its virtual-to-physical address translation. The Map Table Pointer (MTP) in the TCB is either null (zero), or defines the base of this table and virtual address page numbers are used to index into it. If the MTP is null, no translation is performed; otherwise translation proceeds as specified below<sup>1</sup>.

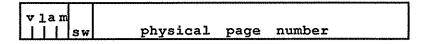

Map table entries have the following format:

and their bits are interpreted as follows:

- 0 Valid this page exists in physical memory

- 1 Locked --this page is locked into memory<sup>2</sup>

- 2 Accessed this page has been read

- 3 Modified this page has been written

- 4:5 Software usable/defined

- 6:31 Physical Page Number 26 bits

The 26-bit physical page number is catenated with the Byte Within Page field to form the physical address. This limits the physical memory (without bank-switching) to an address space of 26 plus size(Byte Within Page) bits. This can be more than 32 bits.

Note: the WM architecture does not define the number of levels in the structure of the Map or Protection tables.