# Register Allocation and Phase Interactions in Retargetable Optimizing Compilers

# A Dissertation

Presented to

the Faculty of the School of Engineering and Applied Science at the

University of Virginia

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy (Computer Science)

by

Manuel Enrique Benitez

© Copyright by

Manuel Enrique Benitez

All Rights Reserved

May 1994

# **ABSTRACT**

Retargetability is increasingly becoming a necessary property in optimizing compilers. Because register allocation is essential to high-quality code generation, compilers whose register allocators assume a particular register file organization sacrifice retargetability. Also, the strategies used to allocate registers on optimizing compilers that incorporate many code improvement phases tend to over-commit register resources and expect the register assigner to compensate for poor allocation decisions. State-of-the-art register assignment techniques can compensate to a point, but invariably emit poor code when confronted with small register sets or very high register demand. The research presented here will show that:

- when simplicity, retargetability, code quality and execution time are considered, a simple register allocation strategy that allocates registers on a first-come, first-served basis while preventing the code improvement phases from over-committing the registers is the most effective of the various retargetable register allocation techniques evaluated,

- phase iteration, a technique that re-attempts code improvements as additional opportunities to apply them arise, is an effective way of reducing interactions between the tasks performed by an optimizing compiler and simplify the ordering of these tasks,

- it is possible to integrate the code improvement and register allocation tasks performed by an

optimizing compiler in order to improve the quality of the code produced by the compiler and

increase its retargetability, and

- machine-level global code improvement techniques allow retargetable optimizing compilers to

produce code whose quality meets or exceeds the quality of the code produced by traditional

production compilers.

This dissertation also includes a detailed description of the experimental frameworks and the register deprivation measurement techniques that were developed to support the design, implementation and evaluation of the machine-level register allocation and code improvements algorithms presented here.

# APPROVAL SHEET

This dissertation is submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy (Computer Science)

This dissertation has been read and approved by the Examining Committee:

| Dissertation Advisor   | · |

|------------------------|---|

| ∫ Dissertation Advisor |   |

| MA                     |   |

| Committee Chairman     |   |

| hh & Well              |   |

|                        |   |

| Bam W. almos           |   |

| 000                    |   |

| John Might.            |   |

|                        |   |

ean, School of Engineering and Applied Science

Accepted for the School of Engineering and Applied Science:

# **ACKNOWLEDGMENTS**

I would like to thank everyone who has, in some way, contributed to this work. This work would not have been possible without the support, guidance and encouragement of many.

First and foremost, I would like to thank my advisor, Jack Davidson, for the guidance and inspiration that he so willingly provided throughout this long endeavor. I am indebted to his insight and his expertise.

The members of my examining committee, Jack Davidson, William Wulf, Andrew Grimshaw, Barry Johnson and John Knight, provided many helpful comments and devoted much time to ensure that this work measures up to the standards of the University of Virginia and the scientific community. Robert Cook and Joseph Kent, although not part of my committee, also made valuable contributions.

Many of my fellow students deserve more than just the passing mention that they will get here. Mark Bailey provided many useful suggestions, never tired of reading my tired prose and pointed out many of the weaknesses in my logic. David Whalley's work with *ease* and some of his machine descriptions provided me with much needed building blocks. Ann Holler provided much needed encouragement and convinced me to make the most of my limited time as a graduate student. Sanjay Jinturkar, Bruce Childers and Michael Alexander also contributed in many ways.

This work would not have been possible without the help of the current and erstwhile staff at the department of computer science: Mark Smith, Gina Bull, Ray Lubinsky and Ann Bailey.

I would also like to thank my running partners, Jim French, Jeff Salowe and Bob Downer for going the extra mile(s) with me and making my last year here a memorable one.

I would also like to acknowledge the financial support of the research presented in this dissertation provided by the National Science Foundation's Grant number CCR-9214904.

Finally, I wish to thank my family for all their love and encouragement. It is to them that I dedicate this dissertation.

To my Mother

Make it as simple as possible—and no simpler.

-Nicklaus Wirth

# TABLE OF CONTENTS

| 1 | INTRODUCTION                                                 |

|---|--------------------------------------------------------------|

|   | 1.1 Retargetable optimizing compilers                        |

|   | 1.1.1 What is retargetability?                               |

|   | 1.1.2 Why is retargetability important?                      |

|   | 1.1.3 Intermediate representations                           |

|   | 1.1.4 Register allocation                                    |

|   | 1.2 The scope of this investigation                          |

|   | 1.2.1 Architectures                                          |

|   | 1.2.2 Code improvement transformations                       |

|   | 1.2.3 Register allocation                                    |

|   | 1.3 Structure                                                |

| 2 | CODE IMPROVEMENTS                                            |

|   | 2.1 The motivation for comprehensive code improvement suites |

|   | 2.2 Code improvement phases                                  |

|   | 2.3 Phase interactions                                       |

|   | 2.4 Organizational structure                                 |

|   | 2.5 Related work                                             |

|   | 2.5.1 Amsterdam Compiler Kit                                 |

|   | 2.5.2 PO                                                     |

|   | 2.5.3 HP Precision Architecture                              |

|   | 2.5.4 VPO                                                    |

|   | 2.5.5 GCC                                                    |

|   | 2.5.6 Marion                                                 |

|   | 2.6 Summary                                                  |

| 3 | REGISTER ALLOCATION                                          |

|   | 3.1 The allocation process                                   |

|   | 3.2 Retargetable register allocation                         |

|   | 3.2.1 Very few registers                                     |

|   | 3.2.2 Few registers                                          |

|   | 3.2.3 Many registers                                         |

|   | 3.3 Basic allocation strategies                              |

|   | 3.3.1 Local-scope register allocation                        |

|   | 3.3.1.1 Minimal cost path                                    |

|   | 3.3.1.2 Page replacement                                     |

|   | 3.3.1.3 Use counts                     |

|---|----------------------------------------|

|   | 3.3.2 Global-scope register allocation |

|   | 3.3.2.1 Packing                        |

|   | 3.3.2.2 Coloring                       |

|   | 3.3.2.3 Probabilistic                  |

|   | 3.4 Related work                       |

|   | 3.4.1 SL/1                             |

|   | 3.4.2 U-code                           |

|   | 3.4.3 PQCC                             |

|   | 3.4.4 PL.8                             |

|   | 3.4.5 UOPT                             |

|   | 3.4.6 Split allocation                 |

|   | 3.5 Summary                            |

| 4 | REGISTER DEPRIVATION MEASUREMENTS      |

|   | 4.1 Trials and probes                  |

|   | 4.2 Comparative measurements           |

|   | 4.3 Benchmark suite                    |

|   | 4.4 Applications                       |

|   | 4.4.1 System performance measurements  |

|   | 4.4.2 Phase performance measurements   |

|   | 4.4.3 Benchmark suite evaluation       |

|   | 4.4.4 Architecture design              |

|   | 4.4.5 Validation suite enhancement     |

|   | 4.5 Implementation                     |

|   | 4.5.1 Measurements                     |

|   | 4.5.2 Registers                        |

|   | 4.5.3 Calling convention               |

|   | 4.5.4 Probes                           |

|   | 4.5.5 Library Functions                |

|   | 4.6 Summary                            |

| _ |                                        |

| 5 | EXPERIMENTAL FRAMEWORK                 |

|   | 5.1 Overview                           |

|   | 5.2 Global-scope instruction selection |

|   | 5.3 Local register assignment          |

|   | 5.3.1 Register description             |

|   | 5.3.2 Constrained references           |

|   | 5.3.3 Evaluation order determination   |

|   | 5.4 Variable promotion                   |

|---|------------------------------------------|

|   | 5.4.1 Local interference graph           |

|   | 5.4.2 Live range reduction               |

|   | 5.4.3 Coloring                           |

|   | 5.5 Loop optimizations                   |

|   | 5.5.1 Loop-invariant code motion         |

|   | 5.5.2 Loop strength reduction            |

|   | 5.5.3 Recurrence optimization            |

|   | 5.5.4 Induction variable elimination     |

|   | 5.6 Architecture-dependent optimizations |

|   | 5.6.1 Instruction scheduling             |

|   | 5.6.2 Filling branch delay slots         |

|   | 5.7 Summary                              |

| 6 | IMPROVING THE LOW-LEVEL FRAMEWORK 138    |

|   | 6.1 Code improvements                    |

|   | 6.1.1 Common subexpression elimination   |

|   | 6.1.2 Loop-invariant code motion         |

|   | 6.2 Register allocation                  |

|   | 6.2.1 Free-for-all                       |

|   | 6.2.2 Round-robin                        |

|   | 6.2.3 Bounded register                   |

|   | 6.2.4 Comparisons                        |

|   | 6.3 Unified approach                     |

|   | 6.3.1 Overview                           |

|   | 6.3.2 Implementation                     |

|   | 6.3.3 Results                            |

|   | 6.3.4 Comparisons                        |

|   | 6.4 Summary                              |

| 7 | CONCLUSIONS                              |

| Ą | REGISTER TRANSFER NOTATION               |

| R | RIRI IOGRAPHY                            |

# TABLE OF FIGURES

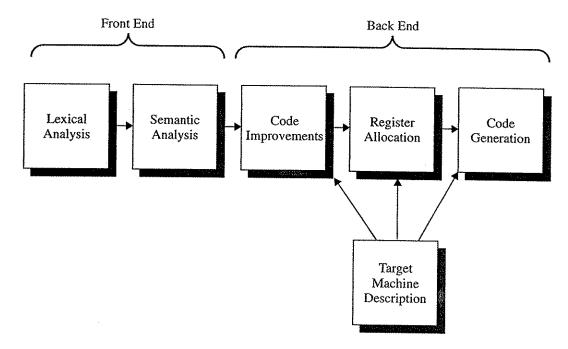

| Figure 1:  | The front and back ends of an optimizing compiler                           | 14 |

|------------|-----------------------------------------------------------------------------|----|

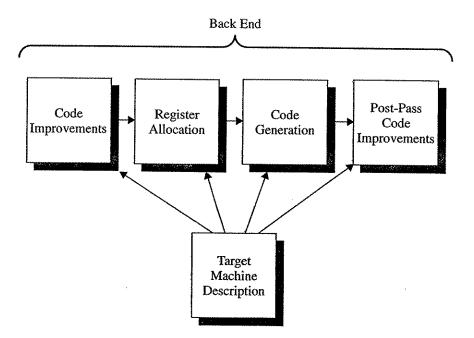

| Figure 2:  | Back-end with post-pass code improvements                                   | 1: |

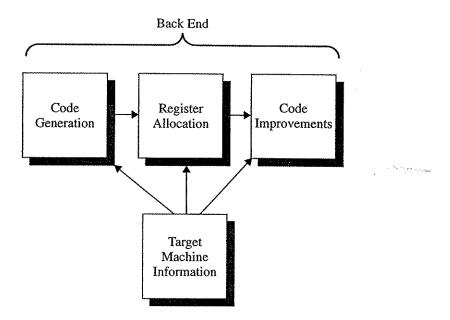

| Figure 3:  | Structure of a back-end that operates exclusively on machine code           | 16 |

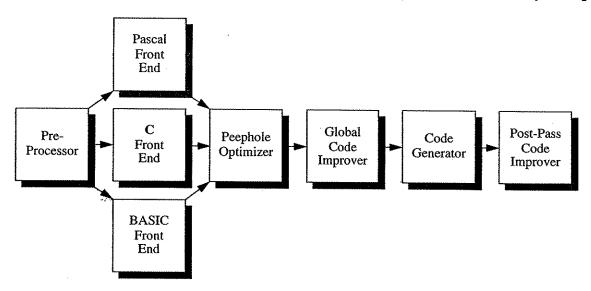

| Figure 4:  | Structure of a compiler produced with the Amsterdam Compiler Kit            | 1′ |

| Figure 5:  | The structure of PO                                                         | 18 |

| Figure 6:  | The structure of <i>vpo</i>                                                 | 23 |

| Figure 7:  | The retargetable allocation process                                         | 25 |

| Figure 8:  | A minimal cost path graph                                                   | 31 |

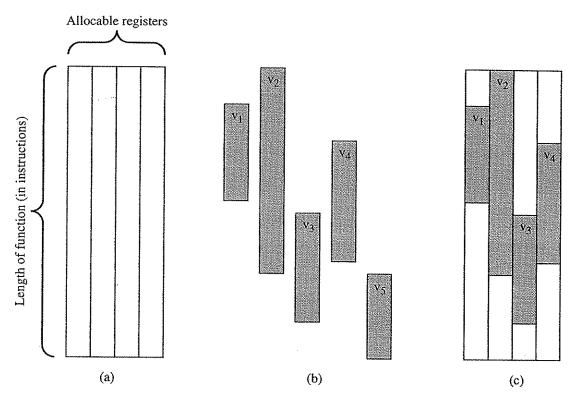

| Figure 9:  | Register allocation via packing                                             | 33 |

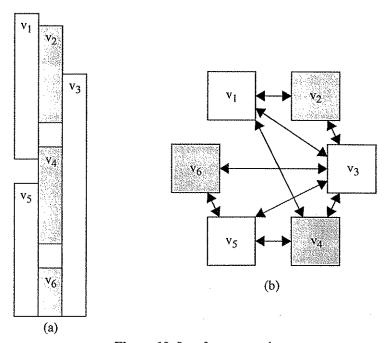

| Figure 10: | Interference graph                                                          | 34 |

| Figure 11: | $\Delta$ -probabilities                                                     | 35 |

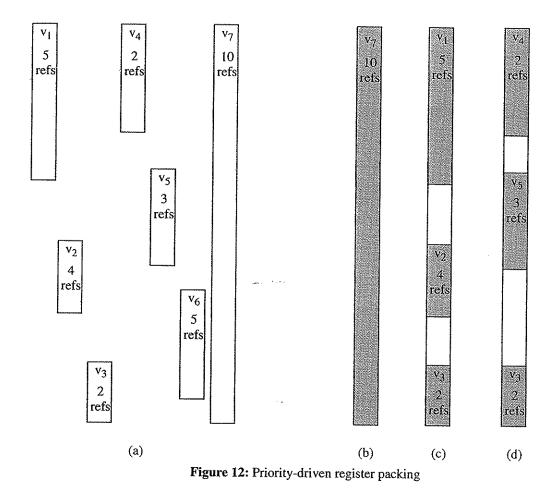

| Figure 12: | Priority-driven register packing                                            | 39 |

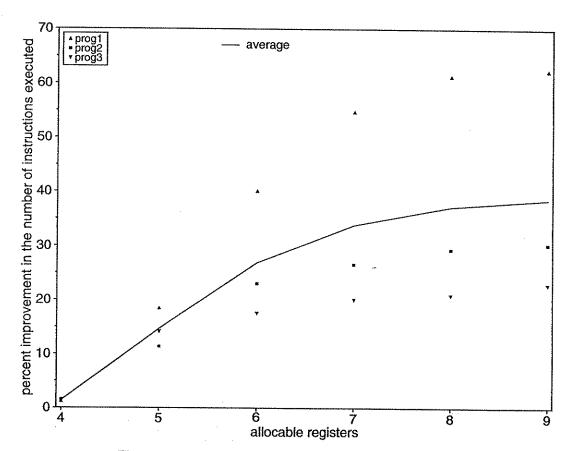

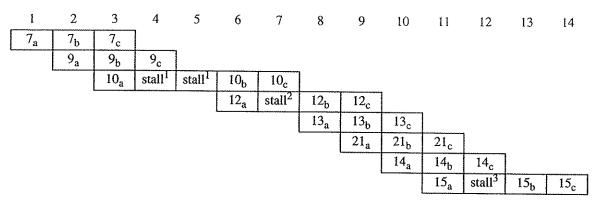

| Figure 13: | Instruction execution counts from a register deprivation trial              | 46 |

| Figure 14: | Instruction execution counts from a register deprivation base trial         | 46 |

| Figure 15: | Results of comparing two register deprivation trials                        | 47 |

| Figure 16: | Results of a sample register deprivation experiment                         | 48 |

| Figure 17: | Benchmark suite                                                             | 49 |

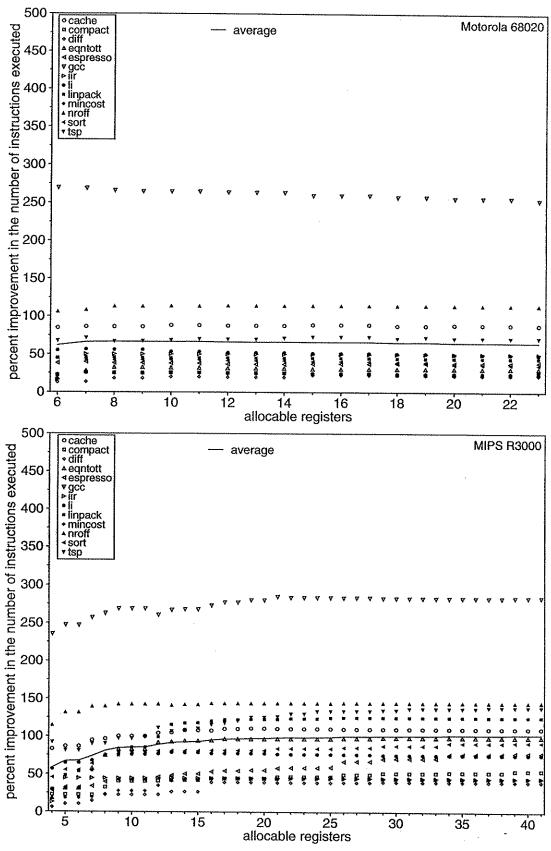

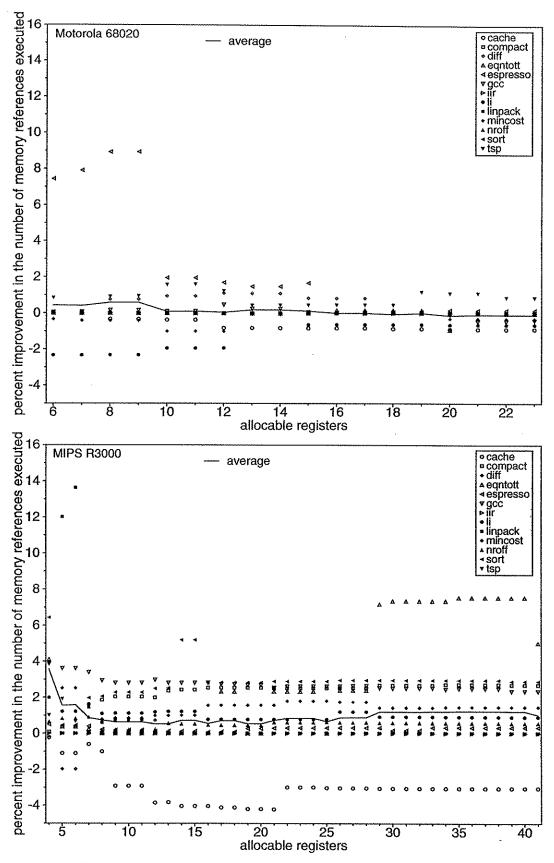

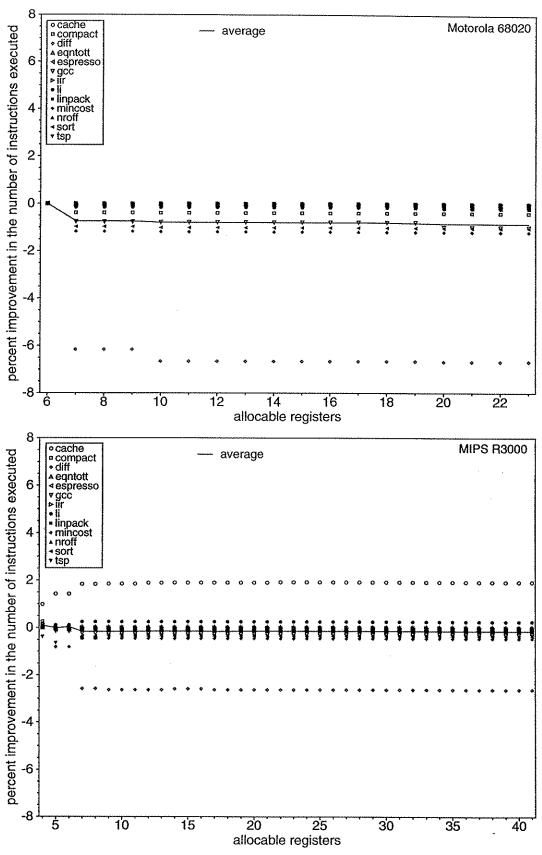

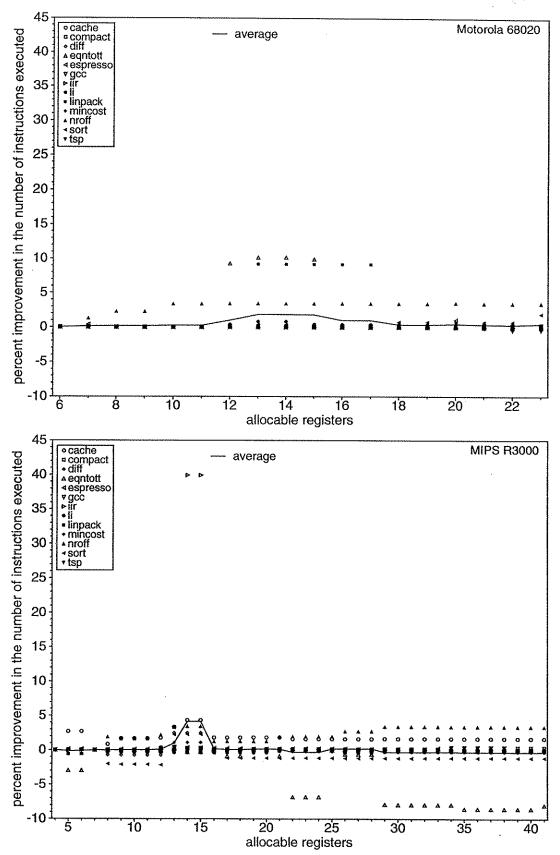

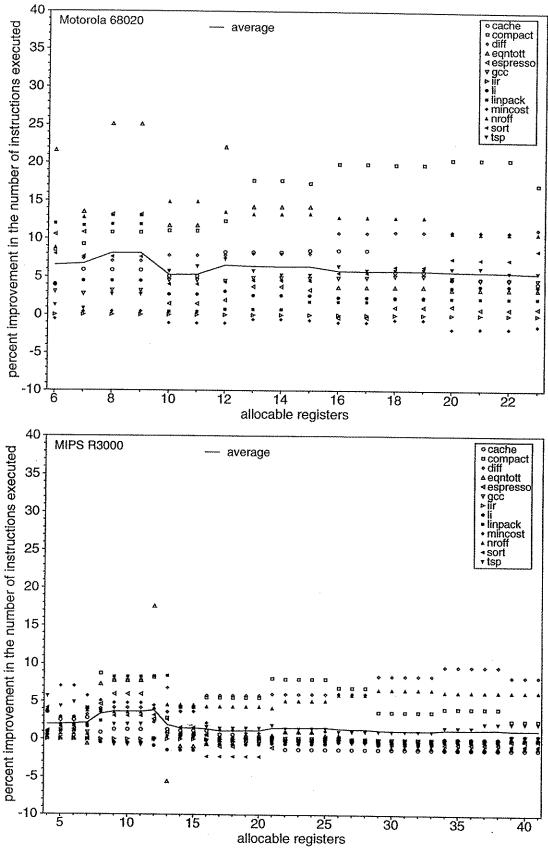

| Figure 18: | System performance results (instruction counts)                             | 50 |

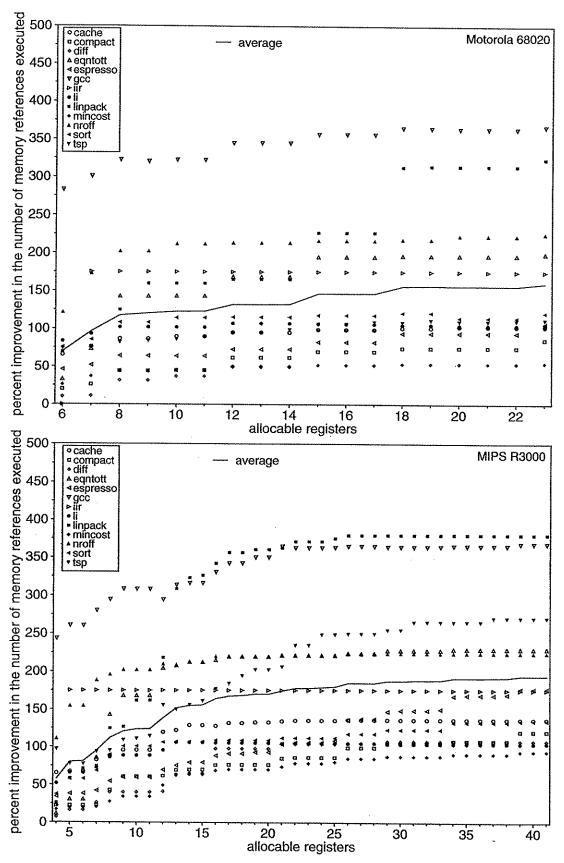

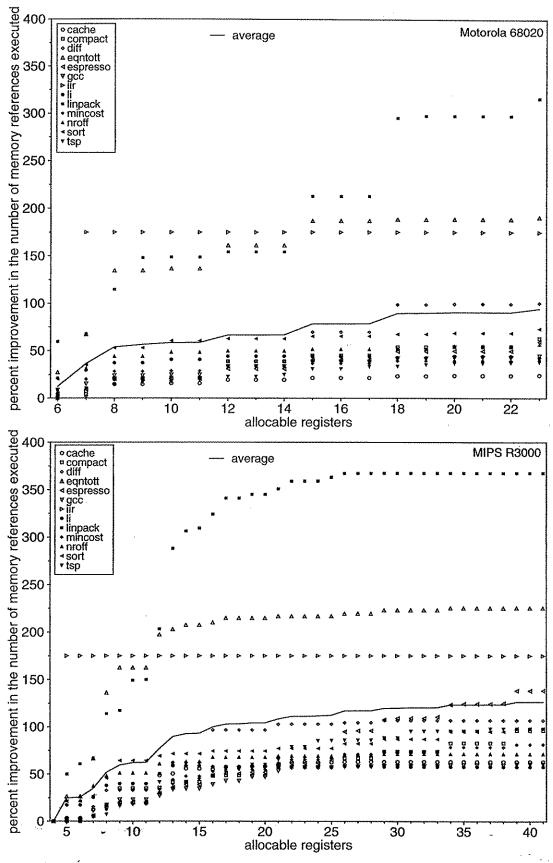

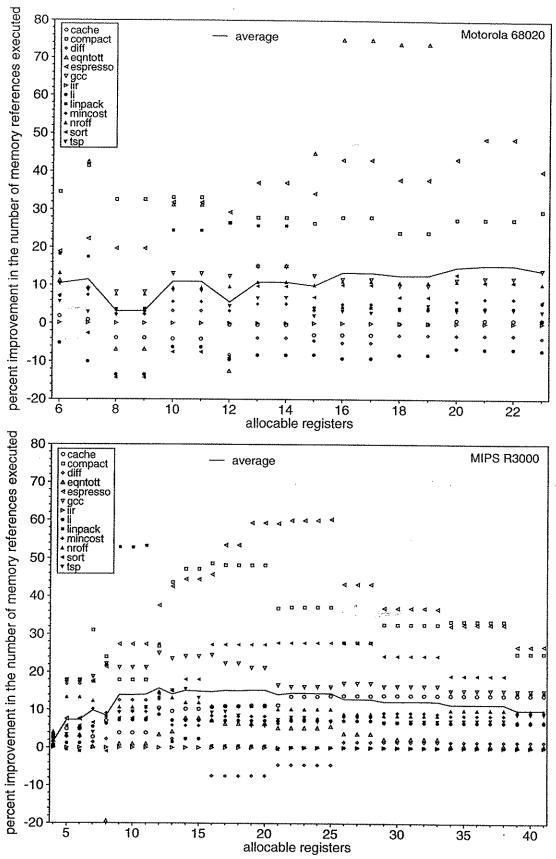

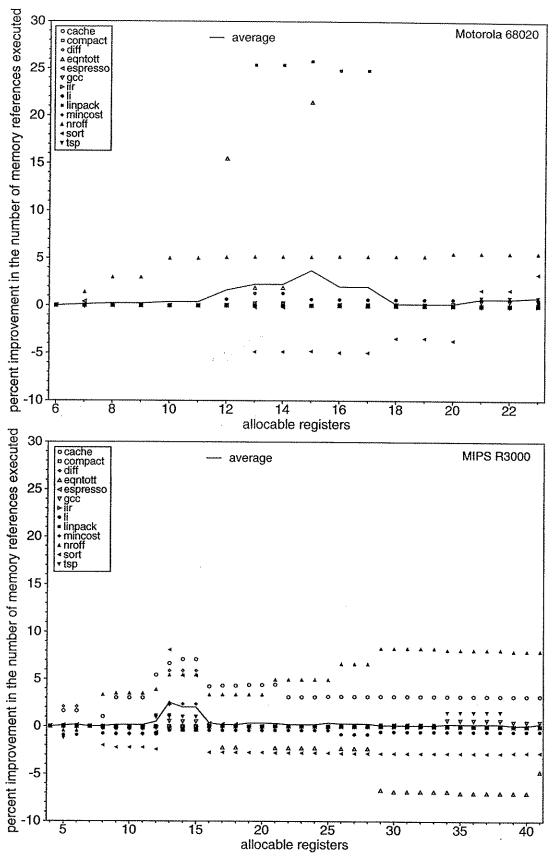

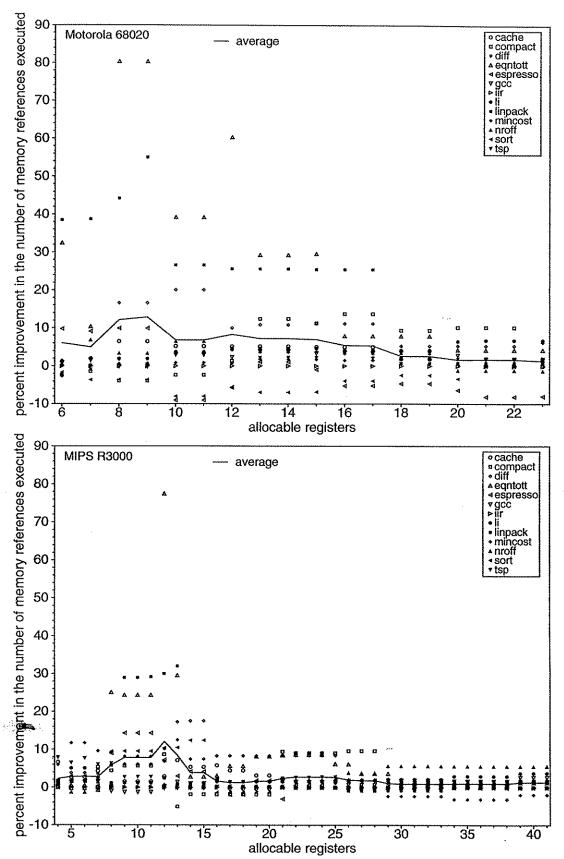

| Figure 19: | System performance results (memory reference counts)                        | 52 |

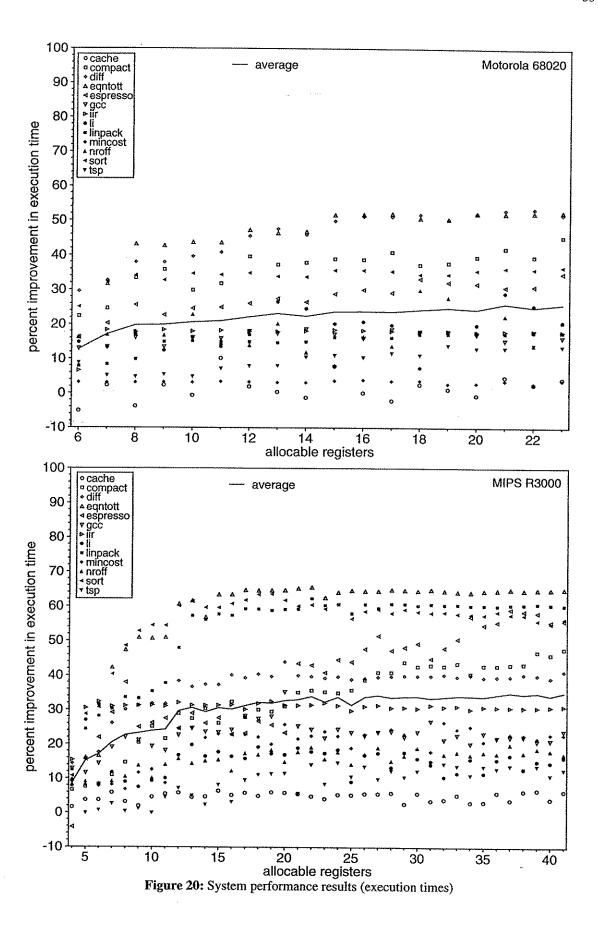

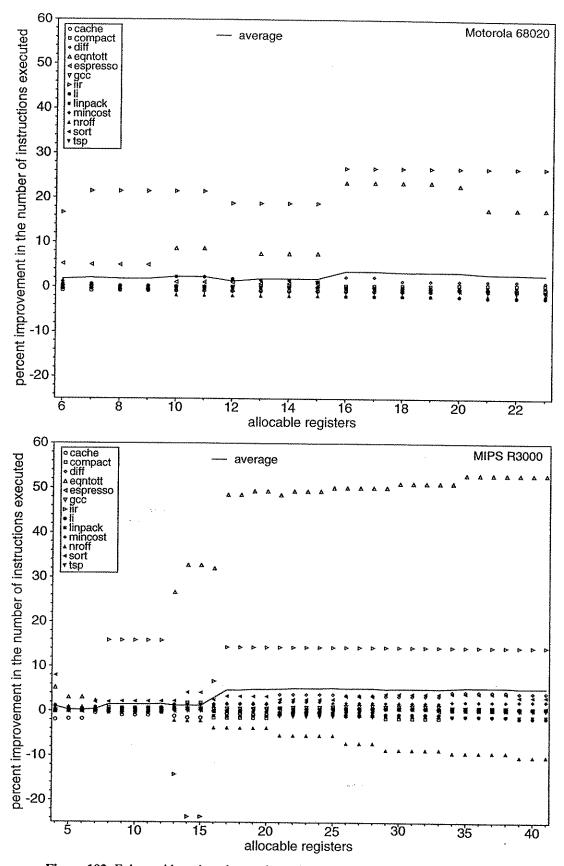

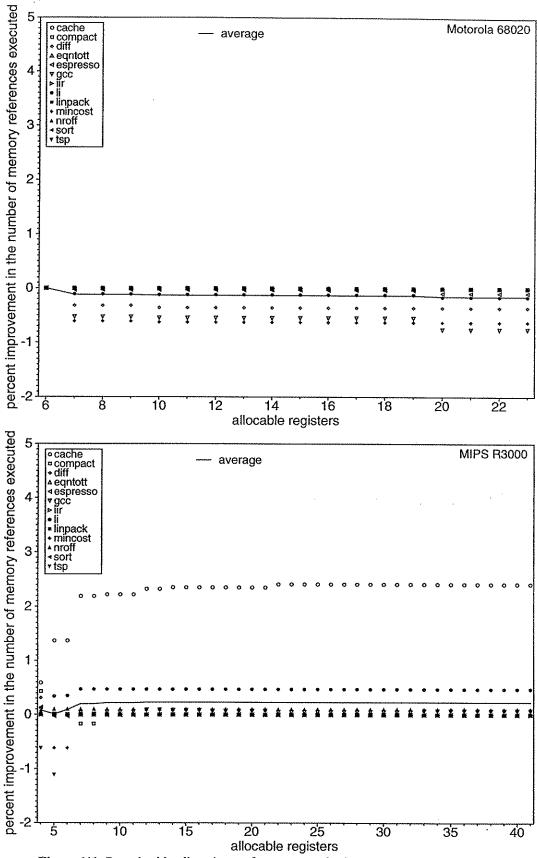

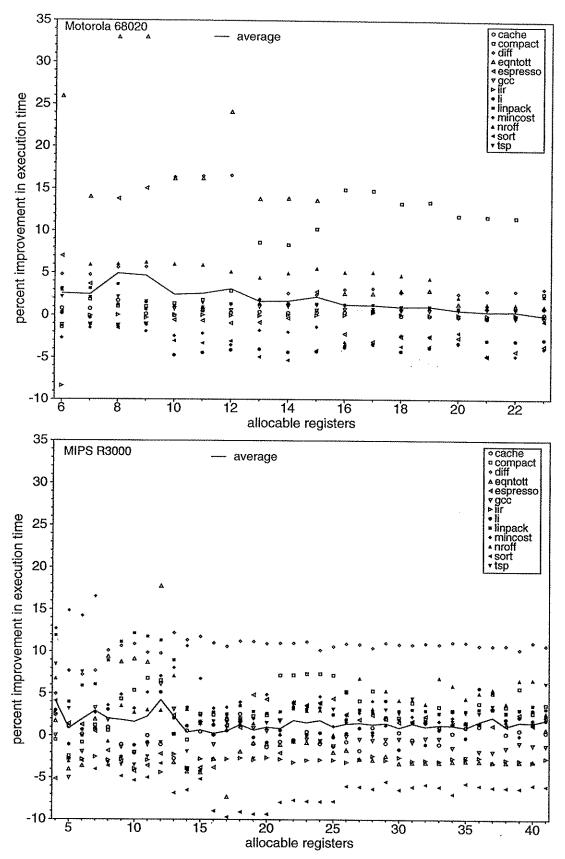

| Figure 20: | System performance results (execution times)                                | 53 |

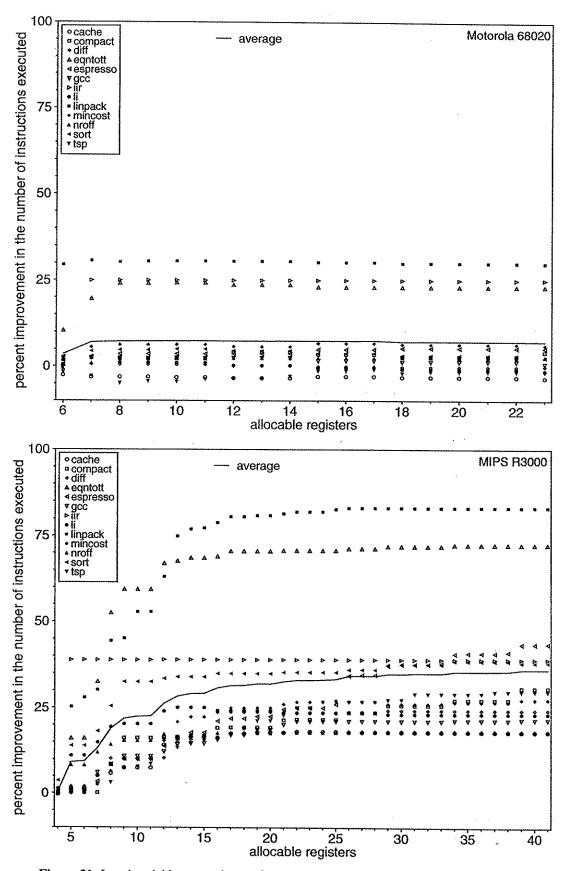

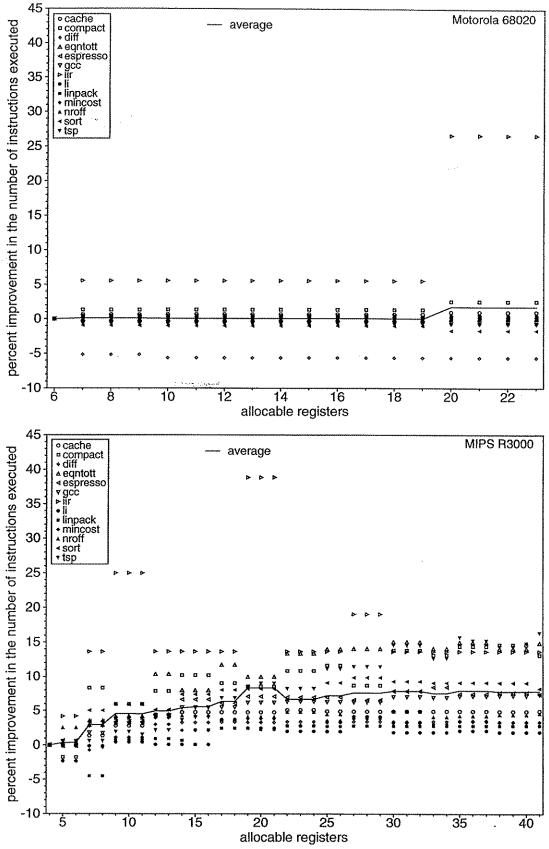

| Figure 21: | Local variable promotion performance results (instruction execution counts) | 56 |

| Figure 22: | Local variable promotion performance results (memory reference counts)      | 57 |

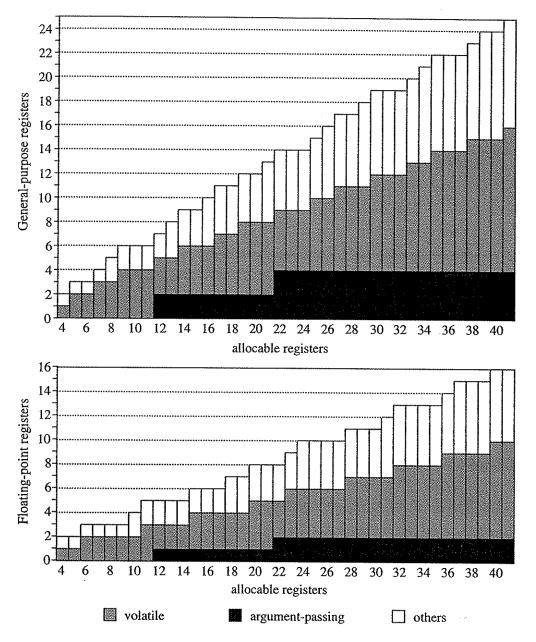

| Figure 23: | Registers available on each MIPS R3000 probe                                | 62 |

| Figure 24: | Registers available on each Motorola 68020 probe                            | 63 |

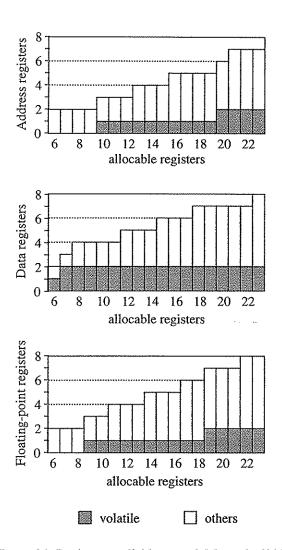

| Figure 25: | Calling convention interface code                                           | 65 |

| Figure 26: | Execution time comparisons between <i>llef</i> and production compilers     | 68 |

| Figure 27: | Optimization driver procedure                                               | 72 |

| Figure 28: | The SSA form for an if-then-else construct                                  | 73 |

| Figure 29: | Register description for the SPARC architecture                             | 76 |

| Figure 30: | A call sequence before local register assignment                            | 79 |

| Figure 31: | A call sequence after local register assignment                             | 82 |

|            | مندون                                                                                   |     |

|------------|-----------------------------------------------------------------------------------------|-----|

| Figure 32  | : Expression calculation code sequence                                                  | 83  |

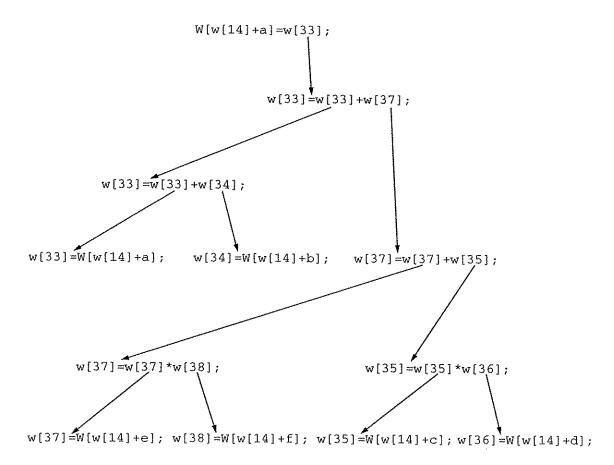

| Figure 33  | : Evaluation order determination expression tree                                        | 84  |

| Figure 34  | : Evaluation order determination algorithm                                              | 85  |

| Figure 35  | : Initial carry and use values                                                          | 86  |

| Figure 36  | : Final carry and use values                                                            | 86  |

| Figure 37  | : The reorder_subexpression function                                                    | 87  |

| Figure 38  | : The move_closer function                                                              | 87  |

| Figure 39  | Expression code sequence after evaluation order determination                           | 88  |

| Figure 40: | : Local register allocation before and after evaluation order determination             | 89  |

| Figure 41: | : Local interference graph construction algorithm                                       | 90  |

| Figure 42: | : Basic block and its associated local interference graph nodes                         | 92  |

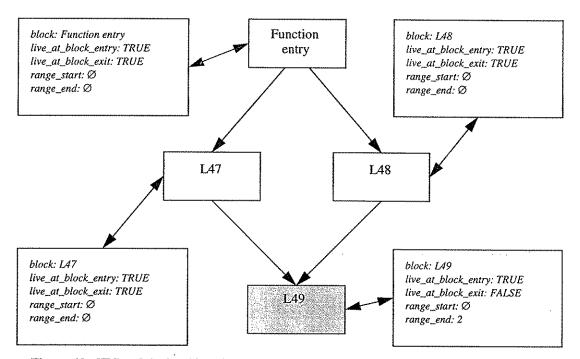

| Figure 43: | : CFG and the local interference graph nodes for argument b before live range reduction | 93  |

| Figure 44: | Graph node merge algorithm                                                              | 94  |

| Figure 45: | Global coloring assignment algorithm                                                    | 96  |

| Figure 46: | Local coloring assignment algorithm                                                     | 97  |

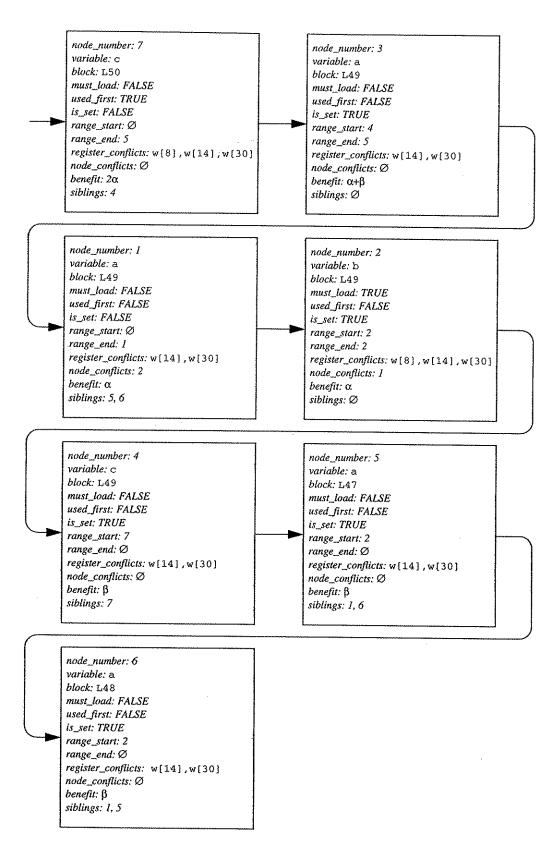

| Figure 47: | Global interference graph nodes                                                         | 98  |

| Figure 48: | Code after coloring process                                                             | 99  |

| Figure 49: | Loop-invariance determination algorithm                                                 | 101 |

| Figure 50: | Loop containing loop-invariant register assignments                                     | 102 |

| Figure 51: | Loop after loop-invariant code motion                                                   | 103 |

| Figure 52: | Loop containing an induced expression                                                   | 04  |

| Figure 53: | Basic induction variable detection algorithm                                            | 105 |

| Figure 54: | Regular induction variable detection algorithm                                          | 106 |

| Figure 55: | Induced address expression detection algorithm                                          | 107 |

| Figure 56: | Induced address expression replacement algorithm                                        | 109 |

| Figure 57: | Loop after loop strength reduction                                                      | 10  |

| Figure 58: | Loop after phase iteration                                                              | 10  |

| Figure 59: | Loop with three related induced expressions                                             | 10  |

| Figure 60: | Loop with three new induction variables                                                 | 11  |

| Figure 61: | Loop with one new induction variable                                                    | 11  |

| Figure 62: | The exploit_index_mode procedure                                                        | 12  |

| Figure 63: | Loop containing a first-order recurrence                                                | 13  |

| Figure 65: Loop containing possible extraneous dependences                    |

|-------------------------------------------------------------------------------|

| Figure 64: Low-level loop with recurrence                                     |

| Figure 66: Partition determination algorithm                                  |

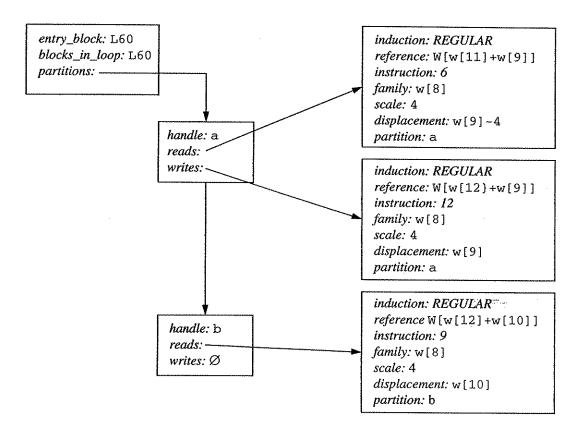

| Figure 67: Memory reference and partition information                         |

| Figure 68: Relative offset determination algorithm                            |

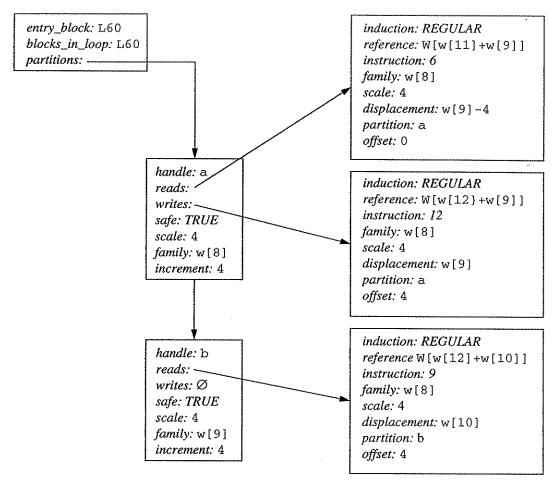

| Figure 69: Final memory reference and partition information                   |

| Figure 70: Recurrence detection and optimization algorithm                    |

| Figure 71: Loop after recurrence optimization                                 |

| Figure 72: Loop containing recurrence after phase iteration                   |

| Figure 73: Induction variable elimination algorithm                           |

| Figure 74: Loop after induction variable elimination                          |

| Figure 75: Loop after phase iteration                                         |

| Figure 76: Three-stage pipeline                                               |

| Figure 77: Pipeline execution diagram for loop body                           |

| Figure 78: Instruction scheduling algorithm                                   |

| Figure 79: The calculate_leader_set function                                  |

| Figure 80: Loop code before instruction scheduling                            |

| Figure 81: The choose_instruction function                                    |

| Figure 82: Instruction scheduling sequence                                    |

| Figure 83: Loop after instruction scheduling                                  |

| Figure 84: Pipeline execution diagram for scheduled loop                      |

| Figure 85: Branch-induced pipeline stall                                      |

| Figure 86: Branch delay slot filler algorithm                                 |

| Figure 87: The fill_both_paths function                                       |

| Figure 88: Sample machine code sequence                                       |

| Figure 89: Equivalence table construction                                     |

| Figure 90: Code after common subexpression elimination                        |

| Figure 91: Code sequences after local register assignment                     |

| Figure 92: Common subexpression elimination after local register assignment   |

| Figure 93: Code sequence containing a recomputation                           |

| Figure 94: Recomputation elimination                                          |

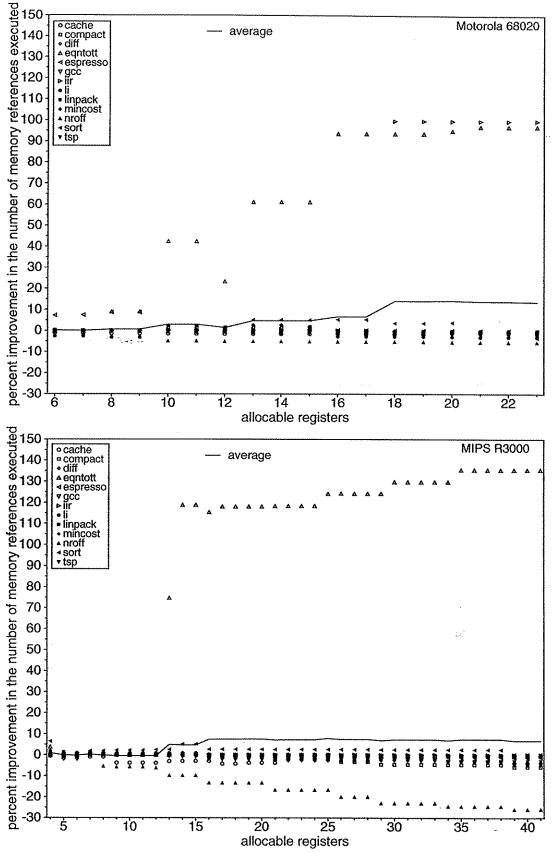

| Figure 95: Impact of recalculation elimination (instruction execution counts) |

| Figure 96: Impact of recalculation elimination (memory reference counts)                           |

|----------------------------------------------------------------------------------------------------|

| Figure 97: Loop containing a loop-invariant expression assigned to a reused register               |

| Figure 98: Loop-invariant code motion enhancement algorithm                                        |

| Figure 99: Loop after the enhanced loop-invariant code motion algorithm is applied                 |

| Figure 100: Loop after phase iteration                                                             |

| Figure 101: Loop after the re-invocation of loop-invariant code motion                             |

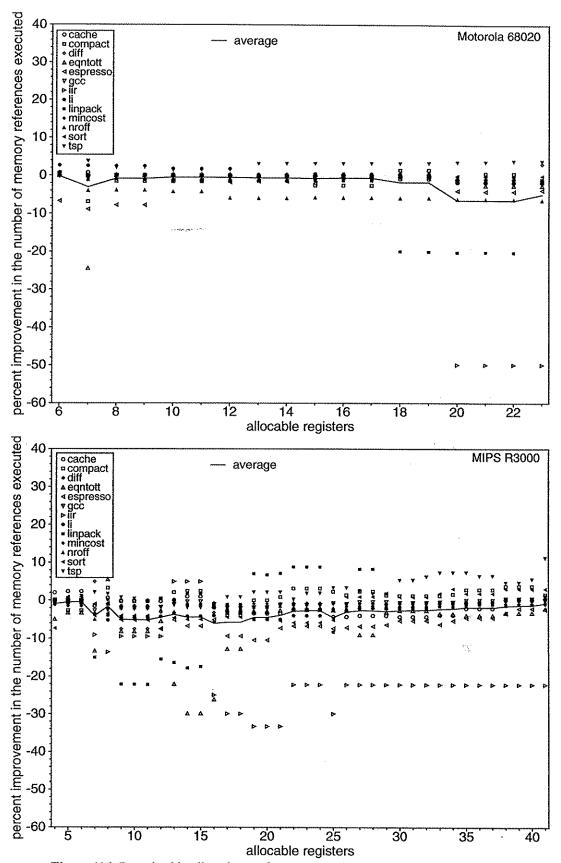

| Figure 102: Enhanced loop-invariant code motion results (instruction execution counts)             |

| Figure 103: Enhanced loop-invariant code motion results (memory reference counts)                  |

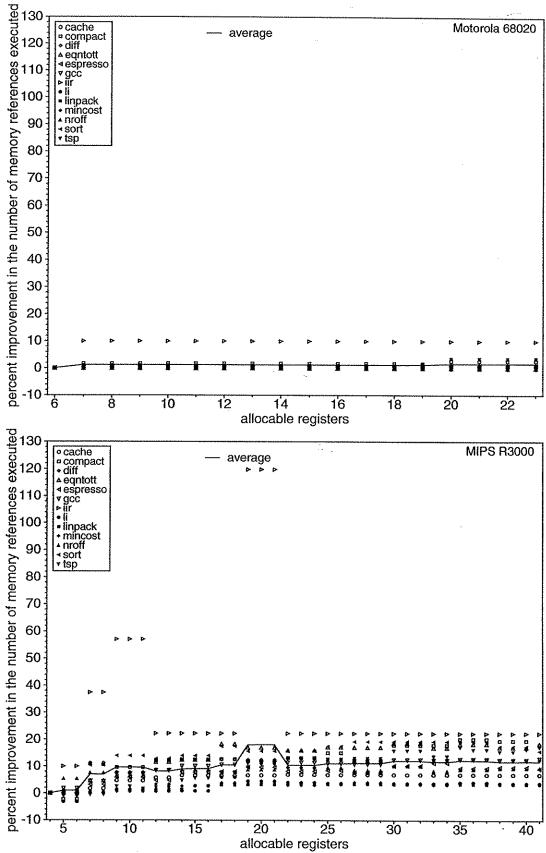

| Figure 104: Performance of coloring vs. simple global register allocation (instruction counts) 153 |

| Figure 105: Performance of coloring vs. simple register allocation (memory reference counts) 154   |

| Figure 106: Fragment of code before local register allocation                                      |

| Figure 107: Code fragment after traditional local register assignment                              |

| Figure 108: Code fragment after round-robin local register assignment                              |

| Figure 109: Code fragment after round-robin assignment and common subexpression elimination 156    |

| Figure 112: The effect of round-robin allocation on a two-address instruction set                  |

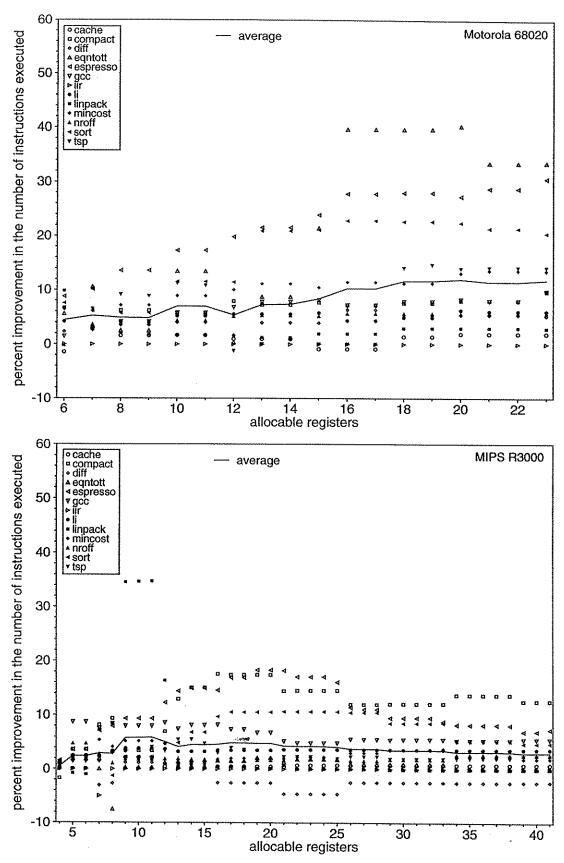

| Figure 110: Round-robin allocation performance results (instruction execution counts)              |

| Figure 111: Round-robin allocation performance results (memory reference counts)                   |

| Figure 113: Effect of round-robin allocation on CSE (instruction execution counts)                 |

| Figure 114: Effect of round-robin allocation on CSE (memory reference counts)                      |

| Figure 115: Round-robin allocation performance results (instruction execution counts)              |

| Figure 116: Round-robin allocation performance results (memory reference counts)                   |

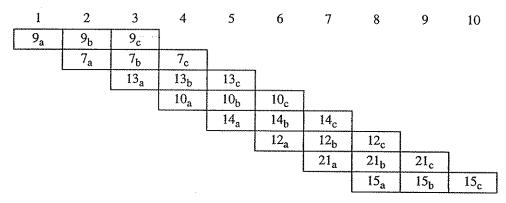

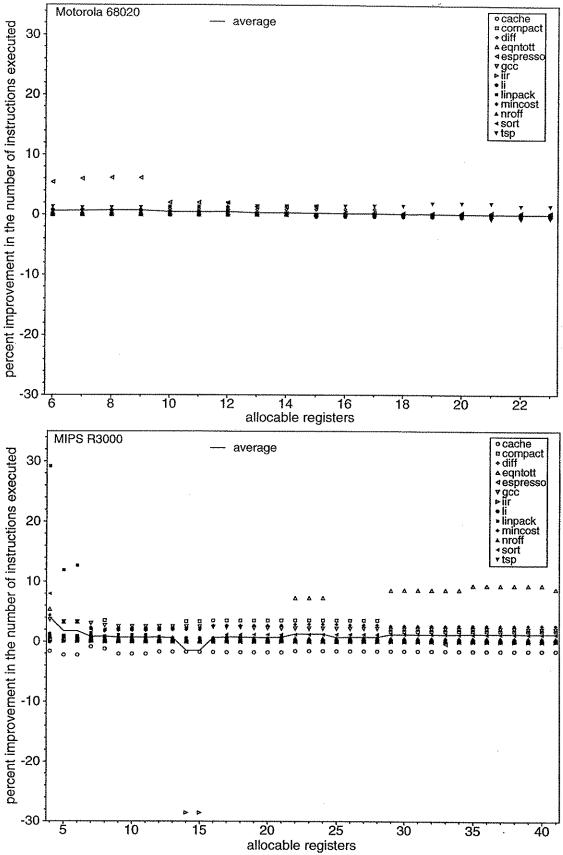

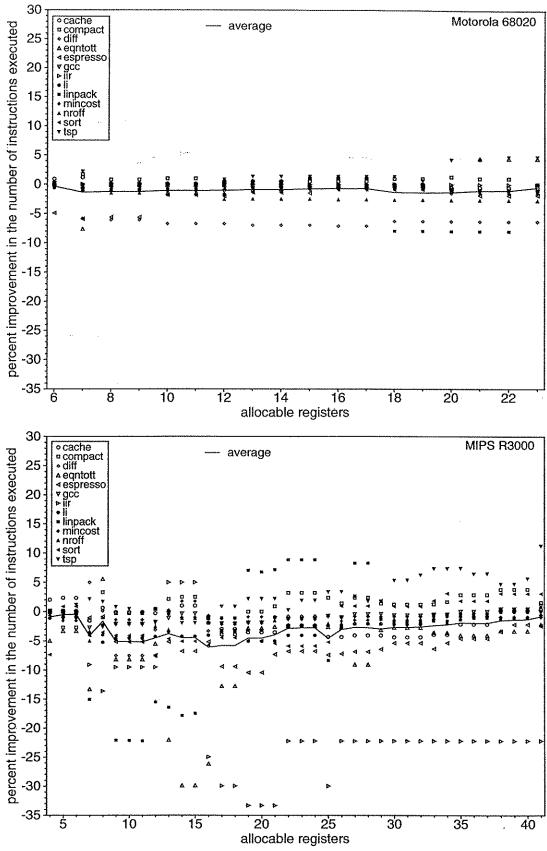

| Figure 117: Bounded-register results for the Motorola 68020                                        |

| Figure 118: Bounded-register results for the MIPS R3000                                            |

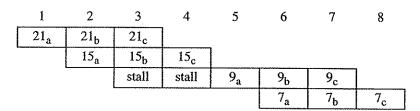

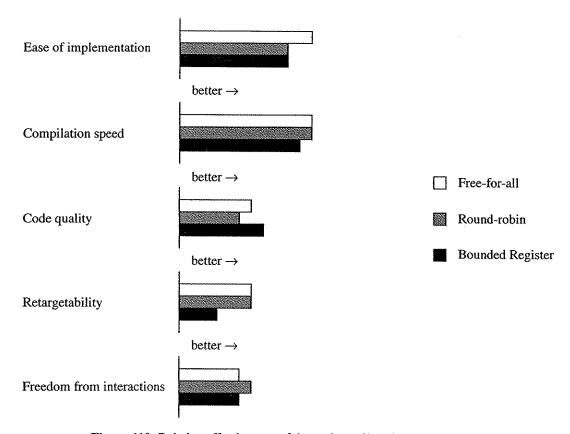

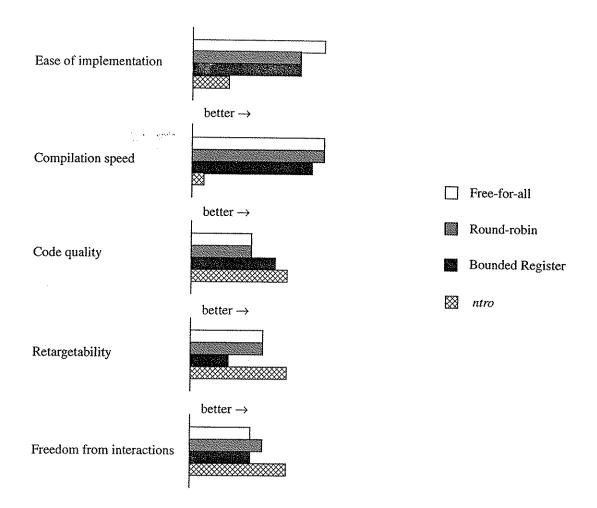

| Figure 119: Relative effectiveness of the register allocation strategies                           |

| Figure 120: Bounded-register allocation performance results (instruction execution counts) 169     |

| Figure 121: Bounded-register allocation performance results (memory reference counts) 170          |

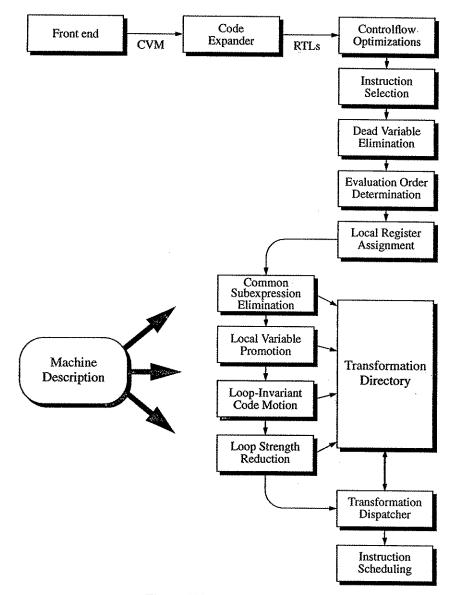

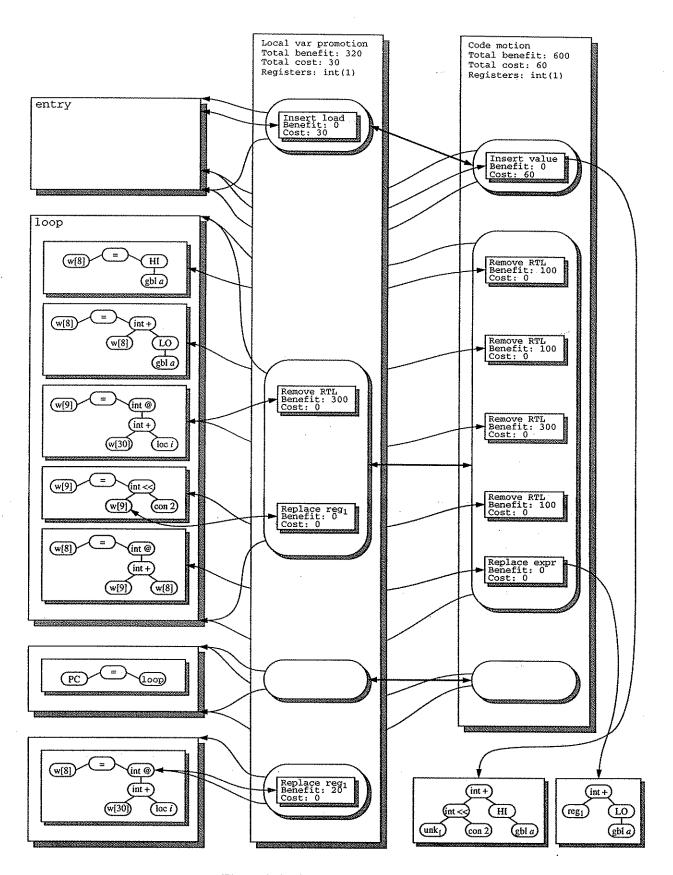

| Figure 122: The structure of <i>ntro</i>                                                           |

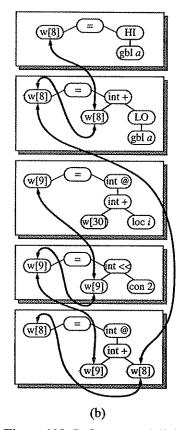

| Figure 123: Define-use web links                                                                   |

| Figure 124: The transformation directory                                                           |

| Figure 125: ntro performance results (instruction execution counts)                                |

| Figure 126: ntro performance results (memory reference counts)                                     |

| Figure 127: ntro performance results (execution times)                                             |

|   | ٠ | • | ٠ |  |

|---|---|---|---|--|

| v | 1 | 1 | 1 |  |

| Figure 128: Number of machine-dependent source code lines                                    | 181 |

|----------------------------------------------------------------------------------------------|-----|

| Figure 129: Relative performance of <i>ntro</i> and the allocation strategies in <i>llef</i> | 182 |

-·

# CHAPTER 1

# INTRODUCTION

Optimizing compilers capable of producing high-quality machine code are frequently used to help satisfy the ever-growing demand for computer system performance. Because of their complexity, the amount of time and effort required to design, implement and validate these optimizing compilers can be justified only if they serve a large number of users over a long period of time. At the current rate of progress, however, existing architectures are becoming obsolete and their users migrating to new systems in increasingly short periods of time. As this trend continues, it will become harder to justify the development of optimizing compilers that are not retargetable enough to migrate along with their users to new architectures.

Unfortunately, retargetability is not easily retrofitted into an optimizing compiler. The ability to operate across a broad spectrum of architectures must be incorporated not only into the parts of the compiler that generate machine code, but also those that perform code improvement transformations and manage resources. In essence, retargetability is a pervasive attribute that must be designed into the overall compilation strategy starting with the intermediate language, which is the internal representation of the code that the compiler performs code improvement transformations on.

Recent developments suggest that intermediate languages that can represent actual target machine instructions are particularly well-suited for use in high-quality retargetable optimizing compilers that need to exploit unique architectural features. Because the majority of existing retargetable compilers use intermediate languages that represent architecture-independent high-level code, however, little is known about how to structure code improvement algorithms that operate on low-level languages capable of representing machine code so as to maximize their effectiveness and their retargetability. Additionally, there remain some concerns as to whether it possible to extract sufficient high-level information from these intermediate representations to perform effective code improvements.

Good register allocation is essential to an optimizing compiler because most code improvement transformations require registers. The number and type of registers provided by an architecture, however,

varies widely and is one of the major factors limiting the effectiveness of the allocator. In spite of this, most retargetable optimizing compilers use register allocation techniques that operate effectively only on a limited range of register sets and, therefore, produce high-quality code only for architectures that provide these kinds of register files. Designing a retargetable register allocation strategy that is effective across a wide range of architectures, however, is particularly challenging because strategies that provide good register allocation on architectures with small register files are quite different from strategies that perform effective allocation on architectures with large register sets.

The following sections expand on this brief introduction, present further evidence to support the notion that high-quality retargetable optimizing compilers should use machine-level intermediate languages and highly-retargetable register allocation algorithms. These sections are followed by a description of the scope and direction of the investigation needed to find answers to some of the unresolved issues associated with these compilation strategies.

#### 1.1 Retargetable optimizing compilers

During the process of translating code written in a high-level programming language into a sequence of low-level machine instructions, a compiler must, at some point, generate machine code from a higher-level representation of the code and find suitable storage locations for the temporary values needed to construct arbitrarily complex expressions from a small set of basic instructions. In addition to performing these tasks, an optimizing compiler must also enhance the quality of the code by applying a comprehensive set of code improvement transformations. Consequently, optimizing compilers are large, complex systems that perform competent code generation, register allocation and code improvement transformations. While the ability to generate correct, high-quality machine code is the main objective of an optimizing compiler, retargetability is gradually playing a greater role in the design of these systems.

#### 1.1.1 What is retargetability?

Retargetability is a measure of how easily a compiler can be modified to produce code for a new architecture. To achieve a high degree of retargetability, the portions of the optimizing compiler that perform

<sup>&</sup>lt;sup>1</sup> Code improvement transformations are commonly referred to as optimizations, which is a misnomer since code improvements rarely, if ever, result in "optimal" code.

code improvement transformations, allocate registers and generate machine code must be able to tolerate a certain amount of variability in the following architectural components:

- the functionality and the encoding of the instruction set,

- the size, partitioning and regularity of the register set,

- the number, capabilities and organization of the processing units,

- the data types supported and their formats,

- the addressing modes available,

- the width of the data paths,

- the degree of pipelining,

- the number of levels in the memory hierarchy,

- the size, relative speed and alignment requirements of the levels in the memory hierarchy and

- the mechanisms provided to support high-level languages.

This list is incomplete because many of the less common architectural elements have been omitted. Also, architectural innovations constantly add new items to this list. The impact of this architectural diversity on an optimizing compiler is so pervasive that retargetability cannot be easily retrofitted into the compiler, but must be incorporated into the overall compilation strategy.

## 1.1.2 Why is retargetability important?

As the quality of the code that optimizing compilers are expected to produce rises in response to the growing demand for system performance, the effort required to design, implement and validate an optimizing compiler increases. While it might seem unreasonable to further complicate this process by making the compiler highly retargetable, doing so is justified because:

- the effort spent in developing a retargetable optimizing compiler can be amortized over a longer period of time and a greater number of users than its less-retargetable counterparts,

- a longer life-span promotes the development of new code improvements and the enhancement of existing ones, which improves the overall quality of the code produced by the compiler,

- retargeting an existing compiler is a cost-effective way (and often the only cost-effective way) to produce high-quality machine code for processors with limited applications or few users and

- a retargetable compiler is a useful architectural design tool.

Rapid advances in VLSI technology, processor design and memory systems effectively reduce the useful life-span of existing architectures. Shorter life-span, in turn, make it increasingly difficult to justify the time and effort required to produce high-quality optimizing compilers that are bound to a single architecture. The life-span of a retargetable optimizing compiler, however, is independent of any one architecture and, thus, is more likely to outlive most, if not all, of its less retargetable contemporaries.

Another argument for the development of a retargetable optimizing compiler is that its user base can be quickly expanded with relatively little effort by retargeting it to a popular architecture. For this strategy to work, however, it is essential for the compiler to compare favorably against the other compilers available for that architecture. The current popularity of *gcc* [STAL89], for example, is due not only to the large number of systems for which it can produce code, but also to its low cost and the reasonable quality of the code that it produces.

The time saved moving a retargetable optimizing compiler to the next generation architecture instead of constructing an entirely new compiler for it can be spent enhancing existing code improvements or developing new ones. This not only improves the quality of the code retroactively across all of the architectures to which the compiler has targeted, but also makes the compiler more competitive against other compilers and subsequently increases its user base. Sometimes new code improvements are needed to utilize a feature provided by a new architecture but, because similar features are likely to appear in other architectures, the new transformation will improve the overall quality of the code produced by the optimizer across different architectures.

There is a substantial group of useful architectures, primarily intended to support embedded systems and signal processing, for which no compilers capable of producing high-quality machine code exist. One reason for this shortcoming is that the amount of code developed on these systems is too small to justify the development of a new optimizing compiler. The simpler task of adapting a highly-retargetable optimizing compiler to such a system, however, is more likely to be cost effective.

Retargetable optimizing compilers provide computer architects with the ability to gauge the impact of new architectural components and features on existing compiler technologies. Because a retargetable compiler can be targeted to the new architecture early in the design process, it can provide valuable feedback to the architect. This feedback can help to resolve important design issues such as how useful certain instructions, operations or addressing modes are, how many registers of each type should be provided and how many pipeline stages the processor should have.

#### 1.1.3 Intermediate representations

Intermediate representation are used to isolate significant portions of the compilation process from the idiosyncrasies of the source language and the target architecture. This isolation is attained using the following strategy: the *front end* of the compiler transforms the source code into semantically equivalent intermediate code which is then improved by a series of code improvement transformations before it is transformed into machine code by the *back end*. The choice of an intermediate representation seriously affects the retargetability of an optimizing compiler [CHOW83]. The types of intermediate representations have been used in optimizing compilers are fixed, high-level intermediate representations and low-level representations.

Because fixed, high-level representations are independent of the target architecture, they require no modification to retarget. Likewise, the code improvement algorithms that operate on these representations remain unchanged across different architectures. Together, these two factors account for much of the retargetability that high-level representations provide. Unfortunately, high-level representations provide the code improvement algorithms with little control over all but the most common architectural features, thereby limiting the effectiveness of code improvement transformations [BENI94]. These limitations apply not only to code improvements like *peephole optimization* [MCKE65] and *instruction scheduling* [HENN83], which exploit specific architectural features, but also to code improvements like *loop-invariant code motion* [AHO86] and *evaluation order determination* [SETH70], whose broad applicability has fueled the myth that they can be effectively performed on high-level representations. The fallacy of this assumption is illustrated with a few simple examples. First, consider that after all loop-invariant items have been moved out of a high-level representation of a loop, the machine code produced for the loop could still contain part of a loop-invariant computation of a high-level constant expression that is too large to fit into an operand field on the target machine. Similarly, optimal evaluation orders cannot be produced on representations that obscure the register requirements of the machine code [MCKU84, DAVI86].

The factors that limit the effectiveness of code improvements transformations that operate on high-level representations can be avoided by using low-level representations. Unlike their high-level counterparts, low-level representations encode the semantics of a wide range of machine instructions. One of the most commonly used notations used to represent low-level code is the *register transfer* [BELL71]. Register transfers have been successfully used in a number retargetable optimizing compilers including PO [DAVI81].

YC [DAVI84b], vpo [BENI89] and gcc [STAL89]. Regardless of the underlying notation, low-level representations allow the code improvement algorithms to operate at the machine level where all of the target machine nuances are exposed and all transformations, including those that exploit specific architectural features, can be performed effectively. This fact alone makes low-level representations more suitable for use in high-quality retargetable optimizing compilers than high-level representations.

While high-level representations shield code improvement algorithms from the target machine, low-level representations expose them to the target architecture. Because of this, significantly more foresight and planning is required to use these representations in a retargetable framework. Since architecture-specific issues are not hidden form low-level code improvement algorithms, retargetability entails isolating the architecture-specific portions of the algorithms behind an appropriate interface to limit the amount of code that the user must examine during the targeting process. Equally important is the need to extract enough high-level information from low-level code to support complex code improvement transformations. For example, a particular transformation may require extensive alias analysis to ensure that all of the references to a crucial variable are known. Failure to extract such high-level information limits the set of transformations that the compiler can safely apply and degrades the quality of the code produced.

#### 1.1.4 Register allocation

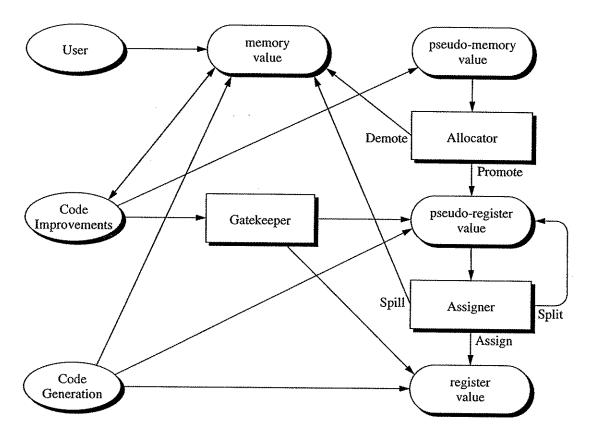

Making effective use of the registers provided by each architecture, which is essential to producing high-quality code, is the job of the register allocator. The register allocation process is profoundly affected by the widely-varying specifics of the registers resources provided by the target architecture. Consequently, neglecting to account for the effects of architectural diversity on the register allocator can severely limit the retargetability of an optimizing compiler.

Most register allocation strategies provide the code improvement algorithms with an inexhaustible supply of registers, called *pseudo-registers*, to use when performing transformations. Under this strategy, the register allocation process consists of assigning actual machine registers to pseudo-registers. Because the set of target registers is finite, the assigner is sometimes unable to assign a target machine register to all of the pseudo-registers and is forced to *spill* some pseudo-register values to memory. Since it takes longer to access a value in memory than it does to access a value in a register, a good assigner strives to spill only values that have a minimal impact on the quality of the code. While this strategy works well when the target architecture

has many registers<sup>1</sup>, it produces an unacceptable number of spills on architectures that provide few registers. Furthermore, this register allocation strategy does not prevent code improvement transformations from overcommitting registers and producing code whose quality is worse than that of the original, unimproved code. The term, *over-optimization*, has been used to describe this situation [AUSL82].

To prevent over-optimization, the compiler can abstain from using pseudo-registers by requiring code improvements transformations to obtain actual target machine registers. Unfortunately, this approach limits the internal representation to a finite set of machine registers and forces the compiler to reuse registers while performing code improvements, thereby introducing a few potential disadvantages. First, the register assignment decisions made by each code improvement algorithms constrain the allocation choices available to subsequent transformations. In compilers that perform code improvements using an infinite set of registers, this problem only occurs while applying low-level code improvements like instruction scheduling [GOOD88]. Second, the need to reuse registers complicates the task of determining which values have been previously computed since each individual expression value is no longer associated with a unique pseudo-register. Third, the process of extending the life of a register value is complicated by the fact that an appropriate register must be allocated from a limited set of registers. Finally, it is difficult to determine that a code transformation that releases at least as many registers as it consumes can be applied when all of the remaining registers are in use. When pseudo-registers are used, there is always a register available to perform these transformations.

#### 1.2 The scope of this investigation

The goal of this research is to develop and evaluate low-level code improvement and register allocation algorithms that are both retargetable and conducive to high-quality code generation. The following sections define the scope and direction of this endeavor.

#### 1.2.1 Architectures

While retargetability is an important attribute of the algorithms developed during the course of this investigation, practical considerations limit the set of architectures used to evaluate these algorithms. Proof of effectiveness will be limited to general-purpose and specialized (e.g., embedded systems, digital signal processing systems) uniprocessors both with and without pipelines, and providing either complex (CISC) or

<sup>&</sup>lt;sup>1</sup> The exact boundary between many and few registers depends on numerous factors, although it is generally between ten and sixteen registers. More details will be provided in the following chapter.

reduced (RISC) instruction sets. VLIW and superscalar architectures are not specifically excluded and many of the algorithms presented here should perform well on these types of architectures with few modifications. On the other hand, vector, dataflow and parallel processors will not be considered in this dissertation.

With regards to the memory hierarchy, this dissertation is concerned primarily with architectures that provide an individually-addressable set of registers with a minimum of two registers for each basic data type on the processor. There is no upper-bound on the number of registers that the architecture may provide, although the scope over which the code improvement algorithms performed by the experimental framework operate is unlikely to effectively use more than 64 registers of any one basic data type. Although pure accumulator-based architectures and stack-based architectures are not excluded, no effort will be made to determine the effectiveness of any algorithm on these machines.

# 1.2.2 Code improvement transformations

Because high-quality code cannot be produced with only a few code improvement transformations, this investigation examines a comprehensive set of code improvements. This set consists of both *local* code improvements, whose scope is limited to a single *basic block*<sup>1</sup>, and *global* code improvements, whose scope span an entire function. Improvements across function boundaries, called *inter-procedural* improvements, are omitted from this investigation although many of the techniques presented here apply to them.

Of the set of code improvements included in the investigation, the following are usually performed on high-level code:

- constant folding, which entails performing operations with constant operands at compile time,

- dead variable elimination, which eliminates assignments to values that will not be referenced in the future,

- copy propagation, which attempts to eliminate copies of an item by replacing them with a reference to the original instance of the item,

- evaluation order determination, which orders instruction sequences to reduce the number of registers needed to compute expressions,

- common subexpression elimination, which detects and eliminates redundant computations,

- loop-invariant code motion, which moves loop expressions that remain invariant across each iteration of the loop to a location outside the loop

- loop strength reduction, which replaces complex expressions that generate simple arithmetic sequences within a loop with simpler expressions that are less expensive to compute,

A basic block consists of a sequence of straight-line code that can only be executed starting with the first instruction in the sequence and exited only through the last instruction [AHO86].

- induction variable elimination, which removes unneeded induction values from a loop,

- dead code elimination, which deletes code that will never be executed.

- branch chain elimination, which changes any branch that transfers control to another branch to branch directly to the destination of the second branch and

- *jump minimization*, which reduces the number of control transfers in a control flow graph (CGF) by performing a topological sort on the CFG.

In addition, recurrence optimization [BENI91b], which eliminates memory references by keeping values that will be used in subsequent loop iterations in registers, is included even though it is an application-specific improvement usually performed only by compilers specializing in compiling either scientific or digital processing codes. Finally, the architecture-specific code improvements called peephole optimization [MCKE65], instruction scheduling [HENN83] and delay slot filling [HENN90] are also included.

This dissertation presents newly-developed retargetable algorithms for performing evaluation order determination, loop-invariant code motion, loop strength reduction, induction variable elimination, recurrence optimization, instruction scheduling and delay slot filling on low-level code. These algorithms were developed using *llef* (which stands for *low-level experimental framework*), which was specifically built to support and measure low-level code generation, register allocation and code improvements, and are designed to exploit specific architectural features and isolate the portions of the algorithm that are affected by the target architecture. These algorithms are effective because they can handle special architectural features and retargetable because they are largely independent of the target architecture. To show that these algorithms are retargetable, they have been targeted, along with *llef*, to six different architectures. To show that they are effective, the quality of the code that they produce will be compared with the quality of the code produced by some of the optimizing compilers available for these architectures.

#### 1.2.3 Register allocation

Because code improvement and code generation algorithms cannot produce high-quality code without a adequate supply of registers, developing register allocation strategies that operates effectively across a wide range of architectures is an important part of this investigation. An important feature of this strategy will be freedom from over-optimization. Techniques that can be used to minimize interactions between the register allocation decisions made during code generation and the subsequent code improvement transformations will also be explored.

To prevent over-optimization, code improvement transformations will be performed exclusively on machine code after a local-scope algorithm assigns target registers to the pseudo-registers created by the code generator to hold temporary expression values. The advantage of this strategy is that it allows the compiler to determine which machine registers are used not only after the initial code sequence is generated, but also as code improvement transformations are applied. A separate global-scope algorithm promotes user-defined variables to registers. The code improvement algorithms that perform loop-invariant code motion, loop-strength reduction, recurrence optimization and induction variable elimination use a register allocation algorithm whose scope is the loop that these improvements are transforming. A number of variations on this basic theme will be examined to determine how the register allocator can best ensure that scarce register resources are given to the transformations that will most improve the quality of the code.

The effectiveness of the register allocation algorithms presented in this dissertation will be measured with a *register deprivation* measurement technique that was developed specifically for this purpose. Using this technique, a single architecture can effectively simulate the register set environment presented by a substantial number of different architectures. This allows a pair of architectures, one CISC and one RISC, to be used to gauge the retargetability and the effectiveness of the register allocation strategies developed with the aid of *llef* across a broad spectrum of architectures.

# 1.3 Structure

The following two chapters give additional background information on code improvement and register allocation along with an overview of previous work that is closely related to the research presented in this dissertation. Chapter four presents the techniques used to perform register deprivation experiments which were developed specifically to measure the efficacy of the algorithms presented in this dissertation and have applications beyond their original purpose. The fifth chapter introduces *llef* the code improvement algorithms developed using it. The results of the measurements performed to determine the efficacy of this new framework are also included in this chapter. Chapter six discusses the algorithms that were developed to perform register allocation strategies that do not suffer from over-optimization even when the target architecture provides very few registers. In addition, this chapter shows the algorithms that were developed to overcome the problems associated with using target registers instead of pseudo-registers to perform code improvement transformations. This chapter closes with a description of an entirely new compilation strategy

that is uniquely suited to low-level compilation and was developed using the experience gained in the course of this investigation. Finally, chapter seven concludes this dissertation with a brief summary.

|  |  | er. |

|--|--|-----|

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

# **CHAPTER 2**

# CODE IMPROVEMENTS

Code improvements play an important role in the generation of high-quality machine code. This chapter examines several different strategies for incorporating a substantial set of code improvements into a retargetable optimizing compiler framework. This chapter also presents a brief overview of some of the systems that have influenced the strategies used in the optimizing compiler framework developed to support this research.

# 2.1 The motivation for comprehensive code improvement suites

The impact of any single code improvement is not uniform throughout all of the code that a compiler generates. While the majority of code improvements substantially enhance the quality of the code regions that exhibit the particular properties that they are designed to detect and improve, they have little effect on the remaining code. Overall, the reduction in execution time produced by a single code improvement rarely exceeds two or three percent when measured on an adequately large set of benchmark programs. Since the magnitude of these improvements is quite modest, optimizing compilers must perform a comprehensive set of code improvements in order to produce high-quality object code. The set of improvements performed by an optimizing compiler is called its code improvement suite.

## 2.2 Code improvement phases

Implementing a comprehensive set of code improvements and orchestrating their function within a single compiler is a daunting task. To simplify the complexity of this task, individual code improvements are generally implemented as a separate, isolated *phases*. Each phase is invoked at a pre-determined time in the compilation process, performs its code improvement transformations on an intermediate representation of the source code, and returns control to the compiler. This modularization eliminates most of the communication paths and the potential interactions between the various code improvements, thus making the system easier to develop, implement, test and maintain. Isolating the compilation and code improvement process into a series of independent phases has proved so beneficial that it is used in most, if not all, optimizing compilers.

#### 2.3 Phase interactions

Although modularization reduces the number of potential interactions between code improvement phases in optimizing compilers, even modularized systems interact in ways that make it difficult to determine the optimal order in which phases should be performed or preclude any such ordering altogether. Among the factors responsible for these interactions are:

- the competition for scarce machine resources (e.g. registers, easily-accessed memory locations, co-processors, etc.),

- the inability to track changes in the data-flow, control-flow or alias information caused by previous transformations,

- attempting to perform code improvements that are mutually exclusive,

- applying transformations that trigger other transformations and

- changing the representation of the code.

These factors complicate the ordering of the phases in a compiler and cause *phase ordering problems*. Unless steps are taken to minimize these factors, phase ordering problems can severely limit the effectiveness of a code improvement suite.

Phase ordering problems in retargetable compilers are exacerbated by the fact that architecturespecific issues such as the size of the register file and the complexity of the instruction set profoundly affect the optimal phase ordering. Consequently, frameworks that automatically determine effective phase orderings have the serendipitous advantage of simultaneously enhancing both the quality of the emitted code and the retargetability of the compiler. This is because failing to determine an appropriate phase ordering for the target architecture sacrifices some of the code quality that can be expected from a retargetable compiler while forcing the person retargeting the compiler to spend time performing this task reduces its retargetability.

# 2.4 Organizational structure

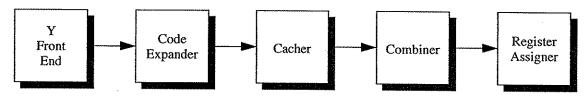

The concept of dividing a compiler into a front-end and a back-end was introduced in Section 1.1.3. The organizational structure resulting from this strategy is illustrated in Figure 1. While performing lexical and semantic analysis on the source code, the front-end not only ensures that the input conforms to the syntactic and semantic rules of the source language, but also produces a high-level intermediate representation of the code. Since high-level representations are independent of the target architecture, properly designed front-ends require little target-machine information.

Figure 1: The front and back ends of an optimizing compiler

The back-end of the compiler accepts the high-level code produced by the front-end, applies a series of code improvements to it, determines how the register resources are to be utilized and produces code that the target machine can execute. Since the exact nature of these tasks depend on the target architecture, the back-end must incorporate information about the target machine. The method used to encode this information affects the retargetability of the compiler. Machine descriptions encoded in an *ad-hoc*, diffused fashion are common in systems that are hard to retarget. One the other hand, the target machine descriptions found in highly-retargetable systems are centralized and are accessed by the rest of the back-end through well-defined interfaces.

Retargetable optimizing compilers generally perform code improvements at the intermediate code level, because high-level intermediate code is much less dependent on the target architecture than machine code is. This strategy enhances retargetability by allowing code improvement phases to remain independent of the target architecture and eliminates the need to provide these phases access to detailed architecture-specific information. As a result, the machine description is smaller and the retargeting process is simplified.

As mentioned in Chapter 1, however, most code improvements are either architecture-specific or interact with those that are. Unfortunately, the semantic gap between the high-level intermediate code and the machine code prevents architecture-specific code improvements from being applied effectively on high-level

intermediate code. Therefore, to accommodate the most essential architecture-specific code improvements, many back-ends invoke a set of *post-pass* phases after machine code is generated. The back-end structure resulting from this strategy is shown in Figure 2 and suffers from the following shortcomings:

- the majority of code improvements are performed prior to code generation and are therefore unable to fully exploit the capabilities of the target architecture,

- the opportunities created by the post-pass phases to perform code improvements that operate on high-level intermediate code are forfeited unless these improvements are duplicated at the machine code level,

- because of their highly architecture-specific nature, post-pass phases usually cater to specific architectures and are rarely retargetable and

- since the high-level context present in the source code is not as easily extracted from target machine code as it is from the intermediate code, post-pass improvements that require extensive data-flow, control-flow or alias analysis may lose much of their effectiveness.

Figure 2: Back-end with post-pass code improvements

Some of the shortcomings of the structure shown in Figure 2 are absent in the organizational framework illustrated in Figure 3, which performs code improvements exclusively on machine code. As a result, the nuances of the target architecture are exposed to the entire code improvement suite, thus eliminating the inefficiencies caused by the semantic gap between the intermediate code and the machine code. Additionally, architecture-independent improvements are applied to machine code and take advantage of the opportunities provided by even the architecture-specific transformations to further improve the code.

Figure 3: Structure of a back-end that operates exclusively on machine code

Although the framework in Figure 3 does not suffer from some of the disadvantages present in the framework in Figure 2, it is not inherently more retargetable and does not eliminate the need to extract high-level information from machine code. Furthermore, the framework introduces a new set of problems, including:

- since code improvements operate exclusively at the machine level, they usually require more target-architecture information than phases that operate on high-level, architecture-independent code do.

- phase interactions are more acute at the machine level, and

- the impact that code improvement transformations have on code generation and register allocation blurs the sharp boundaries between the back-end components shown in Figure 3.

Fortunately, all of these problems can be solved or significantly mitigated. A high level of retargetability can be obtained using an intermediate representation based on register transfers, which represent target machine instructions using an architecture-independent notation. Because an appropriately devised register transfer notation remains invariant across different architectures, large portions of the optimizing compiler, including the code improvement phases and the high-level information-extraction routines, can be made largely architecture-independent. Carefully executed, this strategy allows a simple interface to a small number of routines to provide all of the architecture-specific information needed to perform code improvements, code generation and register allocation at the machine-level. Finally, since all code improvements are performed on the same representation of the code, phase ordering problems can be reduced by using a *phase iteration*

strategy to re-invoke code improvement phase whenever opportunities to perform even previously-applied code improvements arise.

#### 2.5 Related work

The following sections introduce some of the retargetable optimizing compilers that have influenced the design of the optimizing compiler framework described in Chapter 5. These sections focus primarily on the overall structure of each compiler, the nature of the intermediate language on which the bulk of the code improvements are applied and the techniques used to minimize the interactions between the various code improvement phases.

## 2.5.1 Amsterdam Compiler Kit

The Amsterdam Compiler Kit (ACK) [TANE83] is a set of programs that simplify the task of developing a compiler. Like many modern retargetable compilers, ACK is based on the principle that a single, universal intermediate language, called an UNCOL [STEE61], allows N languages to be made available on M different architectures with only N front-ends plus M back-ends instead of M×N separate compilers. ACK includes front-ends for various languages, an intermediate language code improver that performs global-scope code improvements and peephole optimization on a high-level, machine-independent intermediate language called EM, a code generator, a post-pass code improver, a universal assembler and a linker. The structure of an ACK compiler is shown in Figure 4. EM succeed where previous UNCOLs failed by catering

Figure 4: Structure of a compiler produced with the Amsterdam Compiler Kit

only to architectures with individually-addressed, 8-bit bytes. Much of the ACK's retargetability can be attributed to the fact that it applies code improvements almost exclusively on its machine-independent intermediate code. The back-end consists of a machine-independent code generator that uses a target machine description table to convert EM code sequences into assembly language instruction sequences for the target machine.

Although ACK has been used to produce compilers that generate good code for a number of different architectures, it suffers from several deficiencies. Most of these deficiencies are the result of performing code improvements almost exclusively on a high-level intermediate language. For example, to support peephole optimization, EM has been embellished with nearly 100 special-purpose instructions that are little more than abbreviations of primitive instruction sequences. While these special-purpose instructions allow ACK to exploit common machine-specific features like pre-decrement and post-increment addressing modes, there is no guarantee that the improvements made to the EM code will result in higher-quality machine code. In fact, most of the peephole transformations applied to the EM code do not improve the machine code produced on RISC architectures that lack complex addressing modes. Not only are some of the improvements made at the intermediate level useless, but some essential improvements are missed. Consequently, to produce good code, ACK must also perform peephole optimization at the machine level. This strategy complicates the compiler, the intermediate language and the retargeting process. Furthermore, in spite of these measures, ACK-based compilers are unable to produce high-quality RISC code.

#### 2.5.2 PO

Davidson and Fraser developed a technique to performs peephole optimization via instruction selection in a retargetable mechanism [DAVI80]. This a peephole optimizer based on this technique, along with a common subexpression eliminator and a local-scope register allocator, comprise the retargetable PO optimizing compiler [DAVI84b]. The structure of the PO compiler is shown in Figure 5.

Figure 5: The structure of PO

PO was one of the first optimizing compilers to apply code improvement transformations exclusively on a low-level representation of the code. PO's front-end generates code for a high-level abstract intersection machine that provides a minimal set of computational primitives. Using an intersection machine enhances the retargetability of the compiler because it uses only a small set of operations that are likely to be available on most target machines. The code expander replaces each abstract machine instruction with a sequence of target machine instructions. Register transfers represent machine code using an architecture-independent notation that allows optimization phases to perform code improvement transformations that are largely independent of the target machine.

PO's cacher phase performs local-scope, machine-independent common subexpression elimination. Because all values, including those computed in address calculations, are exposed at the machine-level and assigned to pseudo-register values that are never re-assigned, cacher detects and eliminates all local common subexpressions [DAVI84a]. The combiner phase performs instruction selection by merging adjacent register transfers into singletons and consulting a machine description to determine if some instruction on the target machine has the effect described by the combination. This process transforms the naive code produced by the code expander into code sequences that fully utilize the instruction set and the addressing modes provided by the target machine. Before converting the resulting register transfers to assembly language code, a local register assigner is used to map pseudo-registers to appropriate target machine registers.

Although its lack of global code improvements prevents PO from producing very high quality object code, the code produced by PO is comparable to that produced by most of the production compilers that were available at the time it was developed. Unlike these contemporaneous systems, however, PO can be targeted to a new architecture is as little as three days. These results suggest that reasonable code quality can be obtained by performing even a few simple code improvements at the machine level, and that it is possible to structure such a system so that it is highly retargetable.

#### 2.5.3 HP Precision Architecture

Shortly after the development of PO, a low-level, global-scope optimizing compiler was developed for the HP Precision Architecture [JOHN86]. One of the most notable features of this compiler is that most code improvement transformations are performed after code generation to fully exploit the processor pipeline, addressing modes and loop control instructions provided by the target architecture. The back-end of

the compiler works with several front-ends which support a variety of source languages. Each front-end provides the back-end with aliasing information in the form of a list of pointer and variable references that actually or potentially access the same memory location. The code improvement algorithms use this information to perform transformations that change the definitions and uses of memory locations without disturbing the semantics of the original code. The front-ends are expected to perform improvements like constant-folding and evaluation order determination since these are not part of the back-end's repertoire.

The fixed order in which the code improvement phases are invoked was chosen to reduce the amount of time required to perform transformations and maintain the dataflow information. Code improvements that tend to eliminate instructions or require hard-to-update dataflow information are applied as early as possible in order to reduce the amount of work performed by subsequent transformations. The back-end also provides different levels of optimization to give the user the ability to trade compilation time for code quality and to produce debuggable code.

Measurements of the compiler's effectiveness indicate that the back-end produces code that is on average 37% smaller and 46% faster than the code produced directly by the front-end code generators. This is a substantial accomplishment, considering that the front-ends already produce good code. These results suggest that performing code improvement transformations on low-level code is an effective way to produce high-quality machine code.

## 2.5.4 VPO

The experience gained from the PO compiler was used to develop *vpo* [BENI89], which differs from its predecessor the following significant areas:

- it uses a C [KERN78] front end,

- the instruction recognizer uses a yacc-produced parser [JOHN78a],

- it performs global-scope register allocation and code improvements and

- register allocation precedes most code improvements.

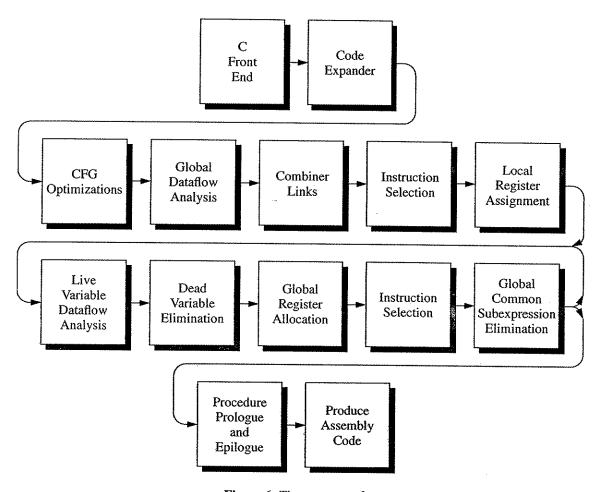

Like PO, *vpo* uses a code expander to generate naive object code in the form of register transfers (RTLs) from the abstract intersection machine code emitted by the semantic analysis phase of the front-end. The code expander defers register allocation by using pseudo-registers to hold temporary expression values. All user variables, including those declared with the **register** class, reside in memory. The back-end performs instruction selection before local-scope register assignment, which maps the pseudo-registers used to contain

temporary values to actual target-machine registers. The RTLs can be translated to assembly code at any time after the assignment phase, although a number of code improvement phases and a global-scope register allocator are usually invoked before the final translation phase, which converts the register transfers to assembly language. Figure 6 shows the structure of *vpo*.

Figure 6: The structure of vpo

The first phase of the back-end builds a control-flow graph (CFG) by partitioning the code into basic blocks [AHO86] in order to perform branch chain elimination, jump minimization and dead code elimination. Because the instruction selection phase attempts to combine logically adjacent rather that physically adjacent instructions, local and global links are inserted to connect groups of instructions that can potentially merge into a singleton. The initial instruction selection phase uses these links to reduce the length of the naive code sequences produced by the code expander by a factor of 50% or more. This has the additional desired effect of decreasing the amount of work performed by the remaining phases.

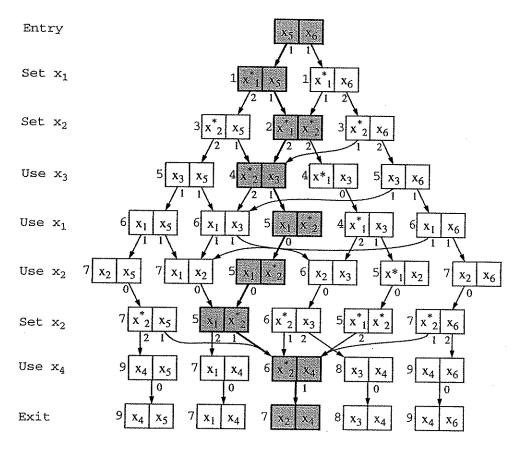

Phase iteration is used to reduce the amount of effort required to determine an optimal phase ordering for each target architecture. This strategy ensures that all of the opportunities created by each transformation to perform additional improvements are automatically exploited. Phase iteration is facilitated by the fact that all code improvement phases operate on the same representation of the code [BENI88]. Each phase indicates whether it applied transformations to the code so that *vpo* can determine which phases should be re-invoked.

The global code improvements performed by *vpo* include dead variable elimination, local variable promotion and common subexpression elimination. Local variable promotion uses a very simple algorithm that assigns a single local or argument variable to an unused register for the entire life of a function. Comparisons performed on various CISC architectures show that *vpo* is capable of generating code of equal or somewhat better quality than the production optimizing compilers on these machines. The amount of time required to retarget *vpo* depends on the complexity of the target architecture and can range from two weeks to a month.

#### 2.5.5 GCC

Like *vpo*, the GNU C compiler (*gcc*) [STAL89], performs code improvements exclusively on machine code represented using register transfers. Currently, *gcc* provides front-ends for C, C++ and Objective C and its back-end supports 23 different target architectures. Register transfers are generated from the front-end's abstract expression trees using machine-specific templates. Various local and global code improvements and register allocation are applied to the register transfers in a pre-determined order. Some of these code improvement phases may be invoked more than once if the user explicitly requests it.

Because of its performance, retargetability and availability, *gcc* is available on most UNIX systems and, in a few cases, is provided and supported by the manufacturer as the standard compiler. Despite its size<sup>1</sup>, *gcc* is relatively easy to retarget. Retargeting the system entails providing the machine-specific templates that produce register transfers from abstract syntax trees, indicate which register transfers denote valid instructions on the target machine and transform register transfers to assembly language code for the target machine. The compiler also requires a substantial number of parameters that control the code improvements

A recent version of gcc contained over 432,000 lines of code.

to be appropriately specified and, in some cases, machine-specific routines to be written in order to exploit rare or unique architectural features. While it may only take several weeks to start producing correct code for a new architecture, determining which code improvement parameter values yield the best results and writing the additional improvement routines needed to produce the desired code quality may entail several additional months. This effort includes determining the best phase ordering for the target machine. While already large, gcc continues to grow as more target architectures are added to its repertoire. This suggests that the techniques used to provide target machine information and handle unique architectural features in gcc may not be as general or as retargetable as they could be.

#### 2.5.6 Marion

Marion is a code generation system for pipelined RISC architectures that require quality instruction scheduling [BRAD91]. Marion integrates instruction scheduling, code generation and register allocation into a single phase. The instruction scheduler performs two separate instruction scheduling passes: the first to obtain schedule cost estimates and a second to produce a final schedule.

The experience with Marion indicates that integrating the scheduler, code generator and register allocator results in a system that produces code on pipelined RISC architectures that executes 12% faster than the code produced using separate components. Although this is an encouraging improvement, Marion does not support global-scope code improvements and its framework does not suggest how these improvements should be integrated. Also, despite the claim that Marion is retargetable, the emphasis on instruction scheduling over instruction selection limits its effectiveness to pipelined RISC architectures.

# 2.6 Summary

This chapter presented several compiler organization strategies along with evidence suggesting that performing code improvements exclusively at the machine-level is feasible and perhaps even desirable. The concepts introduced in this chapter that are used in the frameworks presented in Chapters 5 and 6 include:

- comprehensive code improvement suites are required to produce high-quality code,

- interactions between code improvement phases are affected by the target architecture,

- the choice of intermediate representation and the methods used to provide target architecture information to the compiler significantly affect the retargetability of the system,

- post-pass code improvements are essential to exploiting architectural nuances, and

- performing code improvements exclusively on a single representation of the code simplifies the task of re-invoking code improvement phases.

# **CHAPTER 3**

# REGISTER ALLOCATION